Введение в превосходные проекты Verilog/FPGA с открытым исходным кодом (36)-RISC-V (новый)

Несколько слов о RISC-V

Официальный сайт риска-v

❝https://riscv.org/

RISC-V (читай после меня: «риск-пять») — это архитектура набора команд с открытым исходным кодом (ISA), основанная на принципах сокращенного набора команд (RISC).

Здесь следует уточнить два понятия: спецификация набора команд (Specification) и реализация процессора (Implementation) — это два понятия разных уровней, и их следует различать. Набор инструкций (ISA) — это стандарт спецификации, который часто записывается и описывается в книге или нескольких листах бумаги, тогда как реализация процессора представляет собой исходный код, завершенный на основе спецификации набора команд. RISC-V — это спецификация набора команд.

Основываясь на наборе команд x86/ARM/RISC-V, мы можем спроектировать и реализовать микроархитектуру процессора для формирования исходного кода и, наконец, сформировать микросхему посредством записи на ленту. Спецификации набора команд и права интеллектуальной собственности, реализуемые процессором, независимы и их нельзя путать.

«RISC-V имеет открытый исходный код» означает, что спецификация набора команд является открытым исходным кодом, открытой и бесплатной (открытой и бесплатной), что существенно отличается от наборов команд x86 и ARM, но это не означает, что конкретная реализация процессора является открытой и бесплатной. также с открытым исходным кодом и бесплатно.

На основе спецификации набора команд RISC-V сообщество открытого исходного кода может либо разработать бесплатную версию реализации процессора с открытым исходным кодом (например, ядро Rocket, разработанное Беркли и т. д.), либо коммерческая компания может разработать платную авторизованную версию. реализации процессора (например, отечественный Pingtou Ge Xuantie 910, ядро Xinlai N200 и ядро USi Weihe WH-32 и т. д.).

(Источник выше: https://mp.weixin.qq.com/s/9PX5n_ZPjWM1OyqnijlIPw, авторские права принадлежат автору статьи)

Что делают отечественные производители

В настоящее время многие отечественные институты и компании занимаются соответствующей работой над архитектурой RISC-V. Xinlai и Pingtou занимаются IP. GigaDevice запустила специальную линейку продуктов GD32VF103 на основе Xinlai N200. Некоторые компании работают над Pingtou на основе IP Xinlai Brother. используется в качестве SoC, Canaan Technology выпустила его в прошлом году С выпуском K210, предназначенного для аудио и видео AI, компания Zhongke Lanxun выпустила серию чипов Bluetooth на основе архитектуры RISC-V с огромными поставками. Она утверждает, что является первой компанией в мире с более чем 100 миллионами RISC-чипов. V, и все они оснащены отечественной операционной системой IoT RT-Thread с открытым исходным кодом. Публичный аккаунт: OpenFPGA

(Ссылка на источник выше: https://www.zhihu.com/question/274106611/answer/975894883, авторские права принадлежат автору)

более полныйиз Сводный вид《Знакомство с архитектурой набора команд RISC-V и знакомство с отечественными и зарубежными производителями》。

Следующее примерно отсортировано по сложности реализации:

Добавлен 1. tinyriscv

tinyriscv

Полное описание проекта:

❝https://liangkangnan.gitee.io/2020/04/29/%E4%BB%8E%E9%9B%B6%E5%BC%80%E5%A7%8B%E5%86%99RISC-V%E5%A4%84%E7%90%86%E5%99%A8/ ❞

Реализовано одноядерное 32-битное небольшое процессорное ядро RISC-V (tinyriscv), написанное на языке verilog. Целью разработки является тестирование процессоров серии ARM Cortex-M3. tinyriscv имеет следующие возможности:

- Поддерживает набор инструкций RV32IM и проходит тест на совместимость инструкций RISC-V;

- Используется трехэтапный конвейер: выборка, декодирование и выполнение;

- Может запускать программы на языке C;

- Поддерживает JTAG и может читать и записывать память через openocd (программа онлайн-обновления);

- Поддержка прерываний;

- Автобус поддержки;

- Поддержка FreeRTOS;

- Поддержка обновления программы через последовательный порт;

- Легко портируется на любую платформу FPGA (при наличии ресурсов);

общая архитектура

❝https://gitee.com/liangkangnan/tinyriscv ❞

Подробные инструкции по дизайну на китайском языке, очень подходят для начала работы!

Добавлен 2. райдкор

❝https://github.com/ridecore/ridecore

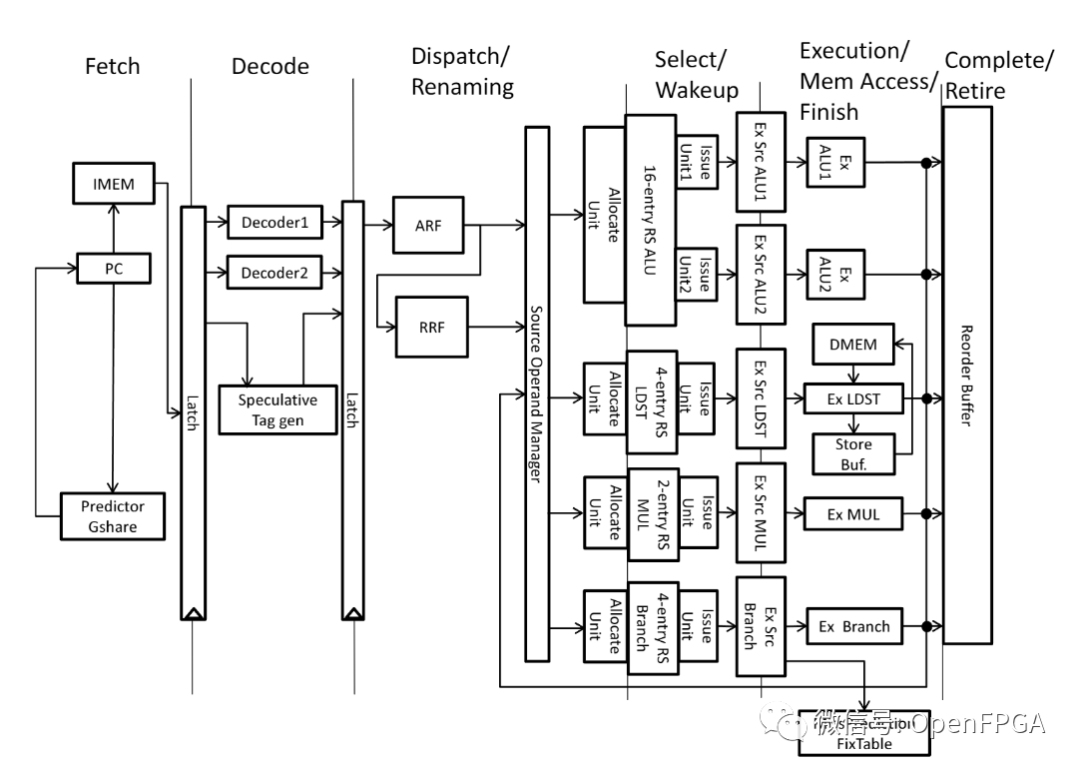

RIDECORE (RISC-v Dynamic Execution CORE) — процессор RISC-V с нарушением порядка, написанный на Verilog HDL.

RIDECORE из Микроархитектура основана на“Современный дизайн процессора:суперскалярный процессориз База”(https://www.waveland.com/browse.php?t=624&r=d|259)。поэтому,Мы рекомендуемиспользоватьсемьясуществоватьделатьиспользовать RIDECORE Прочтите эту книгу и нашу документацию, прежде чем (doc/ridecore_document.pdf)。

На данный момент прототип нашей FPGA был создан на плате Xilinx VC707. Прототип может работать на тактовой частоте 50 МГц.

Структура райдкода следующая:

Добавлен 3. nanoFOX

RISC-V, который можно «пощупать».

Небольшое ядро ЦП RISC-V, реализованное с использованием SystemVerilog. Это версия RV-CPU с AHB и кешем (полный список команд RV32I (без Fence, Fence.i, ecall, ebreak)).

nanoFOX в настоящее время работает на следующих платах FPGA:

- Storm_IV_E6_V2(Altera Cyclone IV FPGA)

- rz_easyFPGA_A2_1(Altera Cyclone IV FPGA)

- Terasic DE10-Lite(Altera MAX10 FPGA)

- Terasic DE0-Nano(Altera Cyclone IV FPGA)

Вся папка проекта организована очень четко, каждая плата имеет отдельную папку, а файлы моделирования готовы. Сборка проекта также проста, и ее стоит попробовать.

Ссылки:

- PicoRio Specification:https://gitlab.com/picorio/picorio-doc

- RISC-V Specification: https://riscv.org/technical/specifications/

- RISC-V Tools https://github.com/riscv/riscv-tools

- RISC-V GNU Toolchain:https://github.com/riscv/riscv-gnu-toolchain

Адрес проекта

❝https://github.com/Dmitriy0111/nanoFOX

1、darkriscv

Внедрите RISC-V с открытым исходным кодом с нуля за одну ночь!

Хотя код небольшой и грубый по сравнению с другими реализациями RISC-V, он очень удобен (прост) для новичков или новичков в RISC-V. Несмотря на свою простоту, DarkRISCV обладает множеством впечатляющих функций:

- Реализует большую часть набора инструкций RISC-V RV32E.

- Реализует большую часть RISC-V. RV32Iнабор команд(Недостатокcsr*、eиfence)

- Работа на частоте до 250 МГц в сверхбольшом ku040 (400 МГц с разгоном!)

- Дешевый спартан-6 до 100МГц, подойдет для небольших спартан-3Е вроде XC3S100E!

- Может поддерживать 1 такт на инструкцию большую часть времени (обычно 71% времени)

- Гибкая гарвардская архитектура (легко интегрировать контроллеры кэша, шинные мосты и т. д.)

- Хорошо работает в xilinx (spartan-3, spartan-6, spartan-7, artix-7, kintex-7 и kintex ultrascale).

- Хорошо работает с некоторыми альтернативными и решетчатыми FPGA.

- gcc 9.0.0 для RISC-V (патч не требуется!)

- Использует 850–1500LUT (ядро использует только технологию LUT6, в зависимости от включенных функций и оптимизаций)

- Дополнительная поддержка RV32E (лучше работает с FPGA LUT4)

- Дополнительные 16x16-битные инструкции MAC (для цифровой обработки сигналов)

- Дополнительная крупнозернистая многопоточность (MT)

- Никаких блокировок между этапами трубопровода нет!

- Лицензия BSD: используйте где угодно, без ограничений!

Не могу дождаться, чтобы попробовать!

❝https://github.com/darklife/darkriscv

2、picoRiscV

На самом деле, это не нуждается в представлении, это небольшой и полноценный RISC-V.

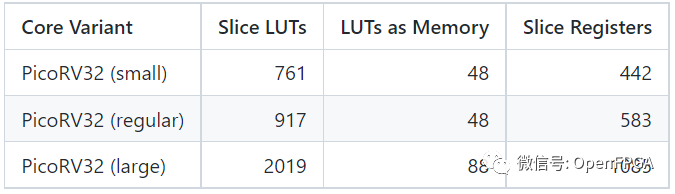

PicoRV32 — это ядро ЦП, реализующее набор инструкций RISC-V RV32IMC. Он может быть сконфигурирован как ядро RV32E, RV32I, RV32IC, RV32IM или RV32IMC и дополнительно включает встроенный контроллер прерываний.

Функции:

- Маленький (750–2000 LUT на архитектуре Xilinx 7-й серии)

- Высокая fmax (250–450 МГц на ПЛИС Xilinx 7-й серии)

- Дополнительный интерфейс собственной памяти или мастер AXI4-Lite

- Дополнительная поддержка IRQ (с использованием простой пользовательской ISA)

- Дополнительный интерфейс сопроцессора

- ЦП предназначен для использования в качестве вторичного процессора в конструкциях FPGA и ASIC. Благодаря высокому fmax его можно интегрировать в большинство существующих конструкций, не пересекая домены тактовой частоты. При работе на более низких частотах он имеет большой запас по времени и поэтому может быть добавлен в конструкцию, не влияя на замыкание времени.

❝Официальный адрес: https://bitbucket.org/casl/shakti_public.

❝https://github.com/cliffordwolf/picorv32

3、cva6

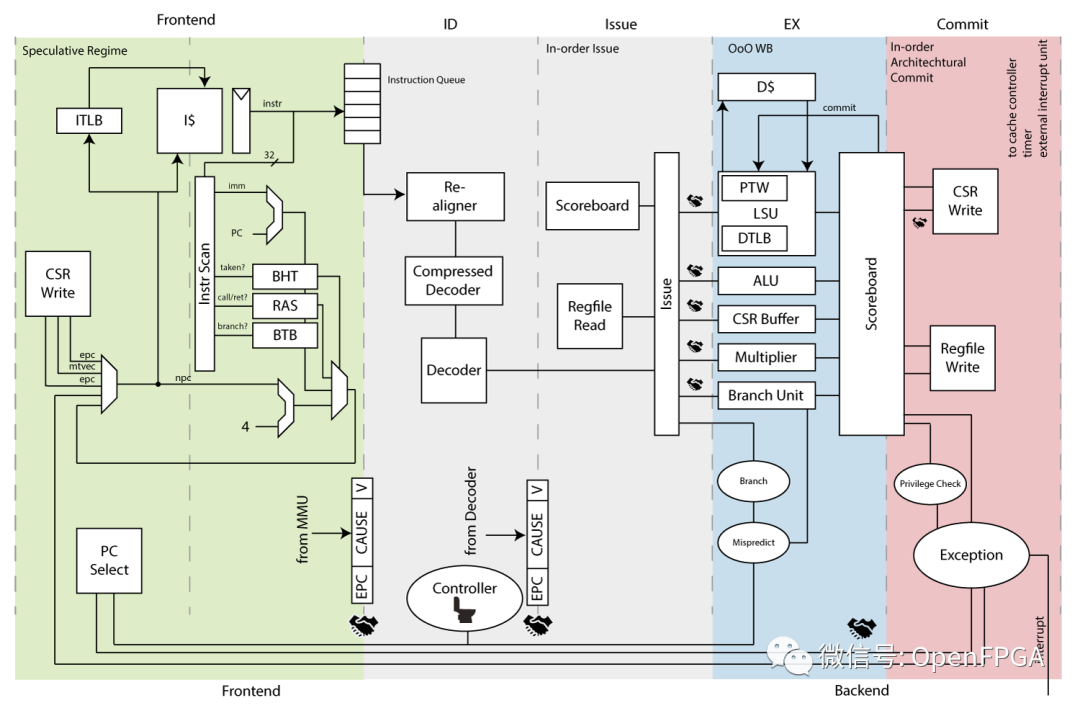

CVA6 — это 6-уровневый ЦП, реализующий 64-битный набор инструкций RISC-V. Он полностью реализует расширения I, M, A и C, как описано в Томе I: User-Level ISA V 2.3 и Privilege Extensions Draft 1.10. Он реализует три уровня разрешений M, S, U для полной поддержки Unix-подобных операционных систем. Публичный аккаунт: OpenFPGA

Он имеет настраиваемый размер, отдельный TLB, аппаратный PTW и прогнозирование ветвей (целевой буфер ветвей и таблица истории ветвей). Основная цель разработки — уменьшить длину критического пути.

❝https://github.com/openhwgroup/cva6

4、VexRiscv

Реализация RISC-V, написанная на SpinalHDL. Вот некоторые характеристики:

- Набор инструкций RV32I[M][A][F[D]][C]

- Конвейер от 2 до 5+ этапов ([Fetch*X], Декодирование, Выполнение, [Память], [Обратная запись])

- 1,44 DMIPS/Mhz --no-inline, когда включены почти все функции (1,57 DMIPS/Mhz, когда включена таблица поиска разделителя)

- Оптимизирован для FPGA и не использует IP/примитивы, специфичные для конкретного поставщика.

- AXI4、Avalon、wishbone

- Дополнительное расширение MUL/DIV

- Дополнительный FPU F32/F64 (в настоящее время требуется кэш данных)

- Дополнительный кэш инструкций и данных, общедоступная учетная запись: OpenFPGA

- Дополнительное аппаратное обновление MMU

- Дополнительные расширения отладки позволяют передавать GDB >> openOCD >> JTAG соединение в процессе Eclipse отлаживать

- Дополнительная обработка прерываний и исключений для режимов машины, [Супервизор] и [Пользователь], как определено в спецификации RISC-V Privileged ISA версии 1.10.

- Две реализации инструкций сдвига: одиночный цикл (полный цикл переключения) и циклshiftNumber.

- Каждая ступень может иметь дополнительную логику обхода или блокировки.

- Совместимость с Linux (SoC: https://github.com/enjoy-digital/linux-on-litex-vexriscv)

- Совместимость с Зефиром

- Порт FreeRTOS

Ниже представлена наибольшая частота работы и потребляемые ресурсы:

VexRiscv small (RV32I, 0.52 DMIPS/Mhz, no datapath bypass, no interrupt) ->

Artix 7 -> 243 Mhz 504 LUT 505 FF

Cyclone V -> 174 Mhz 352 ALMs

Cyclone IV -> 179 Mhz 731 LUT 494 FF

iCE40 -> 92 Mhz 1130 LC

VexRiscv small (RV32I, 0.52 DMIPS/Mhz, no datapath bypass) ->

Artix 7 -> 240 Mhz 556 LUT 566 FF

Cyclone V -> 194 Mhz 394 ALMs

Cyclone IV -> 174 Mhz 831 LUT 555 FF

iCE40 -> 85 Mhz 1292 LC

VexRiscv small and productive (RV32I, 0.82 DMIPS/Mhz) ->

Artix 7 -> 232 Mhz 816 LUT 534 FF

Cyclone V -> 155 Mhz 492 ALMs

Cyclone IV -> 155 Mhz 1,111 LUT 530 FF

iCE40 -> 63 Mhz 1596 LC

VexRiscv small and productive with I$ (RV32I, 0.70 DMIPS/Mhz, 4KB-I$) ->

Artix 7 -> 220 Mhz 730 LUT 570 FF

Cyclone V -> 142 Mhz 501 ALMs

Cyclone IV -> 150 Mhz 1,139 LUT 536 FF

iCE40 -> 66 Mhz 1680 LC

VexRiscv full no cache (RV32IM, 1.21 DMIPS/Mhz 2.30 Coremark/Mhz, single cycle barrel shifter, debug module, catch exceptions, static branch) ->

Artix 7 -> 216 Mhz 1418 LUT 949 FF

Cyclone V -> 133 Mhz 933 ALMs

Cyclone IV -> 143 Mhz 2,076 LUT 972 FF

VexRiscv full (RV32IM, 1.21 DMIPS/Mhz 2.30 Coremark/Mhz with cache trashing, 4KB-I$,4KB-D$, single cycle barrel shifter, debug module, catch exceptions, static branch) ->

Artix 7 -> 199 Mhz 1840 LUT 1158 FF

Cyclone V -> 141 Mhz 1,166 ALMs

Cyclone IV -> 131 Mhz 2,407 LUT 1,067 FF

VexRiscv full max perf (HZ*IPC) -> (RV32IM, 1.38 DMIPS/Mhz 2.57 Coremark/Mhz, 8KB-I$,8KB-D$, single cycle barrel shifter, debug module, catch exceptions, dynamic branch prediction in the fetch stage, branch and shift operations done in the Execute stage) ->

Artix 7 -> 200 Mhz 1935 LUT 1216 FF

Cyclone V -> 130 Mhz 1,166 ALMs

Cyclone IV -> 126 Mhz 2,484 LUT 1,120 FF

VexRiscv full with MMU (RV32IM, 1.24 DMIPS/Mhz 2.35 Coremark/Mhz, with cache trashing, 4KB-I$, 4KB-D$, single cycle barrel shifter, debug module, catch exceptions, dynamic branch, MMU) ->

Artix 7 -> 151 Mhz 2021 LUT 1541 FF

Cyclone V -> 124 Mhz 1,368 ALMs

Cyclone IV -> 128 Mhz 2,826 LUT 1,474 FF

VexRiscv linux balanced (RV32IMA, 1.21 DMIPS/Mhz 2.27 Coremark/Mhz, with cache trashing, 4KB-I$, 4KB-D$, single cycle barrel shifter, catch exceptions, static branch, MMU, Supervisor, Compatible with mainstream linux) ->

Artix 7 -> 180 Mhz 2883 LUT 2130 FF

Cyclone V -> 131 Mhz 1,764 ALMs

Cyclone IV -> 121 Mhz 3,608 LUT 2,082 FF

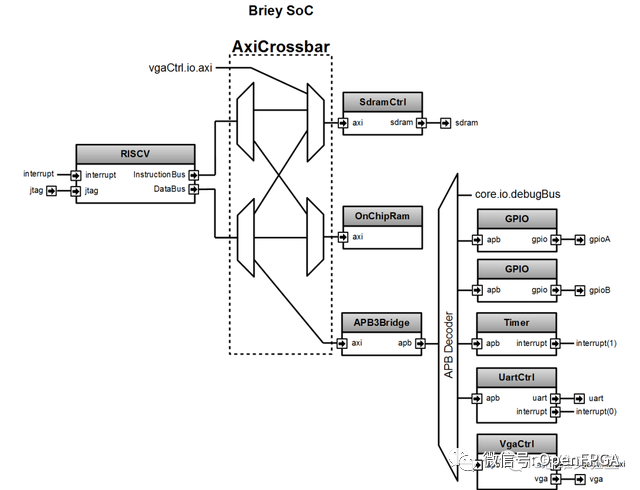

У VexRiscv есть официальная SoC: Briey, которая использует интерфейс AXI. Как и Rocket Chip, он поддерживает моделирование Verilator+OpenOCD+GDB. Как и Rocketchip, он использует инструмент sbt-интерпретатор Scala.

О спине,Можно просмотреть《От Verilog к SpinalHDL》。

❝https://github.com/SpinalHDL/VexRiscv

Все вышеперечисленные небольшие проекты подходят для понимания и начала работы с RISC-V. Самая большая особенность — это простота. Самое главное, что их можно запускать на платах для разработки FPGA, а требования к FPGA не высоки.

Далее идут еще несколько зрелых проектов.

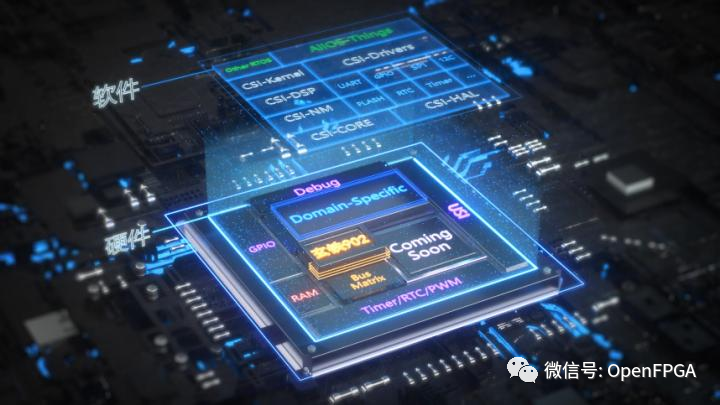

5. У брата Плоскоголового нет меча 100

Плоскоголовый брат без меча 100

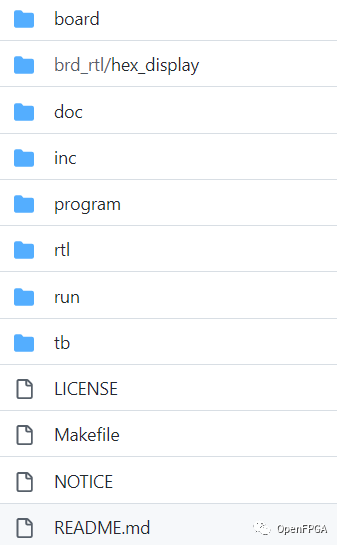

Каталог документов выглядит следующим образом:

|--Project //open source project work directory

|--riscv_toolchain //tool chain install directory download from t-head.cn

|--wujian100_open //wujian100_open project get from github

|--case //test case example for simulation

|--doc //wujian100_open user guide

|--fpga //FPGA script

|--lib //compile script for simulation

|--regress //regression result

|--sdk //software design kit

|--soc //Soc RTL source code

|--tb //test bench

|--tools //simulation script and setup file

|--workdir //simulation directory

|--LICENSE

|--README.md

❝https://github.com/T-head-Semi/wujian100_open

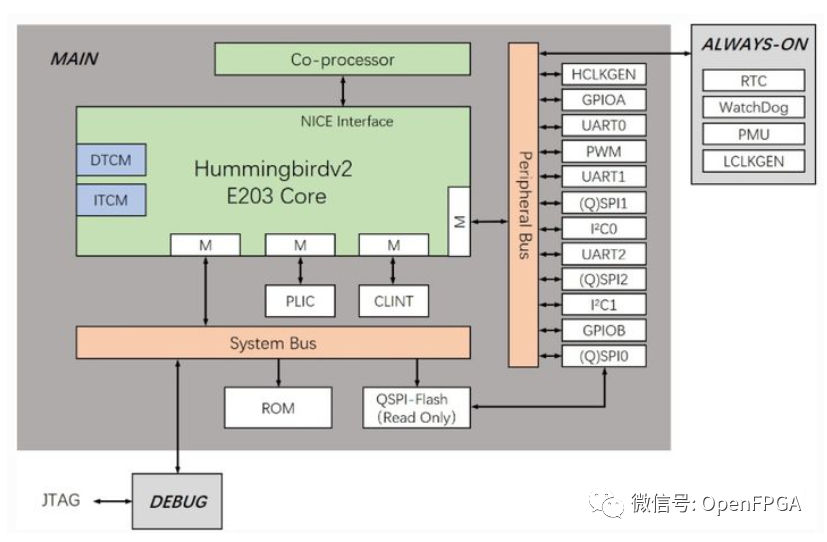

6、Hummingbirdv2 E203 Core and SoC

RISC-V, разработанный Xinlai Technology. core&SOC,даSI-RISCV/e200_opensource (https://github.com/SI-RISCV/e200_opensource) Расширенная версия.

В этом репозитории размещены проекты ядра процессора Hummingbirdv2 E203 RISC-V с открытым исходным кодом и SoC, которые разработаны и открыты для использования компанией Nuclei System Technology, ведущей компанией в области IP и решений RISC-V, базирующейся в материковом Китае. Публичный аккаунт: OpenFPGA

Это обновленная версия проекта Hummingbird E203, поддерживаемая в SI-RISCV/e200_opensource, поэтому мы называем ее Hummingbirdv2 E203.

В этой новой версии мы имеем следующие обновления.

- Добавлен NICE (расширение модуля инструкций Nuclei) для ядра E203, чтобы пользователи могли легко создавать собственные аппаратные модули с ядром E203.

- Интегрируйте периферийные устройства интерфейса APB платформы PULP (GPIO, I2C, UART, SPI, PWM) в SoC Hummingbirdv2. Эти периферийные устройства реализованы на языке Verilog для облегчения понимания пользователем.

- Добавлена поддержка новых плат разработки (Nuclei ddr200t и mcu200t) для SoC Hummingbirdv2.

Добро пожаловать на https://github.com/riscv-mcu/hbird-sdk/, чтобы использовать комплект разработки программного обеспечения Hummingbird E203.

Добро пожаловать на https://www.rvmcu.com/community.html, чтобы принять участие в обсуждении Hummingbird E203.

❝https://github.com/SI-RISCV/e200_opensource

❝https://github.com/riscv-mcu/e203_hbirdv2

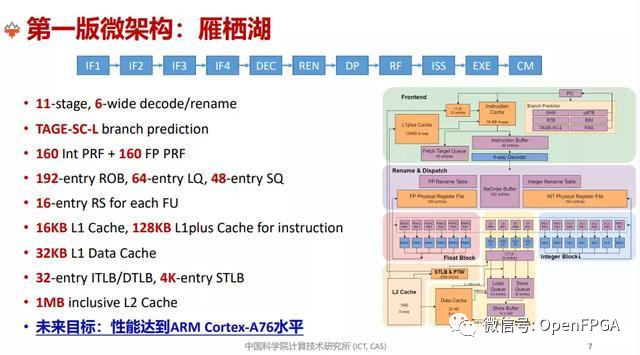

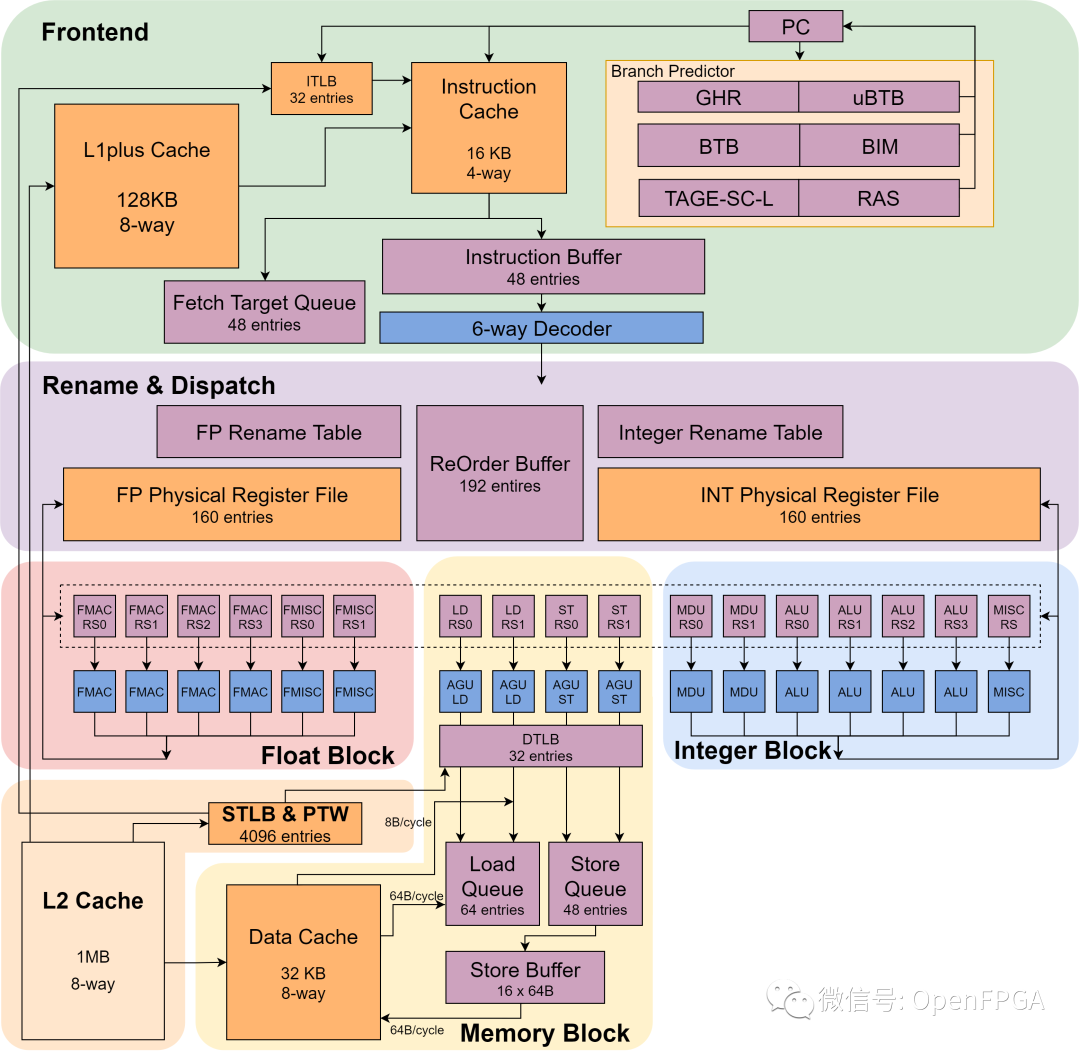

7. Высокопроизводительный процессор Xiangshan с открытым исходным кодом.

«Xiangshan» разработан на основе языка Chisel, поддерживает многоядерность, использует внеочередное выполнение, 11-уровневый конвейер и 6 запусков. Ожидается, что основная частота составит 1,3 ГГц при использовании 28-нм процесса TSMC, а основная частота — 2 ГГц при использовании 14-нм процесса SMIC. Оценка производительности составляет 7/ГГц (SEPC2006). Другими словами, первая версия архитектуры Yanqi Lake сравнивается с ARM A72/A73.

Целью архитектуры Nanhu второго поколения «Сяншань» является 10/G, а основная частота достигает 2 ГГц с использованием 14-нм процесса SMIC. По параметрам эталон архитектуры Nanhu — A76, а SPEC06 достигает 20 баллов на основной частоте 2G. Если эта цель разработки может быть достигнута, производительность центрального процессора не будет иметь аналогов среди процессоров RISC-V.

Архитектура следующая:

Домашняя страница Чжиху: https://www.zhihu.com/people/openxiangshan

Введение в долото и позвоночник «https://zhuanlan.zhihu.com/p/89249985».

❝https://github.com/OpenXiangShan/XiangShan

8. Муксинный процессор

TreeCore — это серия простых в освоении процессоров RISC-V и связанной с ними интегрированной среды разработки на основе VSCode под названием TreeCore с богатыми, подробными и интерактивными онлайн-руководствами, подходящими для начинающих. IDE на базе VSCode объединяет функции анализа кода и моделирования сигналов, а также может автоматически находить и собирать определенные цепочки инструментов, IP-ядра и зависимости библиотек от облачных серверов для разработки процессоров или приложений.

особенность:

- Полная языковая поддержка verilog, vhdl, chisel и spinalHDL.

- Современный пользовательский интерфейс

- Легкий, готовый к использованию функционал.

- Ускорение графического процессора для быстрого рендеринга в реальном времени

❝https://github.com/microdynamics-cpu/tree-core-ide

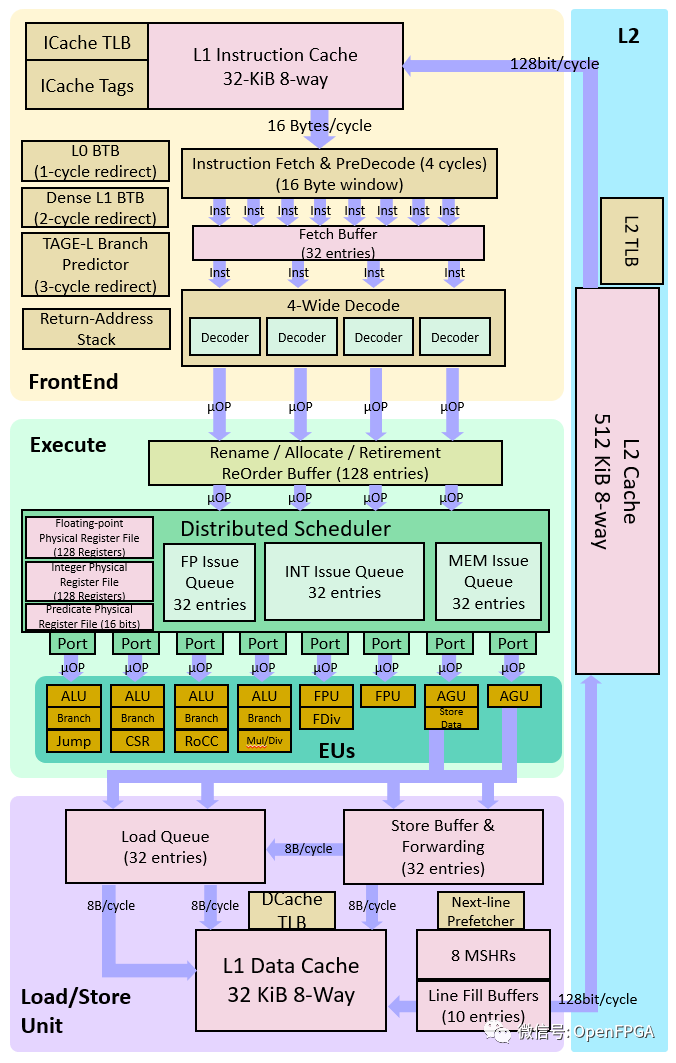

9、Rocket

(UCB) Скалярный процессор: 64Кусочек、5-этапная сборочная линия、А вот процессор выполнения последовательности запуска, оказывается:

- Поддерживает MMU и страничную виртуальную память. Может быть портирован на операционную систему Linux.

- FPU, соответствующий стандарту IEEE 754-2008

- С функцией прогнозирования ветвей он имеет BPB (усилитель прогнозирования ветвей), BHT (таблица истории ветвей), RAS (стек адресов возврата).

Rocket также написан на языке Chisel;

❝https://github.com/freechipsproject/rocket-chip

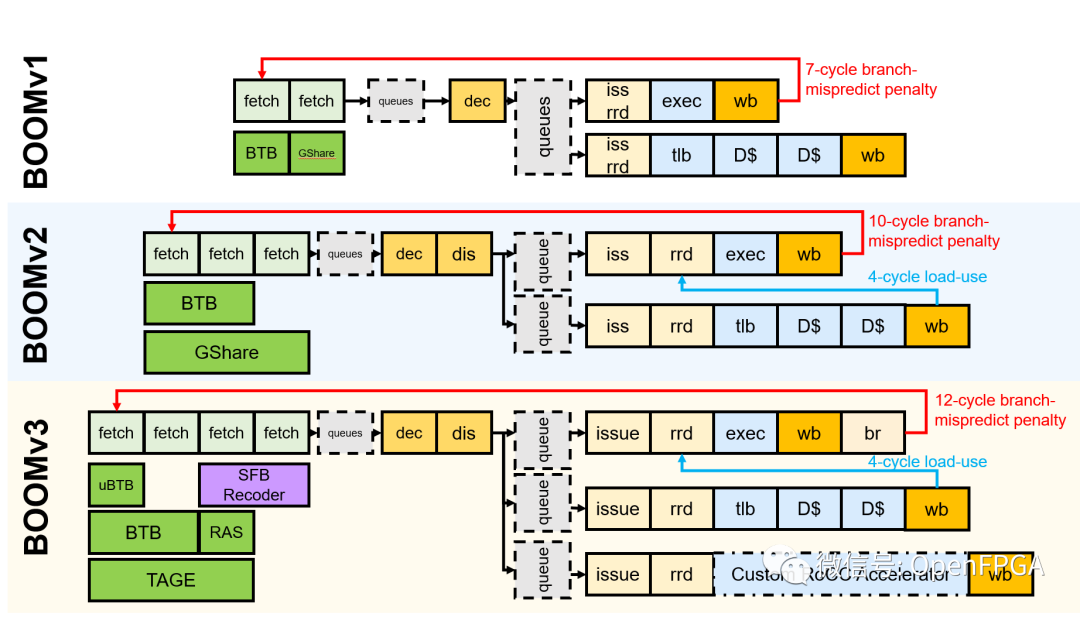

10、BOOM

(UCB) Суперскалярный процессор выполнения вне очереди;

- BOOM также написан на Chisel, а общий код составляет около 9000 строк, инструкция — RV64G;

- 6-этапный конвейер: выборка инструкций, декодирование/переименование/распределение инструкций, выдача/чтение регистра, выполнение, доступ к памяти, обратная запись.

❝https://github.com/riscv-boom/riscv-boom

11、Sodor

(UCB) 32-битный процессор с открытым исходным кодом для обучения. Написанный Chisel, он поддерживает 5 типов процессоров: однотактные процессоры, двухуровневые конвейерные процессоры, трехуровневые конвейерные процессоры, пятиуровневые конвейерные процессоры и процессоры, исполняемые микрокодом. Публичный аккаунт: OpenFPGA

Первые процессоры для учебных целей были написаны на языке Chisel и не имели практической коммерческой ценности. Он давно не обновлялся.

Структура относительно понятна, например описание различной глубины PipeLine (1-го, 2-го, 3-го и 5-го порядка соответственно); ее можно использовать в качестве хорошего демонстрационного кода;

❝https://github.com/ucb-bar/riscv-sodor

12、YARVI

VARVI — это простой 32-битный процессор с открытым исходным кодом, разработанный и выпущенный энтузиастом RISC-V Томми Торном. Он реализует RV32I и использует Verilog. Цель — четко и точно реализовать RV32I.

❝https://github.com/tommythorn/yarvi

13、Pulpino

Разработано совместно ETH Zurich и Болонским университетом, Италия. 32-битный, набор инструкций: RV32I/RV32C/RV32M, расширенные многоядерные инструкции RISC-V;

❝Веб-сайт: https://www.pulp-platform.org/.

❝https://github.com/pulp-platform/pulpino

14、GRVI Phalanx

Массовый параллельный RISC-V (до 1000 ядер), 2-3-ступенчатый конвейер, 32-битный, из которых 32 процессора RISC-V реализованы на плате разработки Artix-7 35T, 80 ядер реализованы на PYNQ-; Z1 реализован 1680-ядерный RISC-V на UltraScale; исходный код не является открытым;

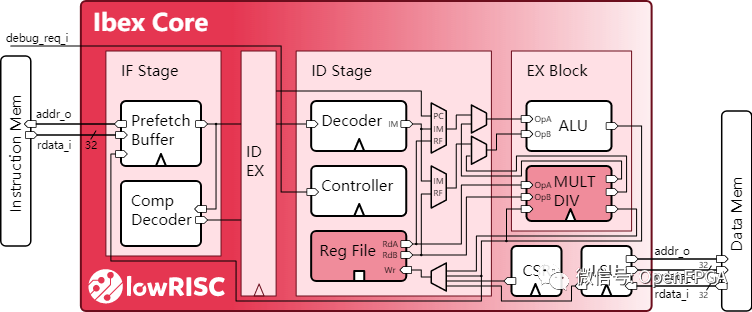

15、Ibex

Говоря о RISC-V с открытым исходным кодом, мы не можем не упомянуть серию Riscy, особенно RISC-V, которая широко используется. Ibex — это ядро, созданное на основе нулевого риска, поддерживающее RV32IMC и некоторые инструкции серии Z и поддерживаемое LowRISC. Ibex небольшой и компактный, с подробной документацией и богатыми учебными материалами. Он поддерживает verilator. Вы можете использовать verilator+openOCD+GDB для отладки во время моделирования. Это очень удобно для тех, кто сильно зависит от Verilator, таких как я.

Ibex поддерживает два режима привилегий: машинный режим и пользовательский режим, которые позволяют реализовать более широкие функции, чем один машинный режим. Ibex разработан с использованием системы verilog, что является хорошей новостью для традиционных инженеров ИС. Ibex теперь также поддерживает кэш инструкций, что повышает производительность, но установка кэша сильно раздует ядро, что полезно для изучения конструкции контроллера кэша.

Ibex использует собственный интерфейс, такой как TLUL, а официальный SoC — PULP. Проект Google OpenTitan также основан на Ibex. Существует довольно много соответствующих учебных материалов по дизайну.

❝https://github.com/lowRISC/ibex

❝Документация: https://ibex-core.readthedocs.io/en/latest/introduction.html.

16、SweRV EH1

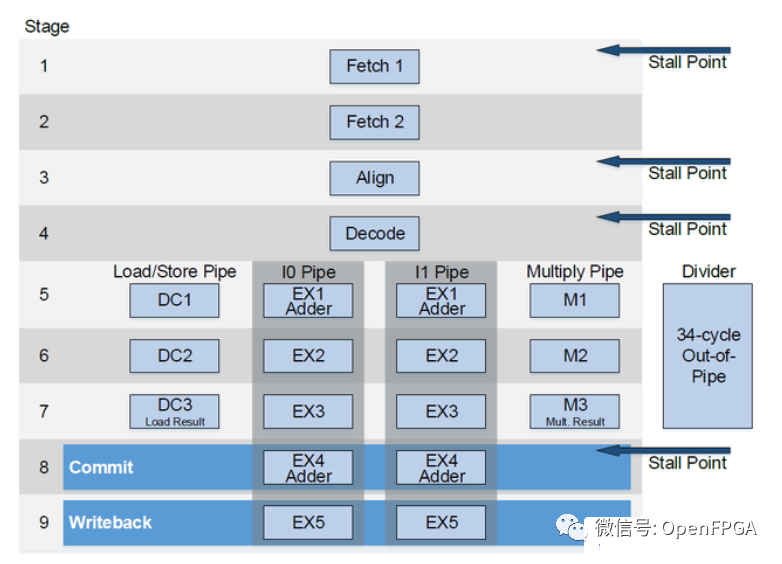

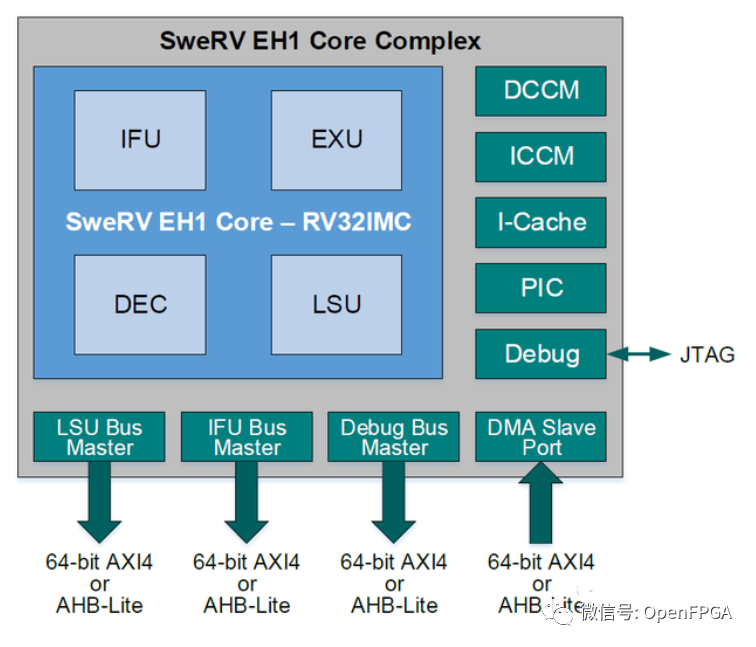

SweRV EH1 — одно из ядер RISC-V, разработанное WD. Оно поддерживает RV32IMC, двойной запуск, однопоточный и 9-уровневый конвейер. Производительность, как следует сказать, довольно хорошая. Он может работать на частоте 1 ГГц при 28 нм. Также имеется подробный документ, достойный выпуска крупного производителя.

SweRV разработан с использованием Verilog/System Verilog и использует интерфейс AXI. Он весьма удобен для студентов, знакомых с AMBA и не желающих изучать Chisel и Scala. И поддержите верилятор, вам должно понравиться. Стоит отметить, что SweRV имеет кеш инструкций и реализует множество пользовательских инструкций по обслуживанию кеша, которые очень стоит изучить.

❝https://github.com/chipsalliance/Cores-SweRV

Шедевр для продвинутого обучения, произведенный крупным производителем.

17、picorio

Официально произведено.

Международная лаборатория открытого исходного кода RISC-V (RIOS: RISC-V International Open Source Lab), возглавляемая лауреатом премии Тьюринга 2017 года профессором Дэвидом Паттерсоном, выпустила первый в мире RISC с полностью открытым исходным кодом, который может работать под управлением Linux. Проект микрокомпьютерной системы V PicoRio используется для создать более прозрачную, маломощную и легко настраиваемую высокопроизводительную платформу периферийных вычислений. Самая большая особенность PicoRio заключается в том, что все, от конструкции процессора до конструкции печатной платы и основного программного обеспечения операционной системы, имеет открытый исходный код. Базовая архитектура использует новейшую технологию набора команд RISC-V с открытым исходным кодом. В дополнение к высококачественной интеллектуальной собственности промышленного уровня с открытым исходным кодом PicoRio также предоставит эталонные проекты SoC с открытым исходным кодом и подробную документацию по интеграции. PicoRio основан на процессоре с открытым исходным кодом и поддерживается многими IP-адресами. Что касается программного обеспечения, PicoRio разработала общую архитектуру программного обеспечения с богатой операционной средой и поддержкой других программ, поэтому у нее мощная программная экосистема. Выпуск PicoRio знаменует собой переход лаборатории RIOS в стадию реального производства. После этого RIOS Lab будет стремиться создать более открытый исходный код, более низкое энергопотребление и более безопасную экосистему программного и аппаратного обеспечения в рамках экосистемы RISC-V и будет отвечать за поддержку всей аппаратной системы и архитектуры программного обеспечения PicoRio.

Проект PicoRio охватывает портирование платформы RISC-V и поддержку ядра Chromium OS и механизма JavaScript V8. Может запускать полные системы Linux и FreeRTOS. В 2021 году проект PicoRio завершит разработку и проверку чипа уровня ARM A75, который будет использоваться в планшетах/ноутбуках RISC-V, где все прикладное программное обеспечение и хранилище работают в облаке (аналогично Chromebook).

Ссылки:

- PicoRio Specification:https://gitlab.com/picorio/picorio-doc

- RISC-V Specification: https://riscv.org/technical/specifications/

- RISC-V Tools https://github.com/riscv/riscv-tools

- RISC-V GNU Toolchain:https://github.com/riscv/riscv-gnu-toolchain

Адрес проекта

❝https://rioslab.org

Эта статья изначально создана автором OpenFPGA и не может быть воспроизведена без моего разрешения!Этап завершен!

NOWДействуйте сейчас!

Наилучшая информация для изучения Xilinx FPGA — это официальное руководство. В следующей таблице обобщено основное вводное содержание некоторых руководств. Следуйте за мной, и оно будет постоянно обновляться...

имя файла | основное название | Краткое введение в содержание | Есть ли китайская версия? | |

|---|---|---|---|---|

UG476 | 7 Series FPGAs GTX/GTH Transceivers | Введение в GTX и GTH, необходимое для изучения PCIe, serdes и т. д. | нет | |

UG471 | 7 Series FPGAs SelectIO Resources | Описывает ресурсы SelectIO, доступные в ПЛИС 7-й серии. | нет | |

UG1114 | PetaLinux Tools Documentaton | Справочное руководство документации PetaLinux Tools | Да, версия 2019.2. | |

UG949 | Руководство по методологии проектирования UltraFAST для Vivado Design Suite | Методология проектирования Xilinx® UltraFast™ представляет собой набор передовых методов оптимизации процесса проектирования современных устройств. Масштаб и сложность этих проектов требуют определенных шагов и задач проектирования, чтобы обеспечить успех на каждом этапе проектирования. Следование этим шагам и передовому опыту поможет вам достичь желаемых целей проектирования максимально быстро и эффективно. | Да, версия 2018.1 | |

Руководство по IP | pg057 | FIFO Generator | Руководство пользователя генератора FIFO IP | нет |

pg104 | Complex Multiplier | Руководство пользователя комплексного множителя IP | нет | |

pg122 | RAM-Based Shift Register | Руководство пользователя сдвигового регистра IP | нет |

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

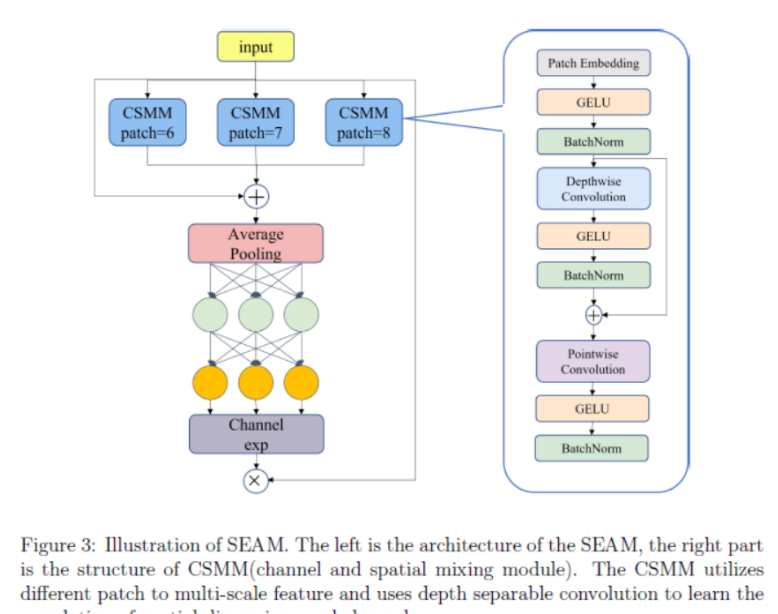

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

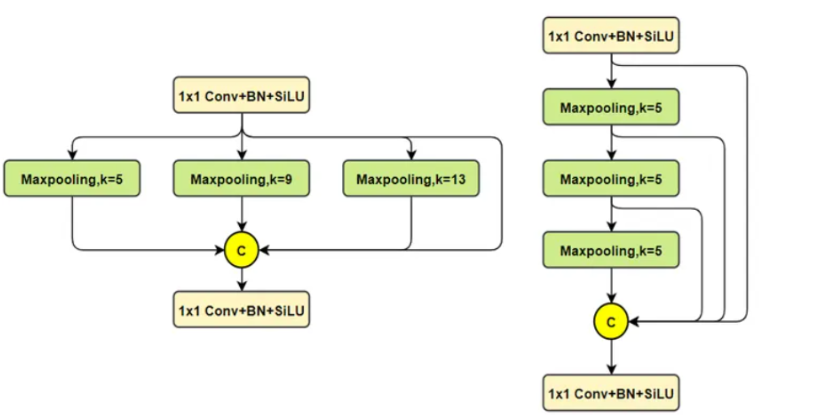

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

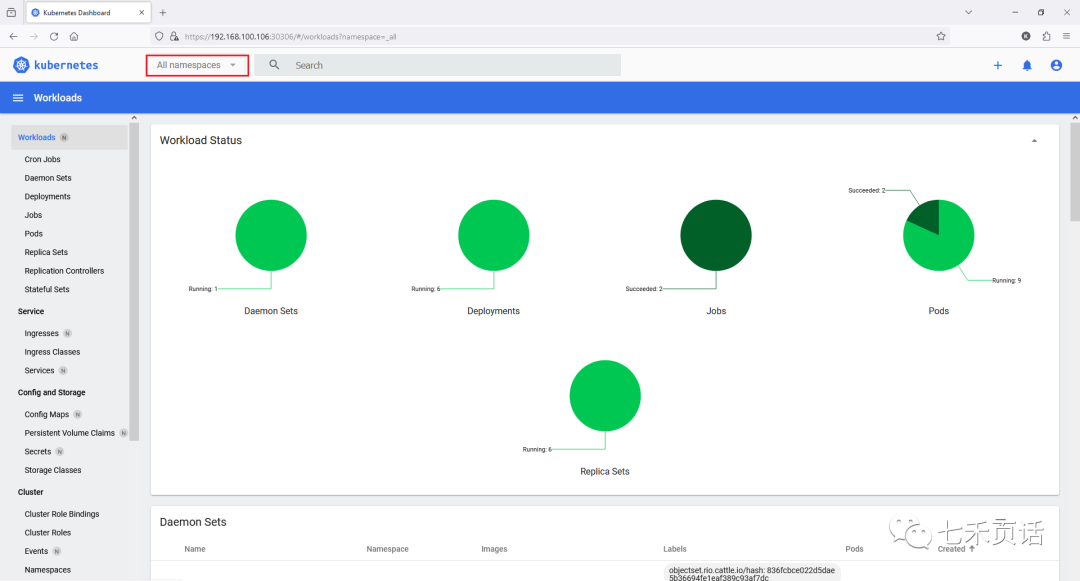

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

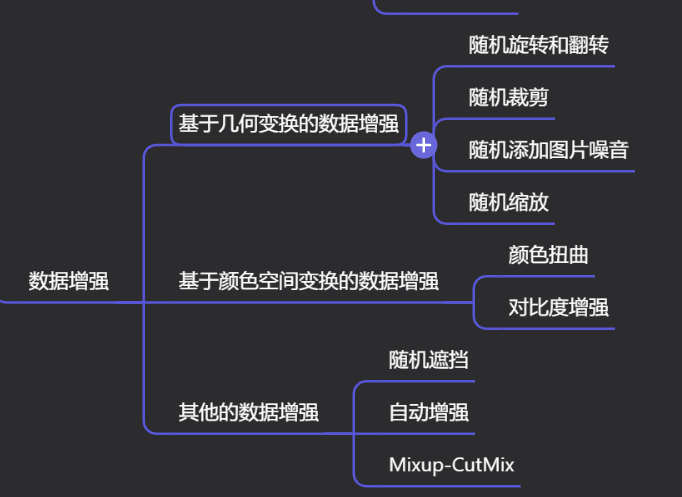

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

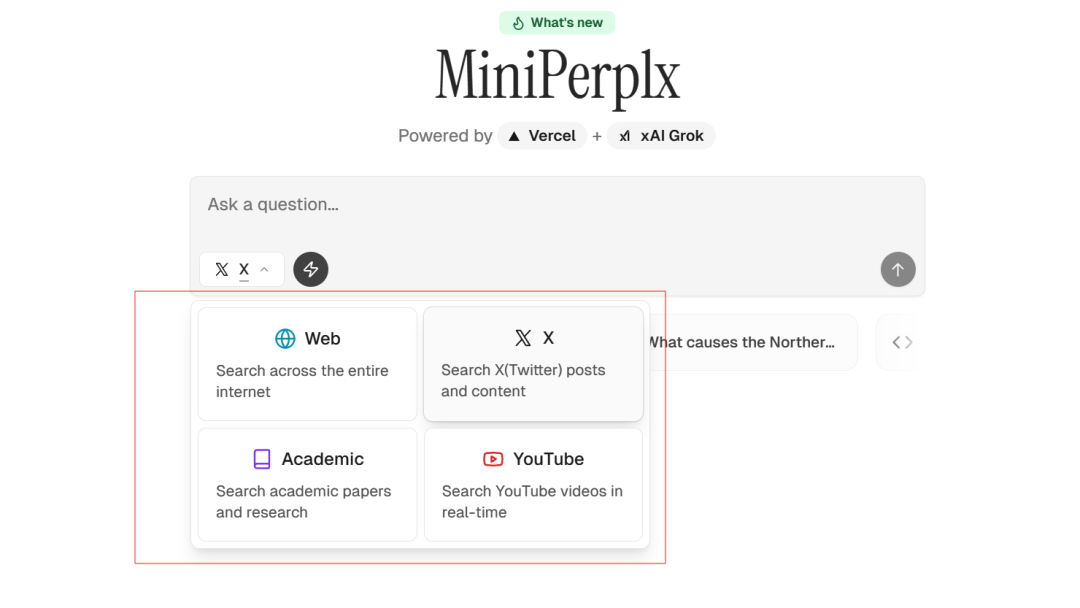

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

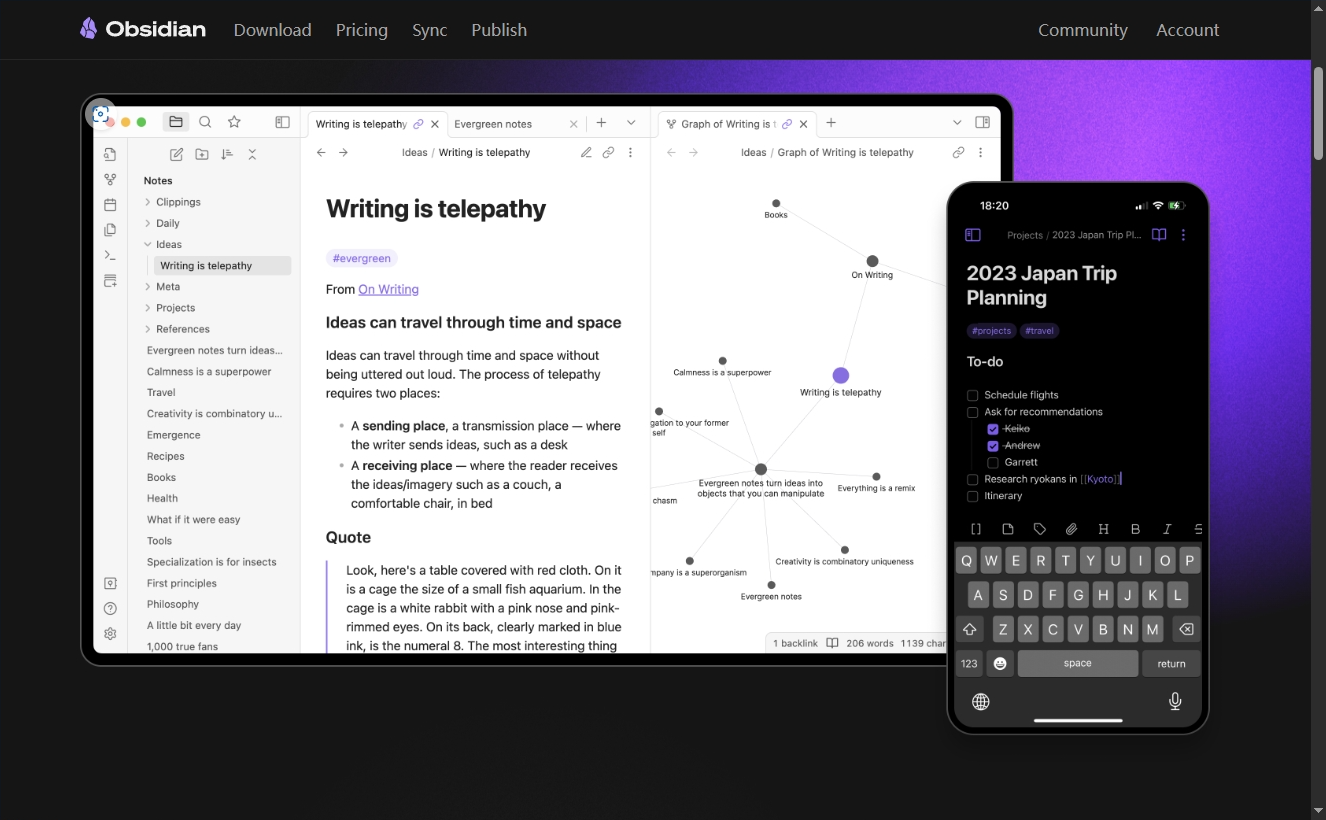

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

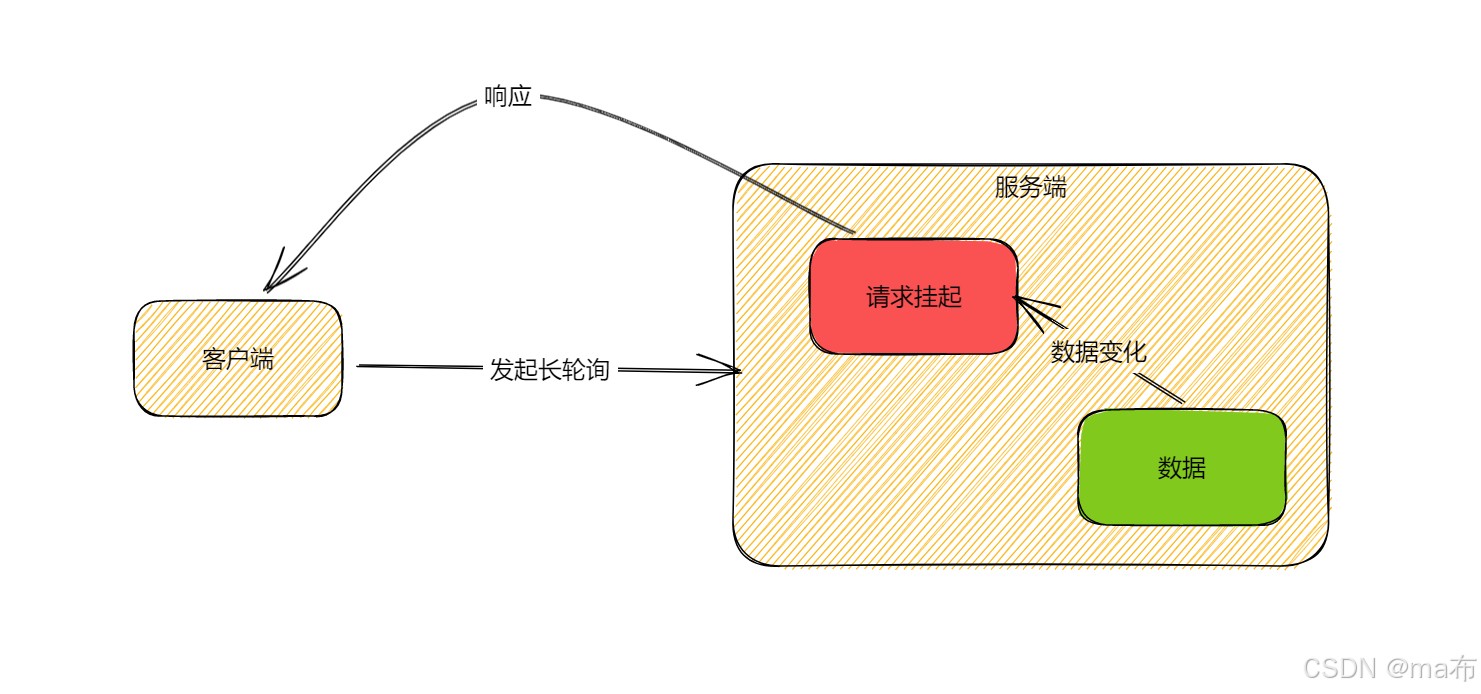

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

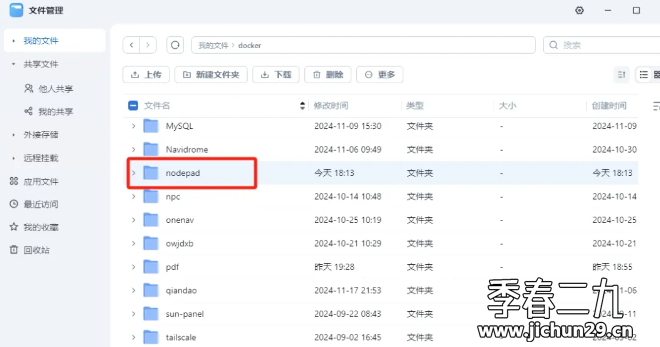

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

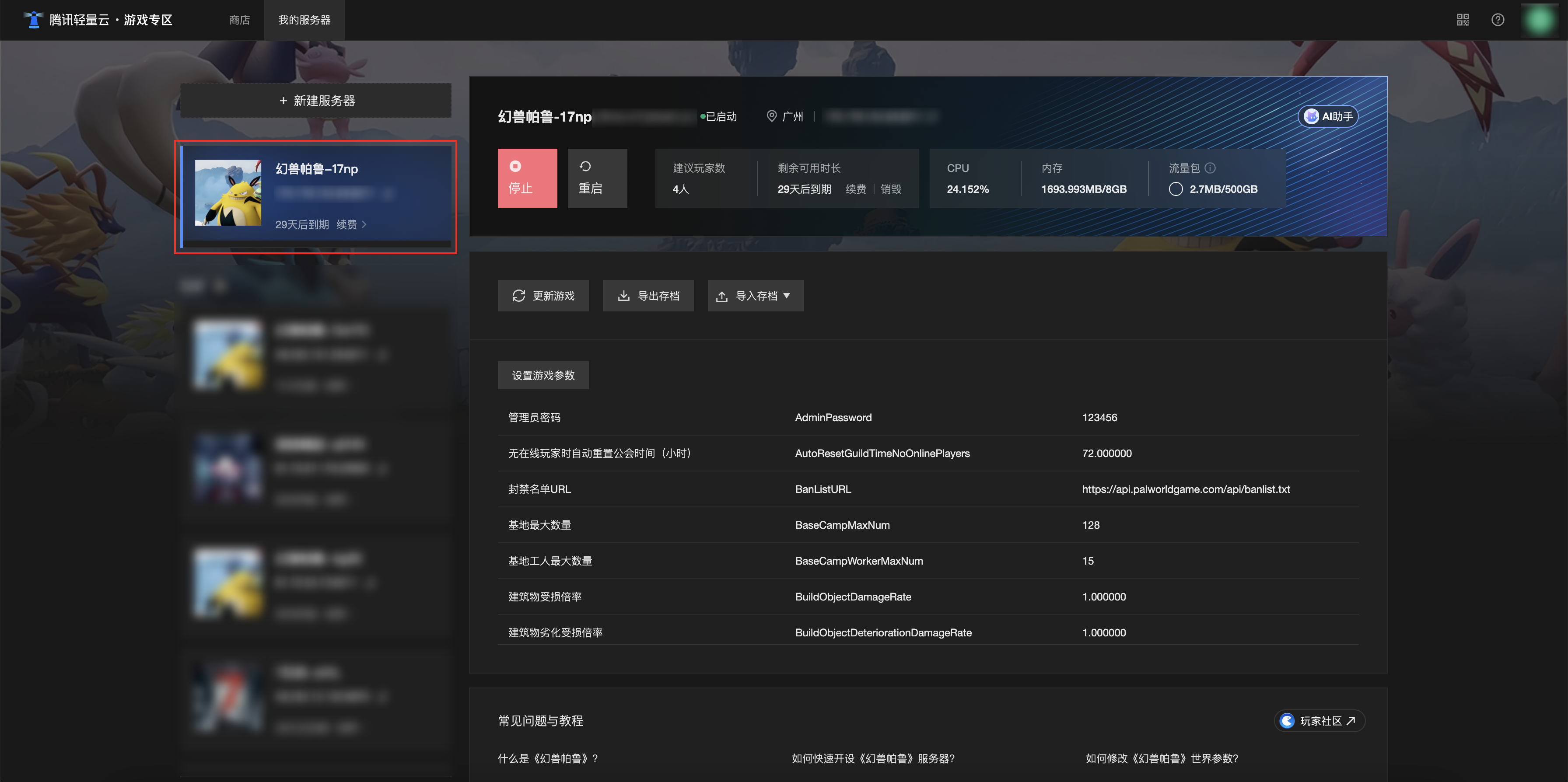

[Зона легкого облачного игрового сервера] Управление игровыми архивами