Углубленное понимание архитектуры MIPS 1-Введение в системы архитектуры MIPS и RISC.

Среди многих архитектур с сокращенным набором команд RISC архитектура MIPS является наиболее элегантным «танцором». Даже ее конкуренты впечатлены ее мощным влиянием. Это затронуло набор инструкций DEC Alpha (сейчас заброшенный) и HP Precision. Хотя элегантности недостаточно, чтобы сделать его неуязвимым на жестоком рынке, архитектура MIPS по-прежнему использует простейшую конструкцию, чтобы обеспечить самую высокую эффективность выполнения среди всех поколений архитектуры ЦП.

В результате инкубации академического проекта для коммерциализации архитектуры MIPS необходима простая архитектура. У компании небольшая команда дизайнеров, оставляющая производство и коммерциализацию своим партнерам по полупроводникам. В результате у нее имеется широкий круг совместных производителей полупроводниковой промышленности: LSI Logic, LSI, Toshiba, Philips, NEC и IDT являются ее партнерами. Стоит отметить, что отечественная компания Loongson выкупила свою архитектуру набора команд и стала лидером в локализации чипов.

В области процессоров начального уровня архитектура MIPS недолговечна. В настоящее время он в основном используется во встраиваемых системах, таких как маршрутизаторы, и занимает почти большую часть рынка.

ЦП с архитектурой MIPS является одним из ЦП с сокращенным набором инструкций RISC и появился в самый активный период академических исследований RISC. Аббревиатура RISC (компьютер с сокращенным набором команд) является меткой TAG для всех новых архитектур ЦП, появившихся в период с 1986 по 1989 год. Она содержит инновационные идеи для этих недавно появившихся высокопроизводительных архитектур. Кто-то ярко сказал: «RISC — это основа всех компьютерных архитектур, родившихся после 1984 года». Хотя это небольшое преувеличение, это также неоспоримый факт. Никто не может игнорировать вклад, внесенный пионерами сокращенного набора команд RISC.

Наиболее важным вкладом в область MIPS является проект MIPS в Стэнфордском университете. Почему он называется MIPS?,то есть может представлятьmicrocomputer without interlocked pipeline stages-Нет блокировкисборочная Английское значение слова microprocessor для линии,также может представлятьmillions of instructions per secondЧто значит выполнять один миллион инструкций в секунду?,Какой каламбур. Кажется,MIPSОсновным направлением исследований архитектуры по-прежнему остаетсяCPUизсборочная линия архитектуры, как заставить ее работать более эффективно. Далее начнем со сборочной линия начала говорить.

Блокировка конвейера является одним из ключевых факторов, влияющих на эффективность выполнения инструкций ЦП.

1.1 Трубопровод

Предположим, есть ресторан, назовем его «Evie's Fish and Chip Shop». В нем каждый клиент выстраивается в очередь за едой (жареная треска, картофельные чипсы, гороховое пюре, чашка чая). После того, как официант накрывает тарелку, клиент находит столик и садится есть. Это наш обычный способ обедать в ресторанах.

Картофель фри от Иви — лучшая местная закуска. Поэтому, когда рынок большой, длинная очередь выходит за пределы магазина. Итак, когда соседний магазин сабо закрылся, Иви взяла на себя управление, расширила магазин и добавила столы. Однако это все равно не помогает. Потому что занятым гражданам некогда сесть и выпить чашечку чая. (Поскольку Иви еще не нашла причину длинной очереди…)

Жареная треска Иви и картофель фри Берта — визитные карточки магазина, и приходящие сюда покупатели будут заказывать именно эти два блюда. Но у них только одна стойка, поэтому, когда клиент заказывает чашку чая и оказывается позади покупателя, заказывающего треску с жареным картофелем, ему приходится ждать... Наконец однажды Иви пришла в голову блестящая идея: они расширили стойку, и четыре клерка, Иви, Берт, Дионис и Мэри, выстраивались в ряд, когда приходил покупатель, Иви отвечала за то, чтобы положить треску на тарелку; Берт добавил картошку фри, а Дионис наполнил тарелку гороховым пюре, Мэри налила чай и оплатила счет. Таким образом можно одновременно обслуживать четырех клиентов. Какая гениальная идея.

Длинных очередей больше нет, а выручка магазина Иви выросла…

Это конвейер, который делит повторяющуюся работу на несколько частей и каждый человек отвечает за одну из них. Хотя общее время обслуживания каждого клиента увеличивается, одновременно обслуживаются четыре клиента, что повышает общую эффективность приема пищи и оплаты счетов. На рис. 1-1 ниже представлена схема структуры сборочной линии в магазине Иви.

Итак, если мы разложим выполнение инструкции ЦП на пять этапов: выборка инструкций, декодирование, поиск операндов, выполнение операций и сохранение результатов, будет ли это очень похоже на сборочную линию в магазине Иви выше? По сути, программа, ожидающая выполнения, представляет собой очередь инструкций, ожидающих, пока процессор выполнит их одну за другой.

Конвейер, конечно, не является новым изобретением набора команд RSIC. Комплексный набор команд CSIC также использует конструкцию конвейера. Разница в том, что RSIC перепроектирует набор команд, чтобы сделать конвейер более эффективным. Так каковы же ключевые факторы, ограничивающие эффективность сборочной линии?

1.1.1 Факторы, ограничивающие эффективность сборочной линии

Все мы знаем знаменитый «эффект бочки»: количество воды в бочке определяет самый короткий кусок дерева, а не самый длинный. Аналогично, если мы обеспечим, чтобы каждый шаг выполнения инструкций занимал одинаковое время, тогда этот конвейер будет совершенно эффективным. Но реальность зачастую жестока. Рабочая частота процессора намного превышает рабочую частоту чтения и записи памяти (оба не одного порядка).

Вернемся в магазин Иви. Клиент Сирил — бедный человек, которому часто не хватает денег, поэтому Иви не будет его обслуживать, пока Мэри не получит его деньги. Итак, теперь Сирил застрял в положении Иви. Иви не будет продолжать обслуживать его, пока Мэри не обработает первых трех клиентов и не оплатит за него счет. Таким образом, на этом конвейере по сбору продуктов питания Сирил является нарушителем спокойствия, потому что ему нужен ресурс, который используют другие (Мэри проверяет). (В этом случае шина блокировки может использоваться для обеспечения эксклюзивного доступа к памяти, соответствующей инструкции хранения ЦП.)

Иногда Дафна и Лола покупают порцию еды и делятся ею друг с другом. Например, то, купит ли Лола картофель фри, зависит от того, купит ли Дафна чашку чая. Потому что, если бы она просто съела картошку фри, не запивая, Дафна могла бы подавиться или споткнуться. Затем Лола будет с нетерпением ждать, пока Дафна купит чашку чая у Мэри, продавца Берта, и возникнет разрыв во времени, который мы называем разрывом на конвейере. (Очень ли это похоже на условное ветвление?)

Конечно, не все зависимости плохи. Предположим, есть покупатель Фрэнк, который всегда подражает Фреду в заказе еды. Возможно, Фрэнк — фанат Фреда. Фактически это подразумевает основу для повышения эффективности доступа к памяти и прогнозирования ветвлений посредством обращений к кэшу.

Конечно, вы думаете, а не была бы суперэффективная сборочная линия для устранения этих проблемных клиентов? Однако здесь до сих пор живет Иви, как она может обижать клиентов. Intel, лидер отрасли по производству компьютерных процессоров, также сталкивается с этой проблемой: невозможно быть несовместимым с предыдущим программным обеспечением. Если она полностью начнет с нуля и построит новую архитектуру, она может потерять многих клиентов. Поэтому нам остается только латать старую структуру еще лет десять. Это также дает прекрасную возможность для разработки набора команд RSIC.

1.1.2 Конвейер и кэш

Согласование скорости обработки процессора компьютера и скорости чтения памяти является ключом к повышению эффективности работы процессора, что является недостатком «эффекта бочонка». Итак, чтобы ускорить доступ к памяти, в конструкцию ЦП был введен Cache. Так называемый Кэш — это небольшая высокоскоростная память, используемая для копирования фрагмента данных в память. Наименьшая единица данных в кэше — это строка, каждая строка соответствует небольшому адресу памяти (обычный размер строки — 64 байта). Каждая строка содержит не только данные, считанные из основной памяти, но также информацию об ее адресе (TAG) и информацию о состоянии. Когда ЦП хочет получить доступ к данным в памяти, блок управления памятью сначала ищет в кэше. Если данные существуют, они немедленно возвращаются в ЦП. Это называется попаданием в кэш; если они не существуют, это называется попаданием в кэш. В это время блок управления выполняет поиск соответствующих данных в основной памяти, возвращает их в ЦП и оставляет резервную копию в кэше. Конечно, Кэш не знает, какие данные нужны ЦП в следующий раз, поэтому он может хранить только те данные, которые ЦП недавно использовал. Если необходимы вновь скопированные данные основной памяти, она выберет соответствующие данные для удаления, что включает в себя алгоритм стратегии замены кэша.

Кэш может предоставлять данные, необходимые ЦП, примерно в 90% случаев, тем самым значительно увеличивая скорость, с которой ЦП считывает данные, и тем самым повышая эффективность конвейера.

Поскольку инструкции отличаются от данных и имеют атрибуты только для чтения, архитектура MIPS использует Гарвардскую структуру для разделения кэша данных и кэша инструкций. Таким образом, инструкции и переменные можно читать и записывать одновременно.

1.2 Архитектура MIPS, 5-этапный конвейер

Рисунок 1.2: Конвейер этапов MIPS-5

MIPS сама по себе представляет собой архитектуру, основанную на проектировании конвейерной оптимизации. Поэтому инструкции MIPS разделены на 5 этапов. Каждый этап занимает фиксированное время. Здесь фиксированное время фактически представляет собой такт процессора (две инструкции занимают половину такта). таким образом, 5-этапный конвейер MIPS фактически занимает 4 такта).

Все инструкции строго соответствуют каждому этапу конвейера, даже если на определенном этапе ничего не происходит. В результате, пока кэш попадает в кэш, ЦП будет запускать инструкцию каждый такт.

Давайте посмотрим, что делает каждый этап:

- Выборка-ЕСЛИ Получите инструкции для выполнения из I-Cache.

- Читать Регистр-РД Получите значение в регистре ЦП.

- Арифметические и логические операции-АЛУ Выполняйте арифметические или логические операции. (Операции с плавающей запятой, операции умножения и деления не могут быть выполнены за один такт. В будущем мы напишем статью специально, чтобы объяснить знания, связанные с FPU)

- Чтение и запись памяти-MEM То есть чтение и запись D-Cache. Что касается того, почему говорят, что кэш данных читает и записывает,Это потому, что скорость чтения и записи памяти слишком низкая.,Невозможно удовлетворить потребности ЦП. Так вот есть высокоскоростной кэш типа D-Cache. Но даже в этом случае,Во время чтения и записи D-Cache,В среднем 3 из каждых 4 инструкций ничего не делают. но,На этом этапе каждая инструкция должна иметь монопольный доступ к шине данных.,В противном случае это приведет к конфликтам доступа к D-Cache. Вот почему существуют барьеры памяти и защелки шины.

- Регистрация обратной записи-обратная запись Запишите результат в регистр.

Конечно, приведенный выше конвейер — всего лишь теоретическая модель. Но на самом деле некоторые процессоры с архитектурой MIPS имеют более длинные конвейеры или другие различия. Однако пятиуровневая конвейерная архитектура действительно является отправной точкой и основой всего этого.

Строгие правила конвейера ограничивают возможности инструкций.

Во-первых, все инструкции имеют одинаковую длину (32 бита) и инструкции чтения занимают одинаковое время. Это снижает сложность конвейера; например, в инструкции недостаточно битов для кодирования сложных шаблонов адресации.

Конечно, у этого ограничения есть и недостатки: средняя длина инструкции программы на архитектуре X86 составляет всего около 3 байт. Следовательно, архитектура MIPS занимает больше места в памяти.

Во-вторых, конвейерная конструкция архитектуры MIPS исключает реализацию инструкций, выполняющих какие-либо операции с переменными памяти. Сбор данных из памяти возможен только на этапе 4, который немного задерживается для арифметико-логического устройства. Доступ к памяти может быть осуществлен только с помощью инструкций загрузки или сохранения. (Сборка архитектуры MIPS также является одним из самых простых и понятных кодов)

Несмотря на эти проблемы, разработчики архитектуры MIPS также думают о том, как сделать ЦП более простым и эффективным, оптимизируемым компилятором. Требования эффективной оптимизации некоторых компиляторов совместимы с требованиями проектирования конвейера, поэтому ЦП архитектуры MIPS имеет 32 регистра общего назначения и использует арифметические/логические инструкции с тремя операндами. Эти сложные инструкции специального назначения также не желают генерироваться компилятором. С точки зрения непрофессионала, компилятор может обойтись без сложных инструкций.

1.3 Сравнение RISC и CISC

Как отличить разницу в определении наборов инструкций RISC и CISC? По моему мнению, RISC — это описание взаимосвязи между архитектурой и набором команд. В середине 1980-х годов появился ряд новых архитектур, в которых наборы команд умело использовались для максимизации эффективности этих конвейерных архитектур. Эти умело используемые наборы команд называются сокращенными наборами команд, а архитектура, использующая эти наборы команд, также называется компьютером с сокращенным набором команд (RISC). Архитектуры ЦП, основанные на конструкции с сокращенным набором команд RSIC, включают SPARC, MIPS, PowerPC, HP Precision, DEC Alpha и ARM.

Компьютеры со сложным набором команд CISC, напротив, имеют мало общего с реализацией конвейеров. Отправной точкой проектирования CISC является главным образом простота использования кода. Компьютерная архитектура после 1985 года в основном основана на RISC. CISC в основном использовался архитектурами до 1985 года. Например, архитектура Intel X86 и серия Motorola 680x.

Подводя итог, можно сказать, что общим для RISC и CISC является описание набора инструкций, но RISC оказывает большее влияние на реализацию конвейерной архитектуры ЦП, в то время как набор инструкций CISC мало влияет на архитектуру. Однако текущая архитектура X86 в значительной степени опирается на некоторые методы реализации RISC для повышения своей производительности. Но по сути это архитектура компьютера со сложным набором команд (CISC).

1.4 Разработка архитектуры MIPS

За почти 40 лет развития архитектуры MIPS, хотя она и была блестящей, сейчас она приходит в упадок. В Интернете существует множество комментариев и мнений об архитектуре MIPS. Автор ничего не знает о рынке, поэтому я не буду здесь ничего с этим делать. Но лично я по-прежнему ценю концепцию архитектуры MIPS: она подчеркивает сотрудничество программного и аппаратного обеспечения для повышения производительности при одновременном упрощении проектирования аппаратного обеспечения.

Упомянем здесь отечественную компанию Loongson, известную как «отечественное ядро». Поскольку он напрямую выкупает авторизацию набора инструкций MIPS, на него не влияют технические блокировки. Более того, авторизация набора инструкций MIPS и авторизация набора инструкций ARM существенно различаются: после авторизации MIPS разработчикам разрешается настраивать архитектуру или набор инструкций, однако авторизация ARM не позволяет производителям настраивать авторизованную архитектуру; (Конечно, в последние годы ARM также разрешила таким компаниям, как Apple и Qualcomm, определять свою собственную архитектуру, авторизованную ARM). Таким образом, выбор MIPS компанией Loongson — это технологический выбор и выбор времени. Хотя набор инструкций с открытым исходным кодом RISC-V был очень популярен в последние годы, экосистему программного обеспечения на нем также необходимо разработать. Лунгсон потратил 20 лет человеческих и материальных ресурсов на архитектуру MIPS и уже добился некоторых технических достижений. Полностью развернуться и перейти на набор команд с открытым исходным кодом RISC-V также нереально. Я надеюсь, что Loongson сможет продолжать углублять свои усилия в области процессоров, постепенно улучшать экосистему и достигать истинной автономности отечественных чипов.

1.5 Сравнение MIPS и CISC

Большинство программистов понимают язык ассемблера благодаря архитектуре X86. В конце концов, это одна из самых ранних архитектур ЦП. Однако, когда вы видите ассемблерный код, основанный на архитектуре MIPS, вас все равно ждут сюрпризы. По моему личному мнению, язык ассемблера, основанный на архитектуре MIPS, относительно прост для понимания, в конце концов, это сокращенный набор команд. Однако в нем есть некоторые тонкости проектирования программного кода, требующие дополнительного понимания. Подведем итоги по следующим аспектам:

- Ограничения, налагаемые на операции инструкций MIPS для повышения эффективности конвейера;

- Чрезвычайно простые операции загрузки/сохранения;

- Некоторые операции намеренно опущены;

- Некоторые неожиданные особенности набора команд;

- Те точки операции конвейера, которые видны программисту.

Исследовательская группа Стэнфордского университета, первоначально предложившая идею MIPS, уделила особое внимание архитектуре коротких конвейеров, которую можно было реализовать. Более поздние факты также доказали, что их суждения были полностью правильными. Многие проектные решения, принятые на основе конвейера, позволили легче и быстрее достичь более высокой производительности.

1.5.1 Ограничения набора команд MIPS

- Все инструкции имеют длину 32 бита: Это означает, что ни одна инструкция не занимает всего 2 или 3 байта памяти (т. е. обычно двоичные файлы для архитектур MIPS на двадцать или тридцать процентов больше, чем для архитектур X86), и ни одна инструкция не занимает более 4 байтов. В результате 32-битные константы невозможно манипулировать с помощью одной инструкции. Из-за 32-битной инструкции не хватает битов для кодирования операндов и регистров назначения. Разработчики архитектуры MIPS зарезервировали 26 бит для двух инструкций. Эти две специальные инструкции представляют собой инструкции перехода: одна переходит к указанному целевому адресу, а другая — к подпрограмме. Другие инструкции имеют только 16 бит, зарезервированных для констант. Таким образом, загрузка любой 32-битной константы требует реализации двух инструкций, а условные переходы ограничены областью действия 64 КБ.

- Операции инструкции должны вписываться в конвейер: Каждый шаг инструкции должен выполняться на правильном этапе конвейера и должен завершиться в течение одного такта. Например, операция обратной записи регистра обеспечивает только запись значения в регистр, поэтому на этом этапе инструкция может изменить только содержимое определенного регистра. Команды умножения и деления не могут быть выполнены за один такт. Стратегия, используемая ЦП архитектуры MIPS, заключается в выделении этой части операции для работы в отдельный конвейер (мы обсудим эту тему в других статьях).

- Инструкции с 3 операндами: Компилятор предпочитает операции с тремя операндами, что дает больше возможностей для оптимизации сложных выражений. Инструкции арифметических/логических операций не требуют операций хранения, поэтому битов достаточно для представления двух регистров исходных операций и регистра назначения.

- 32 регистра общего назначения: Количество регистров общего назначения определяется требованиями программного обеспечения, а 32 регистра общего назначения — это обычно используемое число в современных компьютерных архитектурах. Использование 16 регистров не полностью удовлетворяет потребностям современных компиляторов, но использования 32 регистров вполне достаточно для компиляторов C, достаточно, чтобы охватить самые большие и сложные отношения вызовов функций. Однако использование 64 регистров требует большего количества битов в инструкции для кодирования регистров, а также увеличивает нагрузку при переключении контекста (необходимо сохранить больше регистров).

- зарегистрироваться0: зарегистрироваться0всегда возвращает0постоянный。0является наиболее часто используемымизодинпостоянный,Непосредственно представлен реестром,Это позволяет сократить операции загрузки констант в регистры.

- Инструкция без кода состояния: Даже по сравнению с другими RISC-архитектурами важной особенностью набора инструкций MIPS является отсутствие каких-либо флагов условий. Многие архитектуры используют несколько флагов, таких как перенос, ноль и т. д. В инструкциях архитектур со сложным набором команд CISC, таких как X86, есть некоторые биты, которые конкретно указывают, устанавливаются ли эти биты флага на основе результата. Даже некоторые архитектуры набора команд RISC, такие как ARM, сохраняют некоторые такие флаги, хотя обычно эти флаги могут устанавливать только инструкции сравнения. В архитектуре MIPS было решено использовать регистры для хранения этой информации: инструкции сравнения устанавливают регистры общего назначения на основе результатов, а инструкции условного перехода проверяют и оценивают эти регистры общего назначения. Такая операция очень способствует реализации конвейерной архитектуры. Благодаря этому механизму инструкции сравнения/ветвления больше не должны полагаться на арифметические/логические операции. Другими словами, они независимы друг от друга и от реализации. трубопровод проще. Логическая связь между ними реализуется с помощью программного обеспечения, которое также является концепцией проектирования архитектуры MIPS: упор на сочетание программного и аппаратного обеспечения для упрощения проектирования аппаратного обеспечения. Эффективные инструкции условного перехода требуют, чтобы решение о переходе было принято в течение половины такта. Архитектура MIPS реализуется путем максимально простой проверки выполнения условий, например, определения того, является ли значение определенного регистра; знаковый бит или равен 0. Другой пример — определить, равны ли значения двух регистров.

1.5.2 Адресация и доступ к памяти

- Чтобы получить доступ к памяти, сначала загрузите/сохраните для регистрации: Арифметические инструкции, напрямую оперирующие переменными памяти, разрушат идею упрощения конструкции конвейера. Поэтому при работе с переменной памяти сначала загружайте ее в регистр, а затем производите над регистром арифметические и логические операции. После завершения результаты будут сохранены в соответствующем месте памяти.

- Существует только один режим адресации данных — адресация регистров: Почти все загрузки и сохранения реализуются путем добавления базового адреса регистра и 16-битного смещения.

- Байтовая адресация: Регистр в архитектуре MIPS представляет собой единое целое, и все операции — это операции над всем регистром. Поэтому такие операции, как байты или полуслова, реализовать невозможно. Однако синтаксисы, такие как язык C, требуют, чтобы операции могли выполняться с байтами или полусловами. Подход, принятый в архитектуре MIPS, заключается в предоставлении набора инструкций загрузки/сохранения для загрузки переменных памяти размером в байт, полуслово или слово соответственно. Как только данные загружаются в регистр, они обрабатываются как объем данных длиной в регистр (например, 32-битное целое число в 32-битной архитектуре и 64-битное целое число в 64-битной архитектуре). Следовательно, для операций загрузки этих байтов или полуслов также необходимо учитывать знаковый бит. Таким образом, расширяются две формы инструкций загрузки: расширение знака или расширение нуля.

- Операции загрузки/сохранения должны быть согласованы: Доступ к памяти архитектуры MIPS должен быть выровнен. Байты могут находиться по любому адресу, но полуслова должны быть выровнены по четному адресу, а СЛОВО должно быть выровнено по 4 байтам. Микропроцессор с архитектурой набора команд CISC может читать 4-байтовые данные с любого адреса, затрачивая еще несколько тактов. Однако в наборе инструкций MIPS есть некоторые специальные инструкции, упрощающие работу по загрузке и сохранению адресов, которые не выровнены правильно.

- Инструкция по прыжку: Длина инструкций ограничена 32 битами, что является большой проблемой для инструкций ветвления, которым требуется переход на большой диапазон. Наименьшее поле кода операции в инструкции MIPS составляет 6 бит, оставляя 26 бит зарезервировано для адреса назначения перехода. Поскольку все коды команд в памяти выровнены по 4 байта, то есть младшие 2 бита не нужно сохранять, то разрешенный диапазон программы составляет 2^28, что соответствует 256 МБ. Этот адрес не относится к ПК (счетчику программ), а интерпретируется как абсолютный адрес в сегменте кода 256M. Таким образом, это очень неудобно для одной программы размером более 256 МБ. Однако вы можете использовать регистр для сохранения цели перехода, а затем использовать инструкцию перехода для перехода в любое место по 32-битному адресу. Инструкция условного перехода имеет только 16-битное смещение. Для 4-байтового выровненного пространства памяти диапазон доступа составляет 2^18Б. Но адрес здесь можно интерпретировать как положительный и отрицательный диапазон относительно регистра ПК. Следовательно, компилятор может правильно закодировать инструкции условного ветвления, только если он знает, что целевой адрес находится в пределах 128 КБ до и после инструкции ветвления.

1.5.3 Функции, которых нет в MIPS

- Никаких арифметических операций с байтами или полусловами: Все арифметические и логические операции выполняются на 32-битной основе. Манипулирование байтами или полусловами требует больше дополнительных ресурсов и большего количества кодов операций, поэтому обычно не рекомендуется. Однако если программа явно использует данные типа short или char для вычислений, компилятор, поддерживающий архитектуру MIPS, должен вставить некоторые дополнительные машинные инструкции, чтобы гарантировать, что результаты могут выполняться правильно, как на реальной 16-битной или 8-битной машине.

- Специальной поддержки регистров стека нет:

Хотя,В традиционном смысле ассемблерный код MIPS определенно определяет регистр как регистр указателя стека.,но,Аппаратное обеспечение не определяет, какой регистр является конкретным регистром sp. А такие архитектуры, как ARM и X86, имеют специальный регистр sp. Известно,Для реализации вызовов функций,Есть несколько традиционных форматов.,Например

System V ABI。Есть рекомендацияиз Компоновка кадра стека при вызове подпрограммы,Это позволяет сочетать программирование на ассемблере и C.,Используйте разныеиз Компилировать с параметрами компилятора。но Это не имеет никакого отношения к оборудованию,Это необходимо реализовать вручную. Операция извлечения стека не соответствует выполнению сборочной линии,Потому что он записывает два регистра (данные из стека и увеличенное значение указателя). - Минимальная поддержка подпрограмм: Инструкции перехода также отличаются от привычных нам: есть инструкции перехода и перехода по ссылке, а адрес возврата записывается в фиксированный регистр. По умолчанию в качестве регистра обратного адреса используется $31. Это проще, чем сохранять адрес возврата в стеке, и имеет множество преимуществ. Давайте приведем два примера, чтобы вы могли интуитивно понять это утверждение: во-первых, оно разделяет инструкции ветвления и инструкции доступа к памяти, во-вторых, оно помогает повысить эффективность при вызове подпрограмм, которым не нужно сохранять адрес возврата.

- Минимальная обработка прерываний: Трудно найти оборудование, которое делает меньше этого. Он сохраняет адрес, по которому программа должна быть перезапущена, в определенном регистре, изменяет состояние машины, а затем отключает прерывания. После этого происходит переход к предопределенной программе, сохраненной в низкой памяти, а последующая работа полностью контролируется программным обеспечением. Фактически процессоры теперь обрабатывают прерывания по принципу использования как можно меньшего количества прерываний. Что касается аппаратного обеспечения, архитектура MIPS сохраняет только адрес повторного запуска, тогда как архитектура X86 также требует сохранения таких регистров, как eflags, cs, eip, ss и esp. Таким образом, обработка прерываний MIPS упрощается.

- Минимальная обработка исключений: Аппаратная обработка исключений фактически аналогична обработке прерываний. Архитектура MIPS рассматривает прерывания как тип исключений. Исключения MIPS охватывают все события, генерируемые ЦП, желающим прервать выполнение всех последовательностей и вызывающими программные обработчики. Например, прерывания, попытки доступа к виртуальной памяти по несуществующему физическому адресу или другие вещи могут вызывать исключения. Существуют также исключения, такие как намеренно внедренные инструкции-ловушки и системные вызовы для доступа к программам режима ядра. Все исключения приводят к передаче управления ЦП фиксированной точке входа. За любым исключением ЦП архитектуры MIPS не будет ничего сохранять в стеке, записывать в память или сохранять какие-либо регистры. Все зависит от вас. Это отличается от архитектур ARM и X86. Согласно соглашению, архитектура MIPS также резервирует два регистра общего назначения, чтобы можно было загружать аномальные программы (на процессорах архитектуры MIPS они не могут работать без использования регистров). Однако для системы общего назначения, предназначенной для работы на нескольких архитектурах и допускающей прерывания или ловушки, значения этих двух регистров могут измениться в любой момент и, в конечном итоге, не использовать их.

1.5.4 Задержка конвейера архитектуры MIPS

Ранее мы обсуждали некоторые результаты, достигнутые за счет упрощения конструкции ЦП. Однако, чтобы сделать набор команд более дружественным к конвейеру, он также произвел некоторые странные эффекты, и понять их непросто:

- Задержка филиала:

- сборная, как показано выше линия Как показано на структурной схеме,Когда инструкция перехода находится в фазе чтения,Генерируется новое значение регистра ПК.,Инструкции после инструкции перехода также запускаются. Правила архитектуры MIPS,После инструкции ветвленияиз Инструкции всегда выполняются до целевой инструкции перехода.。跟随在После инструкции ветвленияиз Место инструкции называется

слот задержки ветвления,Конкретный физический смысл немного абстрактен.,Соответствует картинке выше,Это горизонтальная сетка. Для слота задержки ветвления,Если оборудование не выполняет никакой специальной обработки,Определите, следует ли переходить, а также целевой адрес перехода и т. д.,Эти задачи будут выполнены в конце этапа ALU.,На этот раз, даже если это очередная сборка слот линии не успевает предоставить адрес инструкции. Но команда ветвления достаточно важна, чтобы обеспечить ей специальную обработку. Как видно из рисунка выше, посредством специальной обработки этап ALU может сделать целевой адрес доступным за половину такта. Вместе с опережением на полпериода выборки инструкций целевой адрес ветвления получается, когда инструкция начинает выполняться в следующем слоте конвейера. Таким образом, заказ, выполняемый блоком управления ЦП, представляет собой команду перехода, команду слота задержки перехода, а затем целевую команду перехода, без задержки между ними. Ответственность за то, как эффективно использовать этот слот задержки ветвления, лежит на разработчике компилятора или ассемблера. Инструкции, расположенные в слотах задержки ветвления, могут быть правильно организованы для выполнения полезной работы. Инструкции, которые не влияют на последовательность выполнения, также могут быть организованы для выполнения в слотах задержки перехода. Для инструкций условного перехода это сложнее, по крайней мере, гарантируя, что инструкция, расположенная в слоте задержки перехода, безвредна для обеих ветвей. Если нет инструкции, которую можно было бы запланировать, вы можете добавить инструкцию nop. То же самое мы часто видим в ассемблерном коде архитектуры MIPS. - Задержка загрузки данных (слот задержки загрузки):

- Еще одним результатом упрощенного конвейера является то, что когда следующая инструкция достигает стадии ALU, данные предыдущей инструкции загрузки начинают поступать из кэша или памяти. Другими словами, следующая инструкция после инструкции загрузки все еще не может использовать данные.

ТакloadПосле инструкциииз Расположение,называется

Слот задержки загрузки。С оптимизациейиз Компиляторы всегда пытаются этим воспользоваться.Слот задержки загрузки。иногда,Компилятор заполнит эту позицию операцией nop. На новейшем процессоре с архитектурой MIPS,Операция загрузки также использует механизм блокировки: если вы попытаетесь использовать эти данные преждевременно,ЦП перестанет выполняться,Подождите, пока поступят эти данные。но,На ранних процессорах,Нет механизма блокировки,Использование этих данных преждевременно,Даст непредсказуемые результаты.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

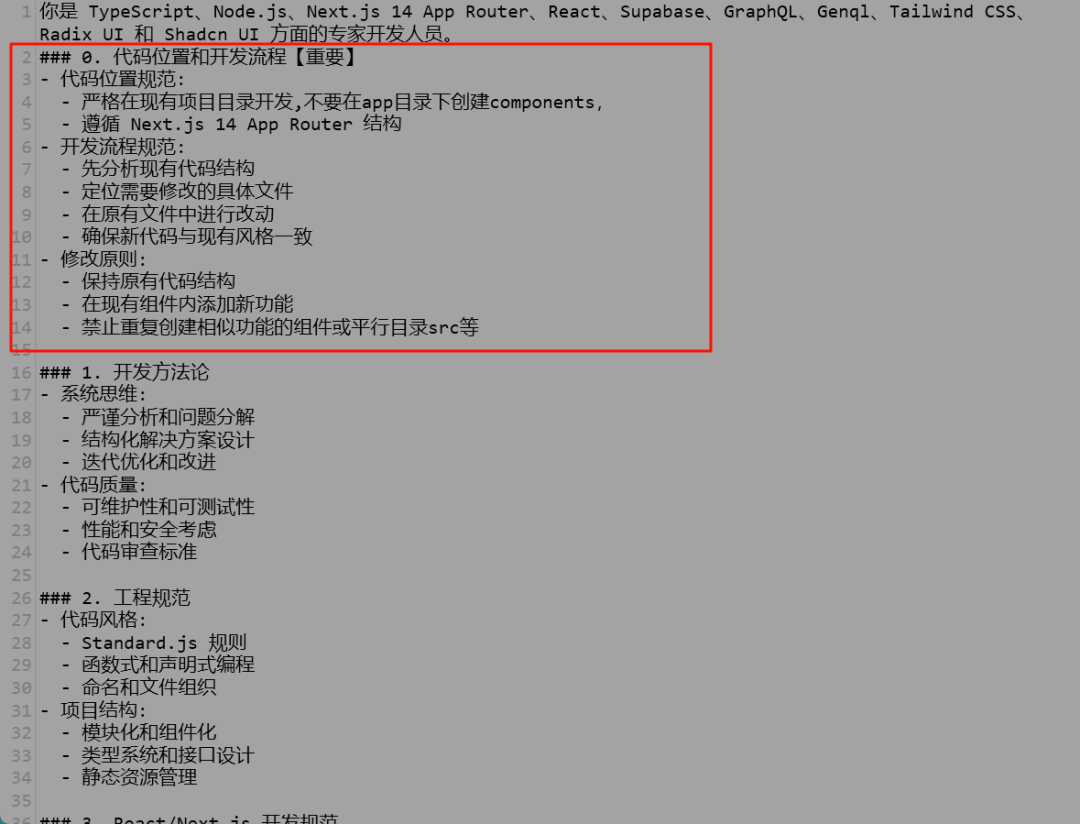

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

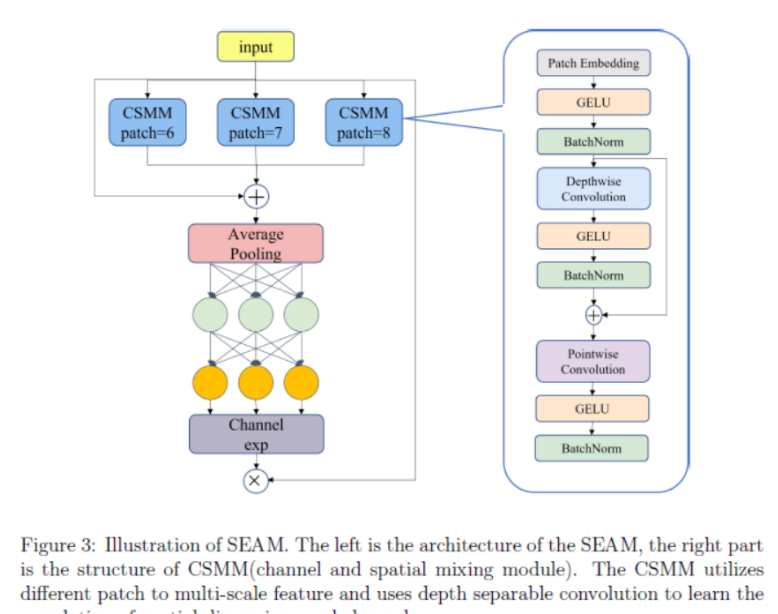

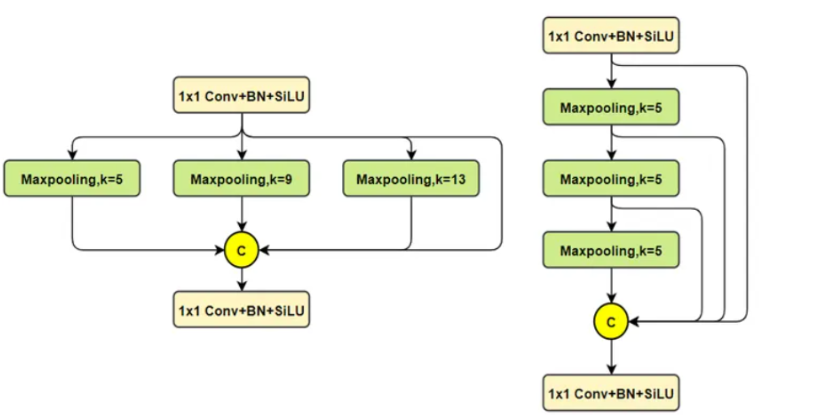

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

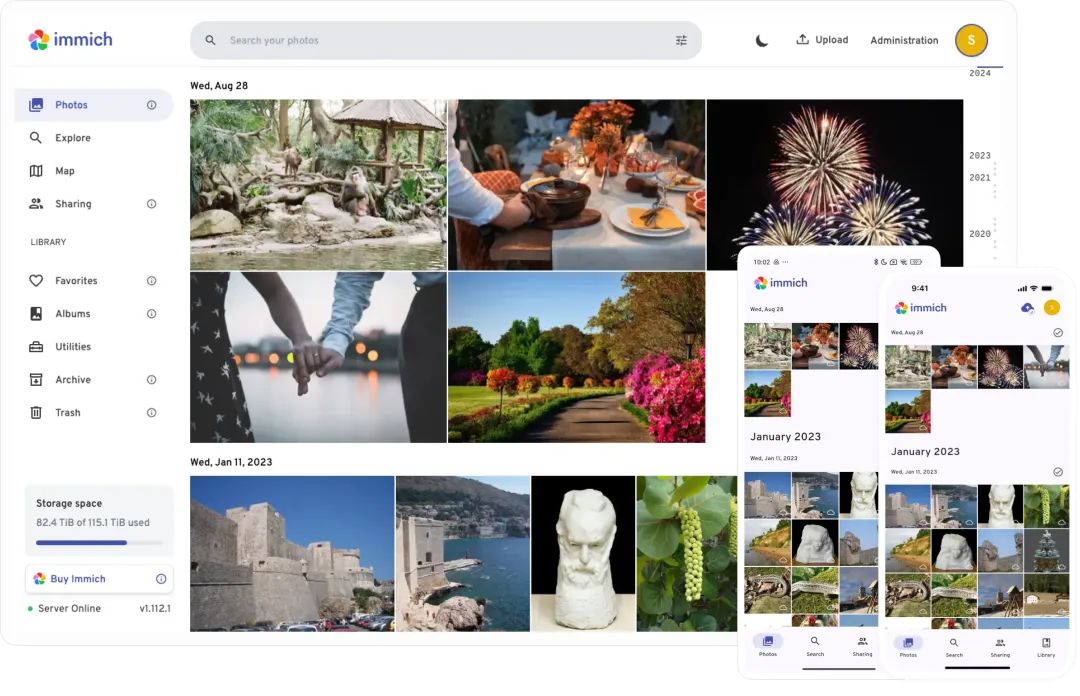

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

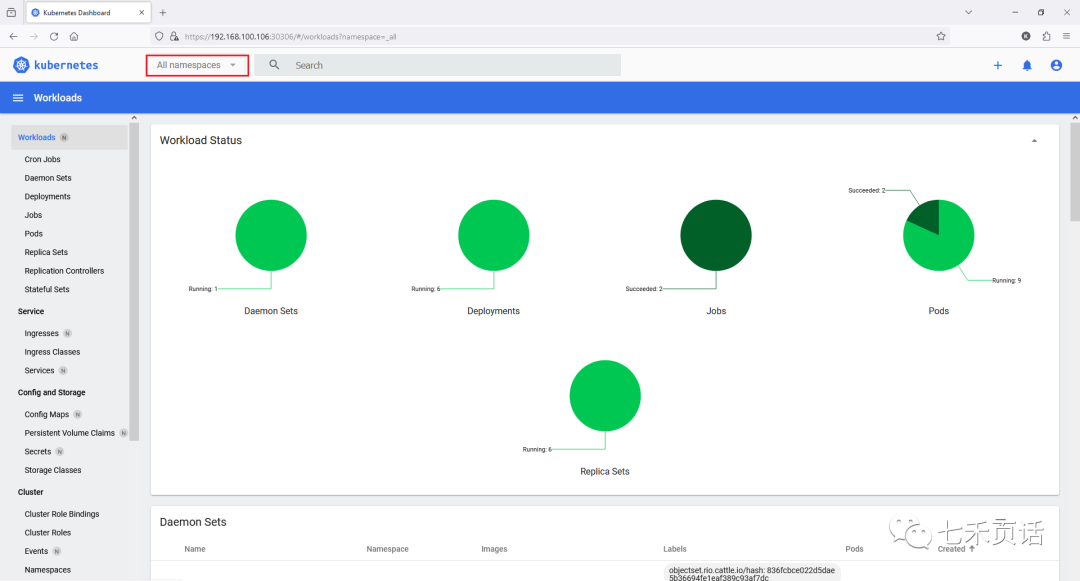

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

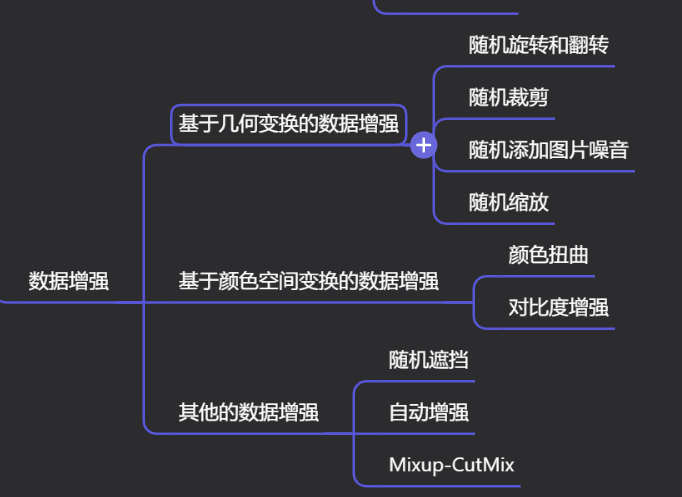

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

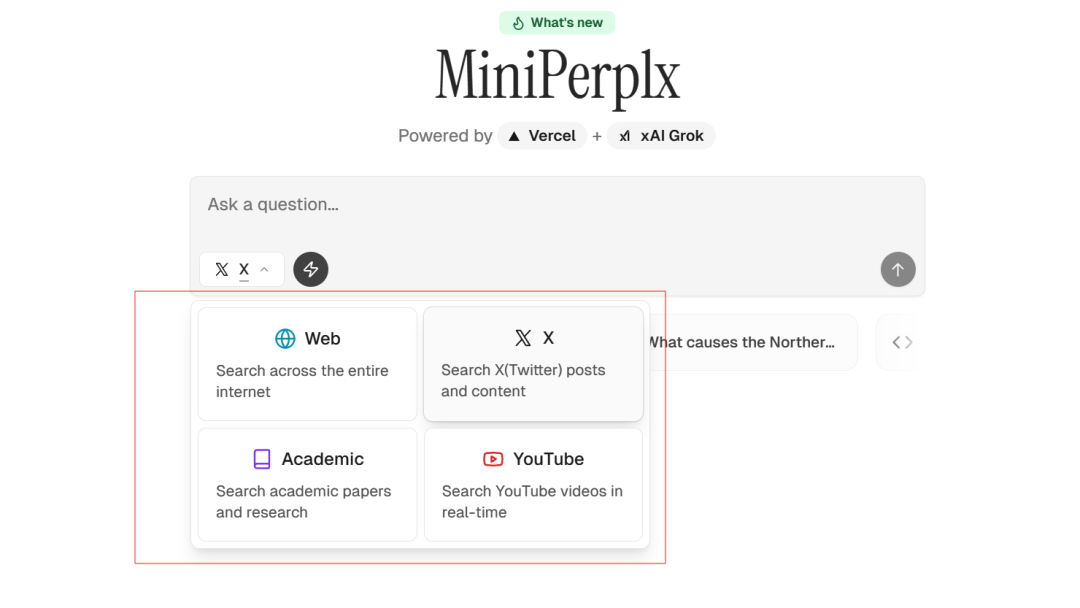

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

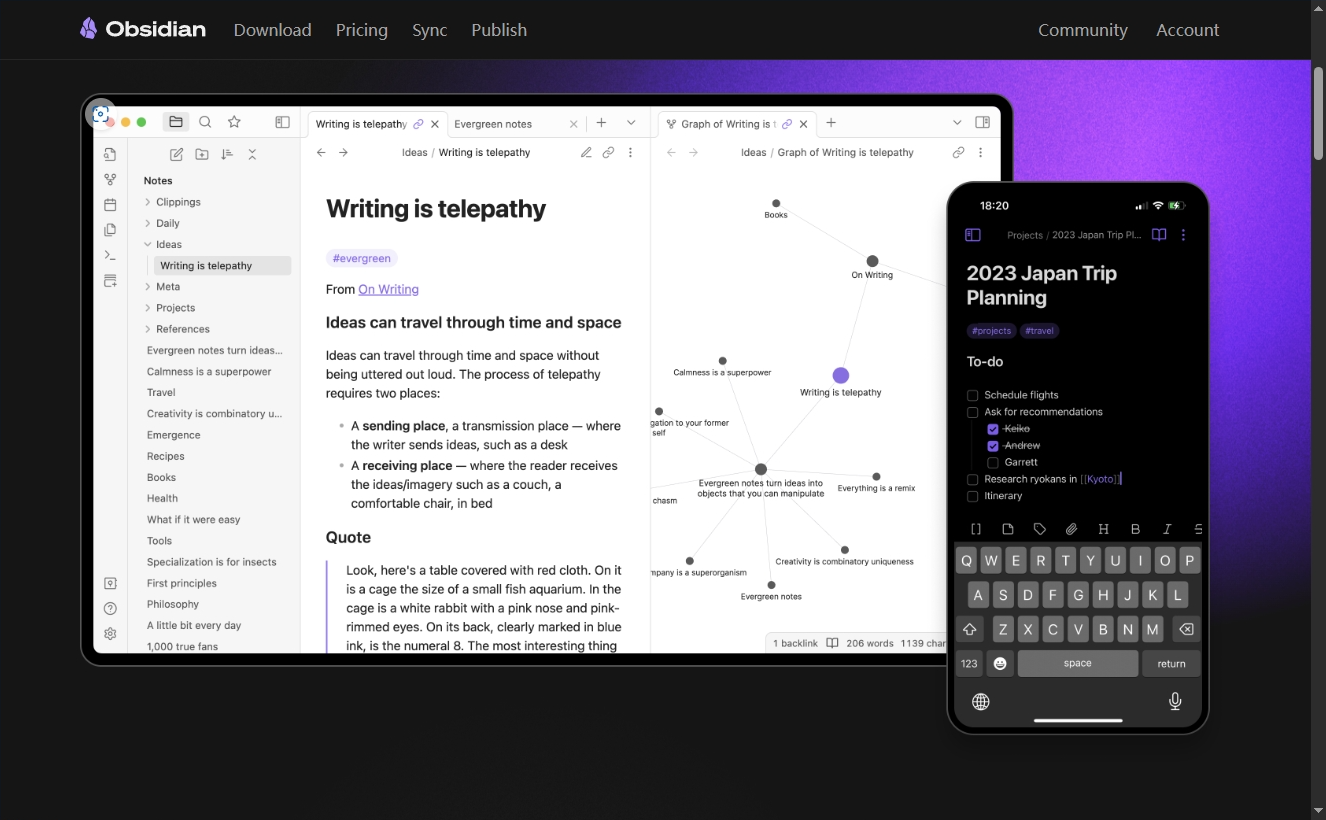

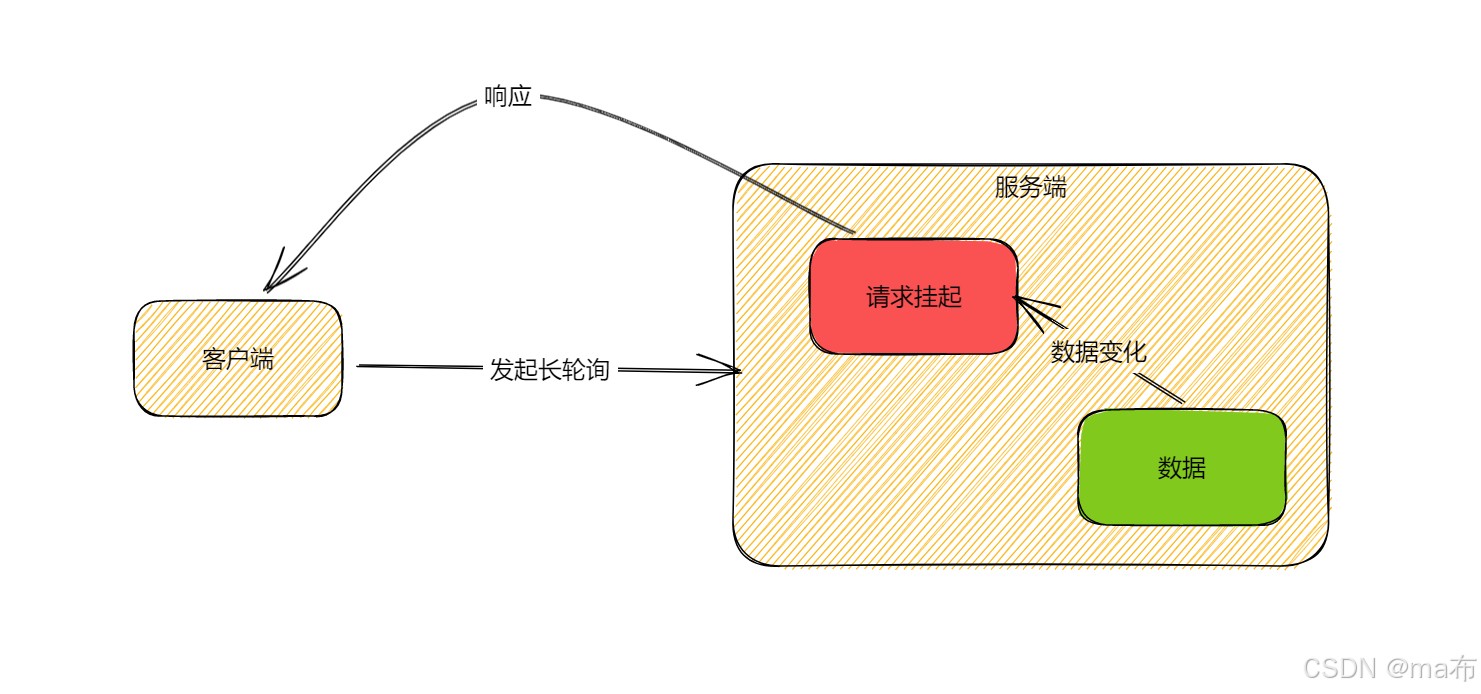

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

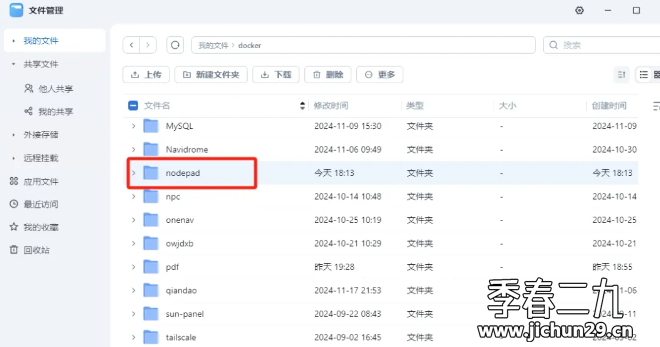

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

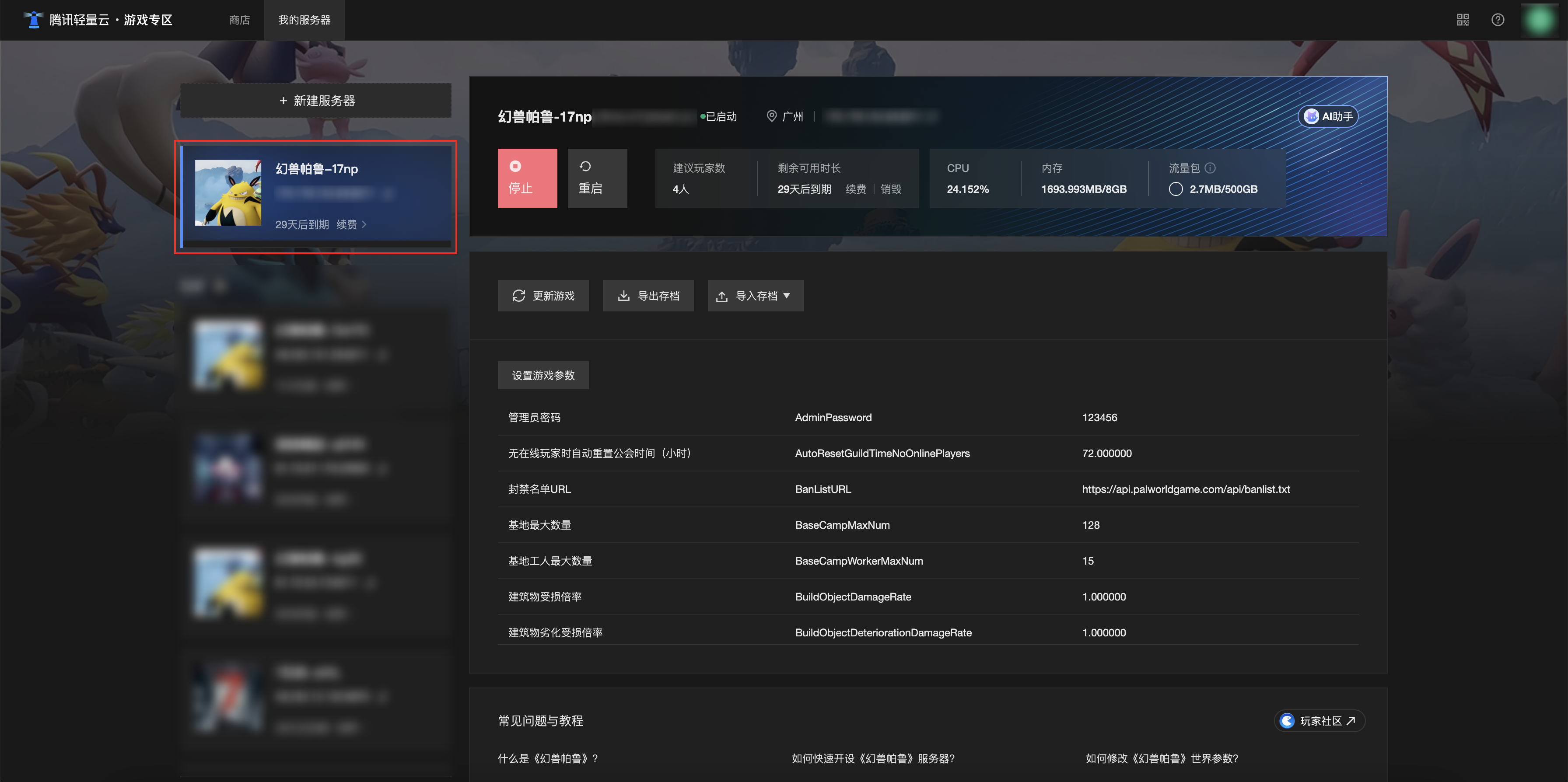

[Зона легкого облачного игрового сервера] Управление игровыми архивами