Цифровое аппаратное моделирование SystemVerilog-комбинационное логическое моделирование (2) всегда и Always_comb

Цифровые схемы уровня вентиля можно разделить на две основные категории: комбинационная логика и последовательная логика. Защелки представляют собой пересечение комбинационной и последовательной логики и позже будут рассмотрены как отдельная тема.

Комбинационная логика описывает схемы уровня вентиля, в которых выход логического блока напрямую отражает комбинацию входных значений этого блока, например, выход вентиля И с двумя входами является логическим И двух входов. Если входное значение изменится, выходное значение отразит это изменение, и модель комбинационной логики RTL должна отражать это поведение на уровне вентиля, а это означает, что выход логического блока всегда должен отражать комбинацию текущих входных значений. этого логического блока.

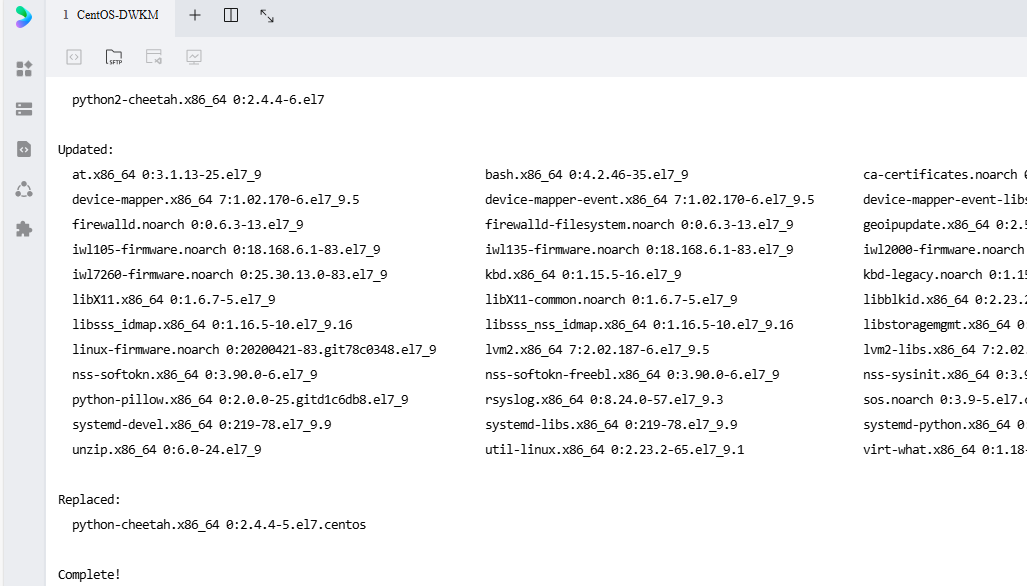

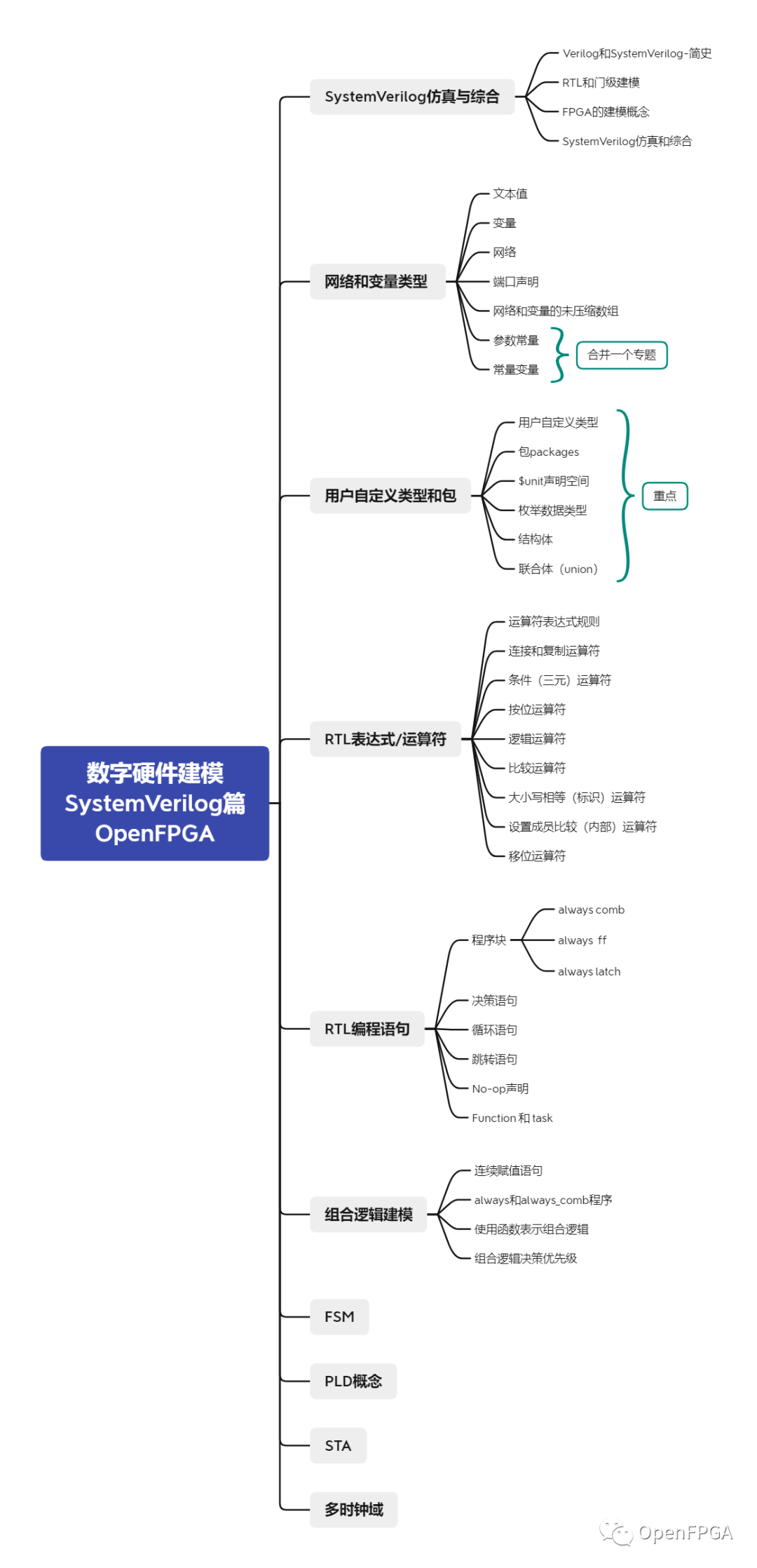

SystemVerilog имеет три способа представления комбинационной логики на синтезированном уровне RTL: операторы непрерывного присваивания, блоки всегда и функции. В следующих нескольких статьях мы рассмотрим каждый стиль кодирования и порекомендуем лучшие стили кодирования.

процедуры Always и Always_comb

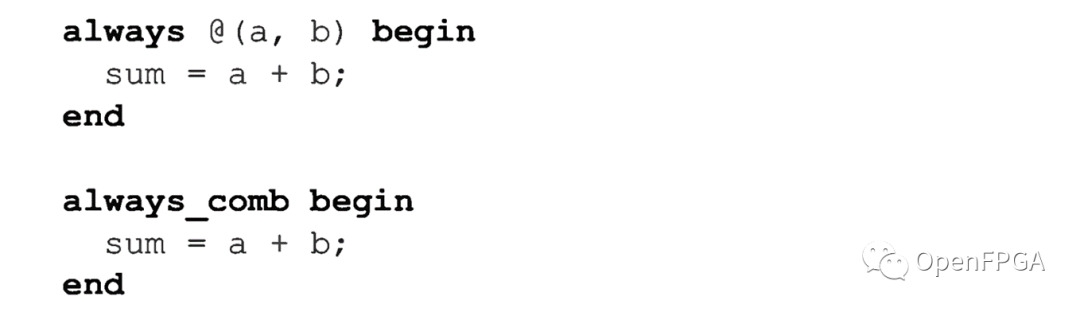

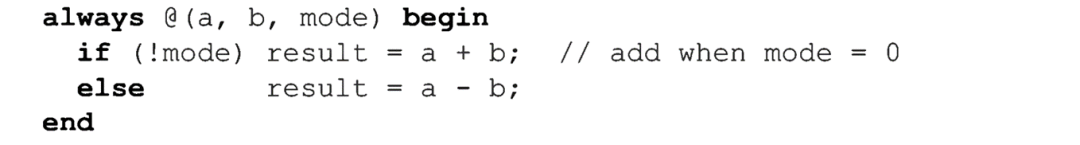

Основной конструкцией моделирования RTL для комбинационной логики является процедура Always, использующая общее ключевое слово Always или ключевое слово Always_comb, специфичное для RTL. Эти программы всегда могут использовать преимущества мощных операторов операторного программирования, обсуждавшихся ранее, тогда как операторы непрерывного присваивания ограничиваются использованием операторов SystemVerilog. Пример простого комбинационного логического сумматора, смоделированного как программа Always и программа Always_comb, выглядит следующим образом:

Всегда программа, которая может синтезировать комбинационную логику

Компилятор синтеза поддерживает процедуры Always и Always_comb.

При использовании программы Always общего назначения компилятор синтеза накладывает некоторые ограничения на кодирование, которые инженер-проектировщик RTL должен понимать и соблюдать. Эти ограничения включают в себя:

- Список чувствительности программы должен включать каждый сигнал, значение которого может повлиять на выходной сигнал комбинационной логики. Списки чувствительности подробно обсуждаются в следующем разделе.

- Список чувствительности программы должен быть чувствителен ко всем возможным изменениям значений каждого сигнала. Он не может содержать ключевые слова posege или negedge, которые ограничивают чувствительность к конкретным изменениям.

- Программа должна выполняться за нулевое время моделирования и не должна содержать каких-либо задержек распространения (включая использование операторов управления #, @ или ожидания).

- Переменные, назначенные в программе комбинационной логики, не должны присваиваться какой-либо другой программой или последовательными операторами присваивания. (В одной программе допускается несколько заданий.)

Руководство по передовой практике 7-3 |

|---|

Смоделируйте всю комбинационную логику RTL с нулевой задержкой. |

Синтезатор не допускает задержки управления временем, такие как @ или ожидание, и игнорирует # задержки. Игнорирование # задержек может привести к несоответствию между моделью RTL, проверенной при моделировании, и реализацией уровня вентиля, игнорируемой при синтезе.

Моделирование с использованием общей процедуры Always

Руководство по передовой практике 7-4 |

|---|

Комбинационная логика моделируется с помощью программы Always_comb, специфичной для RTL. Не используйте общие процедуры Always в моделях RTL. |

Функция Always_comb, специфичная для RTL, автоматически применяет ограничения кодирования, перечисленные выше. Чувствительные списки выводятся, не допускают @ или управления временем ожидания, а переменные, назначенные в процедуре Always_comb, не могут быть назначены другими процедурами или последовательно.

Хотя программы Always не рекомендуются для моделирования RTL, в этой статье обсуждается, как правильно использовать общую программу Always для моделирования комбинационной логики, поскольку такие общие программы распространены в традиционных моделях Verilog.

Чувствительные списки комбинационной логики.УниверсальныйalwaysПрограмма требует список чувствительности,чтобы сообщить эмулятору, когда обрабатывать операторы программирования в программе. Список чувствительности задается в форме @ (список сигналов),Как показано в следующем примере:

Каждый сигнал в списке чувствительности отделяется запятой (,), как в примере выше, или ключевым словом или, как в @ (a или b или режим). Использование запятой (,) не имеет преимуществ или недостатков по сравнению с ключевым словом или. Некоторые инженеры предпочитают списки, разделенные запятыми (,), потому что ключевое слово или может быть ошибочно принято за логическую операцию ИЛИ, а не просто за разделитель между сигналами в списке.

Полный список чувствительности.Для комбинационной логики,Выход комбинированного блока является прямым отражением текущего значения входа блока.,Чтобы смоделировать такое поведение,Когда значение любого сигнала изменяется, влияя на значение выхода программы.,программе всегда необходимо выполнять свои операторы программирования. Входными данными для комбинированной программы всегда является любой сигнал, значение которого считывается оператором в программе.,В примере сумматора выше,Вход программы - считываемые в программе сигналы: а, б и режим.

Программный ввод и вход модуля。Входы комбинационной логической программы могут не совпадать с входными портами модуля, содержащего программу.。Модули могут содержать несколько блоков и последовательные операторы присваивания.,поэтому,Каждый программный блок имеет входные порты. Модули также могут содержать внутренние сигналы.,Передавайте значения между блоками или последовательными операторами присваивания. Эти внутренние сигналы не будут включены в список портов модуля.

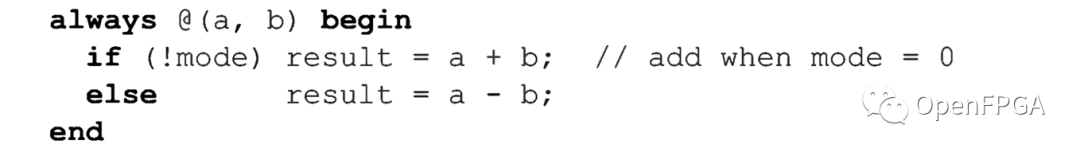

Неполный список чувствительности-глюк моделирования。

Gotcha — это программный термин, используемый для описания кода, который синтаксически корректен, но не работает должным образом. Обычно программы допускают ошибки кодирования такого типа. Если один или несколько входов программы комбинационной логики случайно опущены из списка чувствительности, модель RTL также скомпилируется и может даже показаться правильной симуляцией. Однако полная проверка показывает, что выход комбинационного логического блока не отражает текущую комбинацию входных значений за определенный период времени. Рассмотрим следующий фрагмент кода:

Если режим изменится, вывод результата не будет обновлен с учетом нового результата операции, пока a или b не изменит значение. Значение результата неверно в течение времени между изменением режима и изменением a или b.

Эта ошибка кодирования заметна в небольших комбинационных логических блоках, которые считывают только несколько значений сигналов, но нередко более крупные и сложные логические блоки считывают 10, 20 или даже десятки сигналов. Когда задействовано так много сигналов, легко случайно пропустить сигнал в вашем списке чувствительности. Блок Always также часто модифицируют во время разработки проекта, например, добавляя в логику еще один сигнал, но забывая добавить его в список конфиденциальных данных. Серьезная опасность этой ошибки кодирования заключается в том, что многие компиляторы синтеза по-прежнему реализуют эту неправильную модель RTL как комбинационную логику уровня вентиля, возможно, с легко игнорируемым предупреждающим сообщением, даже несмотря на то, что реализация компилятора синтеза могла быть разработана по замыслу разработчика, но это не так. не является конструктивной особенностью, проверенной в ходе моделирования RTL. Поэтому функциональность конструкции не полностью проверена, что может привести к ошибкам при работе на реальной ASIC или FPGA.

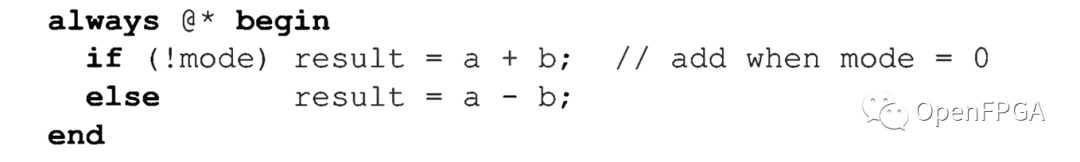

Устарело всегда@

программа. Стандарт IEEE 1364-2001 (широко известный как Verilog-2001) пытается решить проблему неполных списков конфиденциальности путем добавления специального тега, который автоматически выводит полный список конфиденциальности, например:

Вы также можете использовать круглые скобки, например @(

). По сравнению с явным перечислением сигналов в списке, чувствительном к комбинационной логике, @

Разметка обеспечивает лучший стиль кодирования. Однако с этой разметкой есть две проблемы. Во-первых, компиляторы синтеза накладывают некоторые ограничения на комбинационно-логическое моделирование. использовать@

Можно вывести список чувствительности, но другие всеобъемлющие правила комбинационного логического моделирования не соблюдаются. @

Вторая проблема заключается в том, что полный список чувствительности не выведен. Если программа комбинационной логики вызывает функцию, но не передает все сигналы, используемые в функции, в качестве аргументов функции, будет выведен неполный список чувствительности.

Руководство по передовой практике 7-5 |

|---|

Автоматически выводит правильные списки конфиденциальной информации комбинаторной логики, используя специальную процедуру Always_comb в SystemVerilog. Не используйте устаревший @* для вывода конфиденциальных списков. |

Программа Always_comb выведет точный конфиденциальный список без опасностей, связанных с явными списками, или @

проблема вывода. Процедура Always_comb также применяет ограничения кодирования, необходимые компилятору синтеза для точного моделирования поведения комбинационной логики.

Исходный язык Verilog, представленный в 1980-х годах, всегда содержал только программы общего назначения. Несмотря на то, что этот процесс очень полезен, он имеет серьезные ограничения в своей универсальности при использовании для RTL-моделирования. Как программа общего назначения, ее всегда можно использовать для моделирования комбинационной логики, последовательной логики, логики защелки и различных процессов проверки. Когда компилятор синтеза сталкивается с процедурой Always, у него нет возможности узнать, какой тип функциональности намеревался смоделировать инженер-проектировщик. Вместо этого компилятор синтеза должен проанализировать содержимое процедуры и попытаться сделать вывод о намерениях разработчика. Синтез, скорее всего, приведет к другому типу функциональности, чем ожидал инженер.

Еще одним ограничением универсальной программы Always является то, что она не применяет правила кодирования RTL, необходимые компилятору синтеза для представления комбинационного логического поведения. Модели, использующие универсальную программу Always, могут выглядеть корректными, но не могут синтезировать ожидаемую функциональность, поэтому модель RTL необходимо переписать и функциональность повторно проверить в моделировании, прежде чем модель можно будет синтезировать, что приводит к потере времени на проектирование.

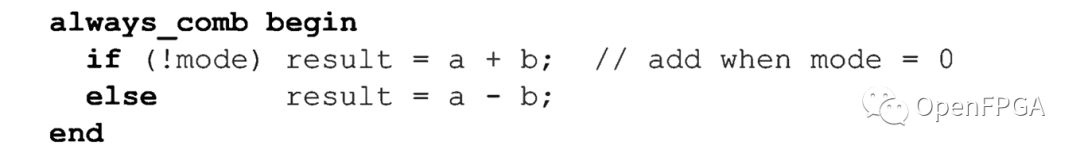

Моделирование с использованием программы Always_comb, специфичной для RTL.

SystemVerilog представляет программы Always, специфичные для RTL, такие как Always_comb, для устранения ограничений программ Always общего назначения. В следующем примере моделируется показанная ранее функциональность арифметико-логического устройства, но вместо Always используется Always_comb.

Процедура Always_comb имеет множество преимуществ при написании моделей RTL:

- Автоматически делать вывод; список чувствительность Список полностью полный, за исключением углового случая @*, подразумевающего неполный список конфиденциальных данных.

- Выполнение операторов задержки, таких как #, @ или wait, не допускается в процедуре Always_comb, которая является обязательной для подробных рекомендаций по использованию программ с нулевой задержкой. Использование этих элементов управления временем в Always Comb является ошибкой, которая будет обнаружена во время компиляции и маршрутизации модели RTL.

- Любая переменная, назначенная в процедуре «always_comb», не может быть назначена из другой процедуры или из оператора последовательного присваивания, что является ограничением, требуемым компилятором синтеза. В ходе компиляции и маршрутизации моделей RTL будут обнаружены ошибки кодирования, нарушающие это правило синтеза.

Семантические правила Always_comb соответствуют ограничениям кодирования компилятора синтеза для моделей RTL комбинационной логики. Эти правила помогают гарантировать, что инженерное время будет потрачено впустую на проверку проектов, которые невозможно синтезировать.

Автоматически оценивается в начале моделирования。always_combПроцедуры также имеют семантическое правило.,Он специально разработан для использования в моделировании. Поведение комбинационной логики,Выходное значение представляет собой комбинацию входных значений для этого логического блока. Для общей программы всегда,Чтобы инициировать выполнение оператора присваивания в программе,Сигналы в списке чувствительности должны изменить значение. Если ни один из сигналов в списке чувствительности не изменил значение в начале моделирования,тогда вывод программы комбинационной логики не будет обновляться,для соответствия входных значений процессу. Программы комбинационной логики по-прежнему будут выдавать неверные выходные значения.,до тех пор, пока сигнал в списке чувствительности не изменит значение. Эта проблема связана с ошибкой моделирования RTL.,Реализация на уровне шлюза не имеет этой проблемы.

Программа Always_comb, специфичная для RTL, решает эту проблему моделирования. Программа Always_comb автоматически запустится один раз в начале моделирования, чтобы гарантировать, что все переменные, назначенные в программе, точно отражают значения, введенные программой в нулевой точке времени моделирования.

Использование блочного (комбинационной логики) присваивания

Руководство по передовой практике 7-6 |

|---|

При моделировании комбинационной логики используйте только присваивание блоков (=). |

SystemVerilogСуществует две формы оператора присваивания.:назначение блокировки(=)Кадзуиназначение блокировки(<=)。Эти типы присвоений влияют на порядок, в котором моделирование обновляет значения в левой части оператора присваивания.,Относительно любой другой активности моделирования в момент моделирования. Блокирующее присваивание (=) немедленно обновляет переменную слева.,Делает новое значение доступным для последующих операторов в группе операторов начала и конца. «Обновления на лету» эффективно моделируют поведение распространения значений в потоке данных комбинационной логики.

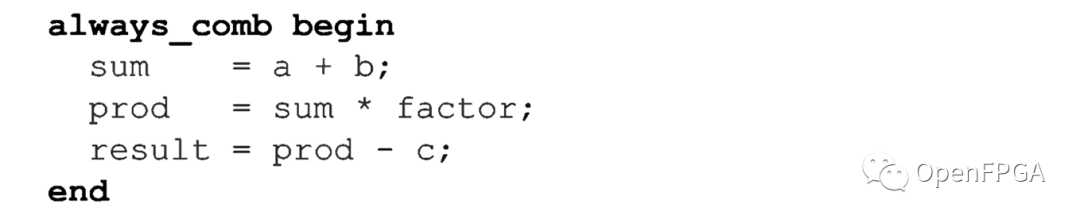

Следующий фрагмент кода демонстрирует поток данных комбинационной логики через несколько назначений в блоке комбинационной логики.

Во время этого процесса переменная sum немедленно обновляется до результата операции a+b. Это новое значение sum передается следующему оператору, где новое значение используется для расчета нового значения prod. Это новое значение prod затем передается в следующую строку кода и используется для расчета значения результата.

Блокирующее поведение операторов присваивания имеет решающее значение для правильного моделирования этого потока данных в модели RTL с нулевой задержкой. Блокирующие назначения в каждой строке кода будут блокировать вычисление следующей строки до тех пор, пока текущая строка не обновит свою левую переменную новым значением. Блокировка в каждой последующей строке кода оценки гарантирует, что каждая строка использует новое значение переменной, присвоенное. предыдущая строка.

Если бы неблокирующие присваивания использовались ненадлежащим образом в приведенном выше фрагменте кода, каждое присвоение будет использовать предыдущее значение переменной в ее правой части до того, как эти переменные будут обновлены новыми значениями. Очевидно, это не комбинаторно-логическое поведение! Однако при использовании неблокирующих присвоений компилятор синтеза все равно может создавать комбинационную логику, что приводит к несоответствию между поведением, проверенным при моделировании RTL, и фактическим поведением уровня вентиля после синтеза.

Как избежать неожиданных блокировок в программах комбинационной логики

Распространенной проблемой при RTL-моделировании является определение поведения фиксации в коде. Правила языка SystemVerilog требуют, чтобы левая часть назначения процедуры была переменной определенного типа, а тип данных Net (сеть) не должен появляться в левой части назначения программы. Это требование использования переменных может привести к непреднамеренной фиксации, что и является целью чистой комбинационной логики. Поведение фиксации возникает, когда запускается несинхронизируемая всегда программа (т. е. программа комбинационной логики), и переменным, используемым программой, не присваиваются значения. Две наиболее распространенные ситуации:

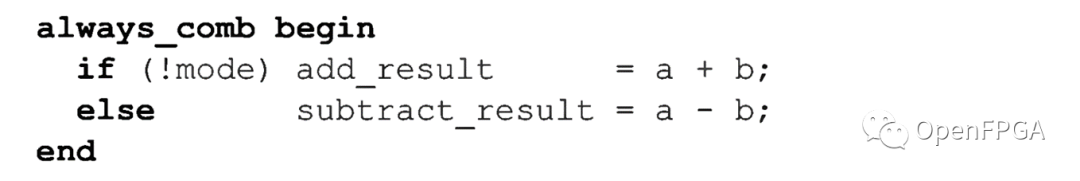

1. Операторы принятия решений назначаются разным переменным в каждой ветви, как показано в фрагменте кода ниже:

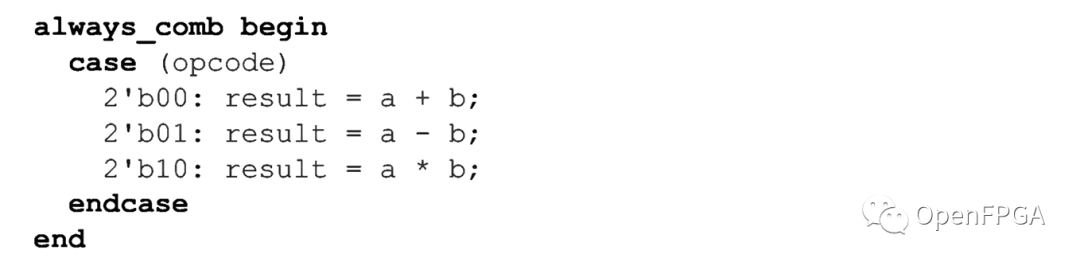

2. Операторы решения не разветвляются для каждого возможного значения выражения решения. Фрагмент кода ниже иллюстрирует проблему.

При моделировании этот простой пример правильно моделирует комбинационные логические сумматоры, вычитатели и умножители. Однако если значение, введенное опкодом, должно быть 2’b11, в этом примере не будет выполняться какое-либо присвоение переменной результата. Поскольку результат является переменной, он сохраняет свое предыдущее значение. Сохраненное значение ведет себя как защелка, хотя предполагается, что программа Always_comb будет вести себя как комбинационная логика.

Даже при использовании процедуры Always_comb выявляются блокировки. Однако компилятор синтеза и средство проверки lint сообщают о предупреждении или нефатальной ошибке о том, что блокировка была обнаружена в программе Always_comb. Это предупреждение является одним из нескольких преимуществ Always_comb перед обычной программой Always. Программа Always-Comb записывает намерение инженера-проектировщика, и когда код в программе не соответствует этому намерению, программный инструмент может сообщить об этом несоответствии намерений.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

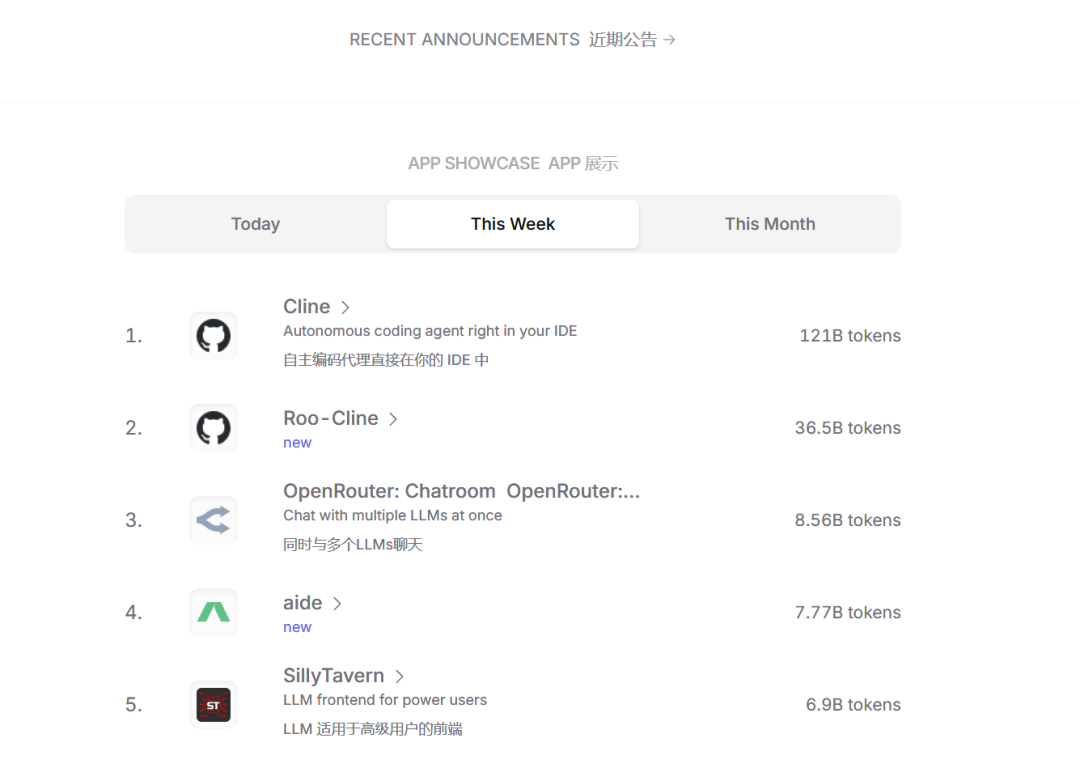

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

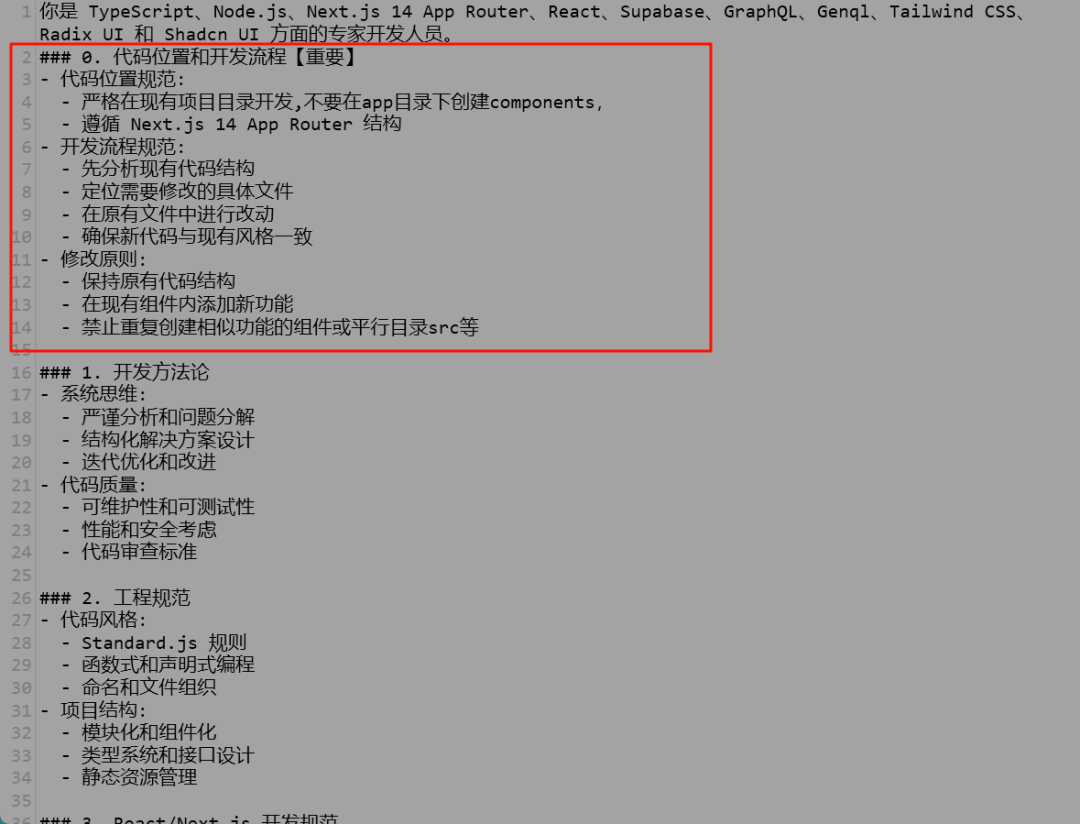

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

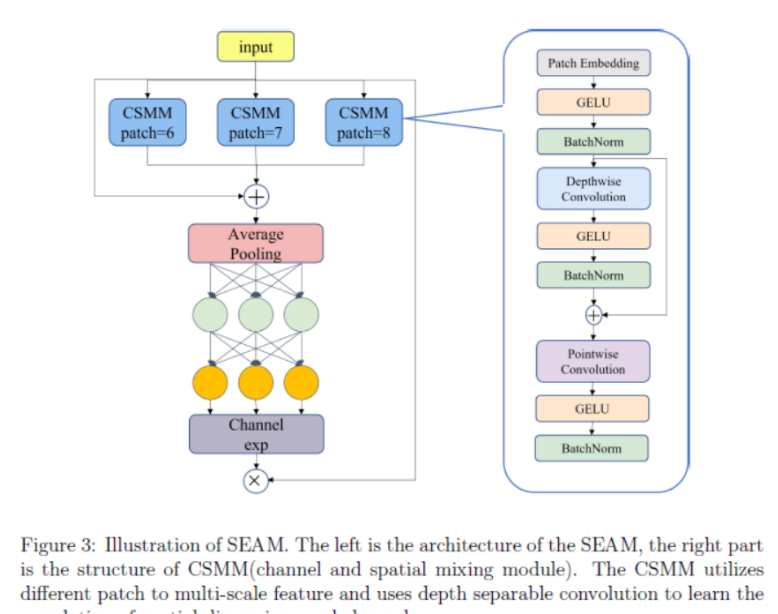

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

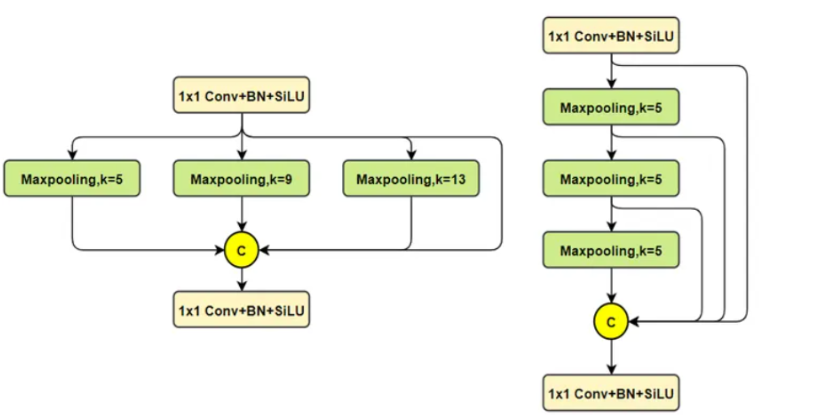

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

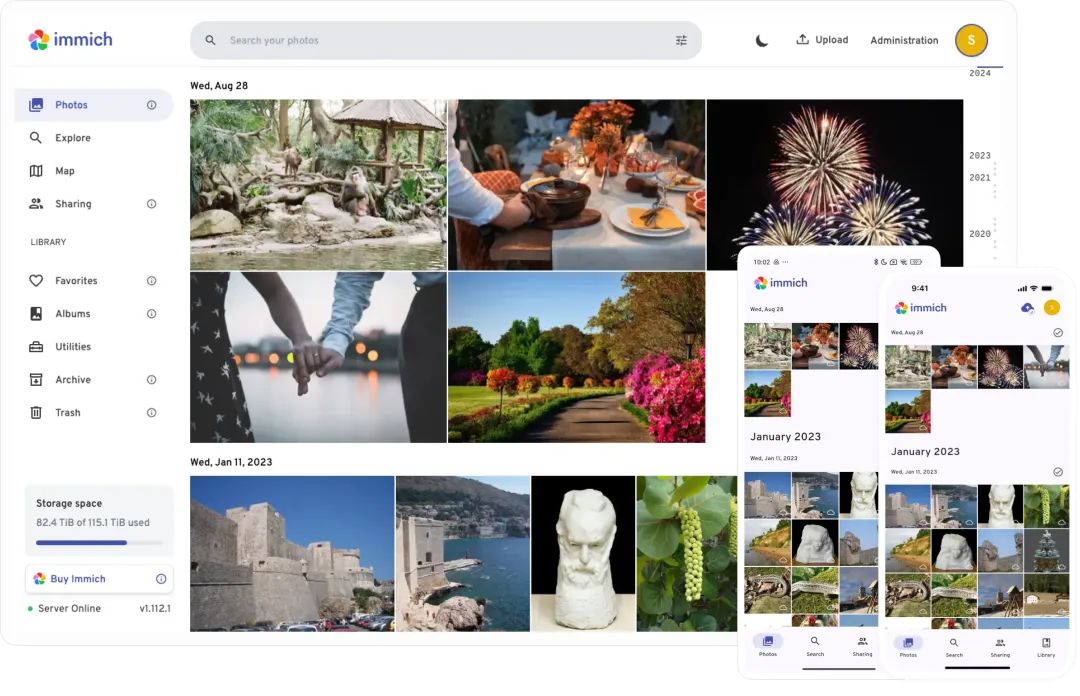

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

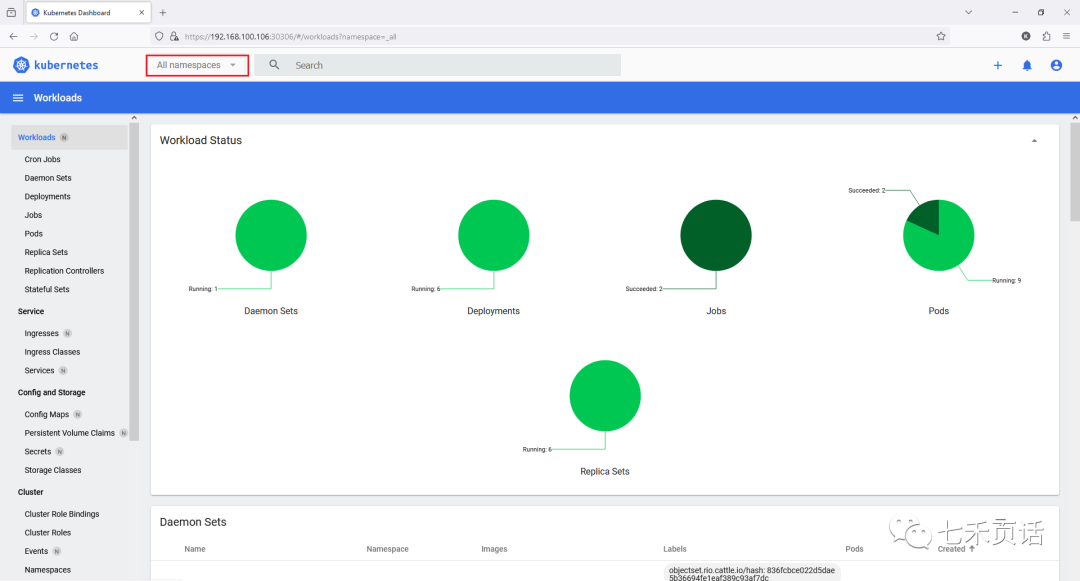

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

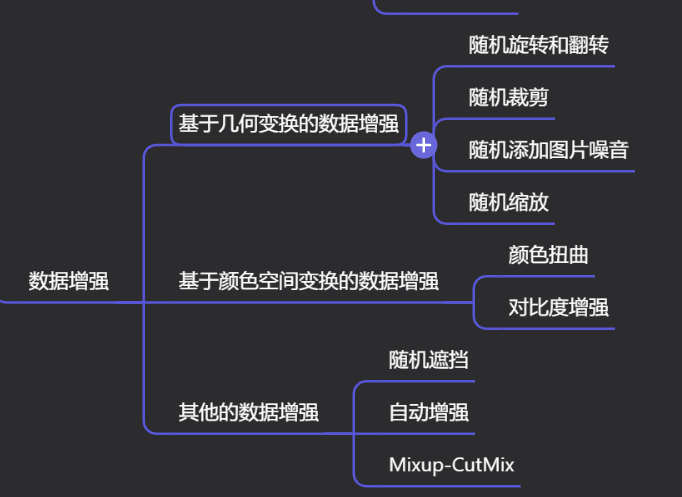

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

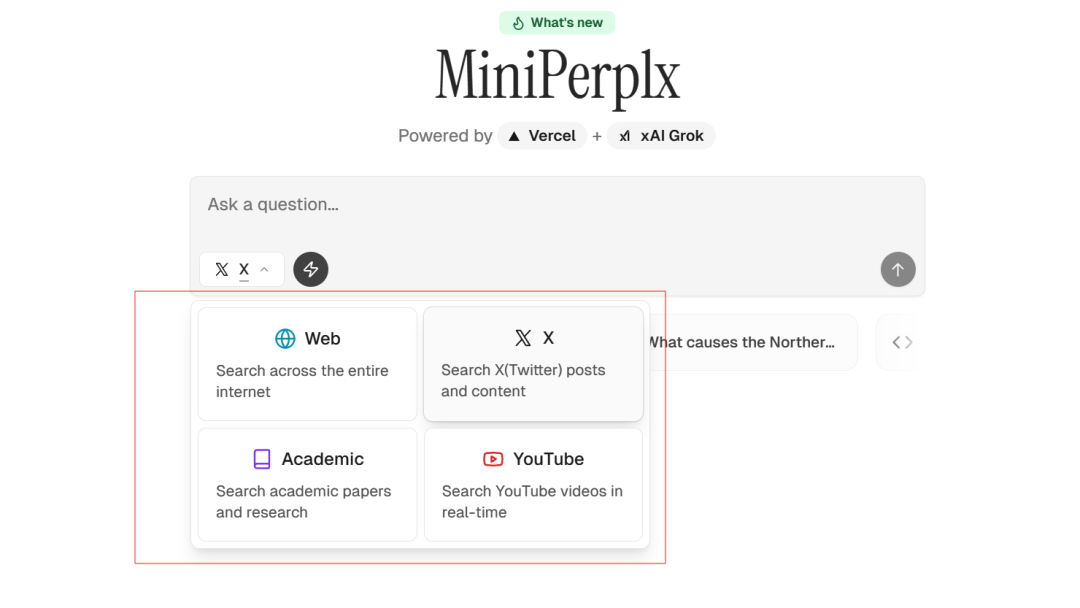

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

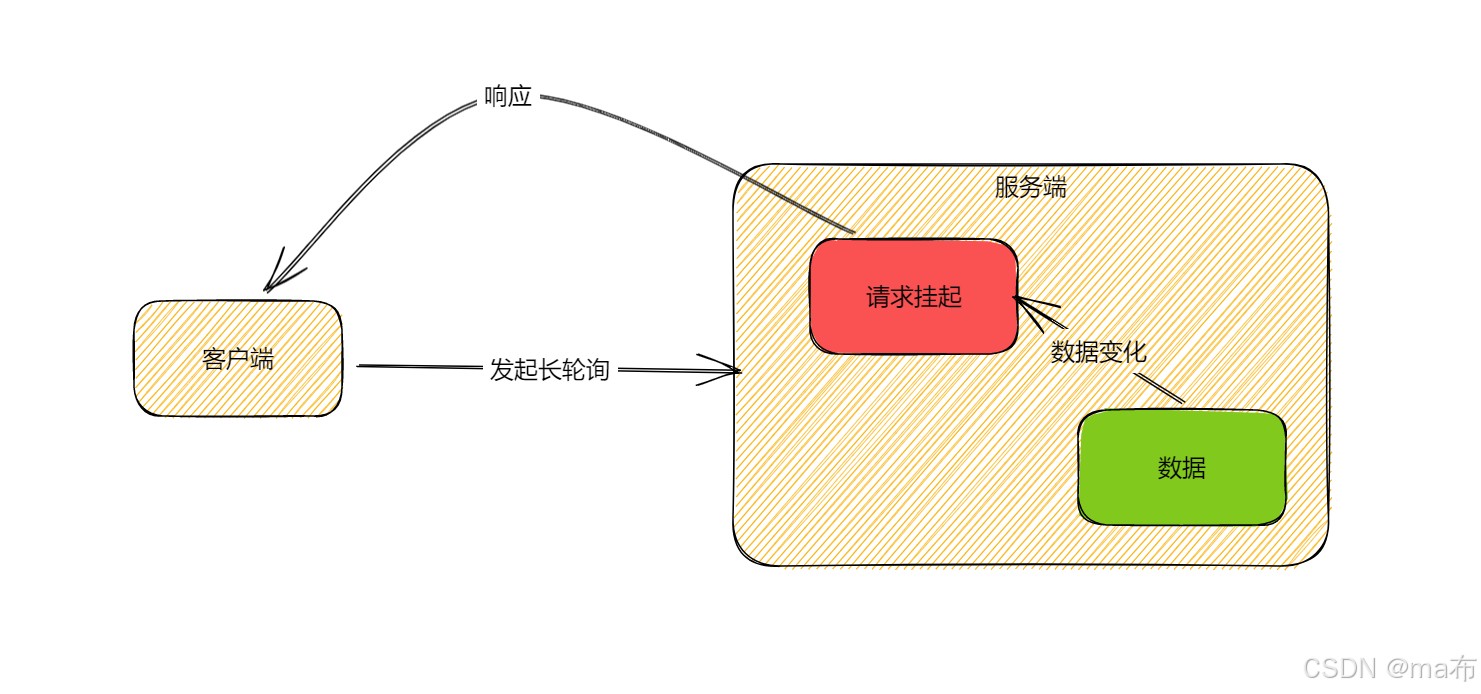

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

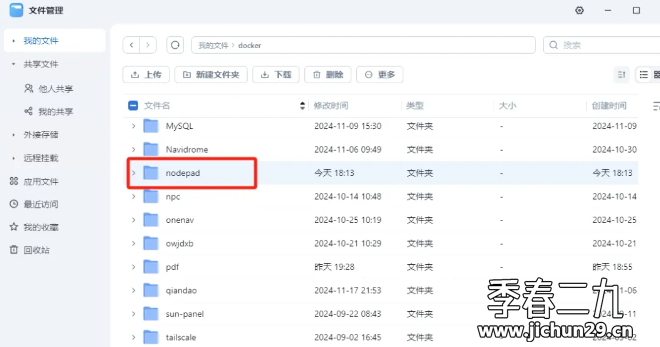

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

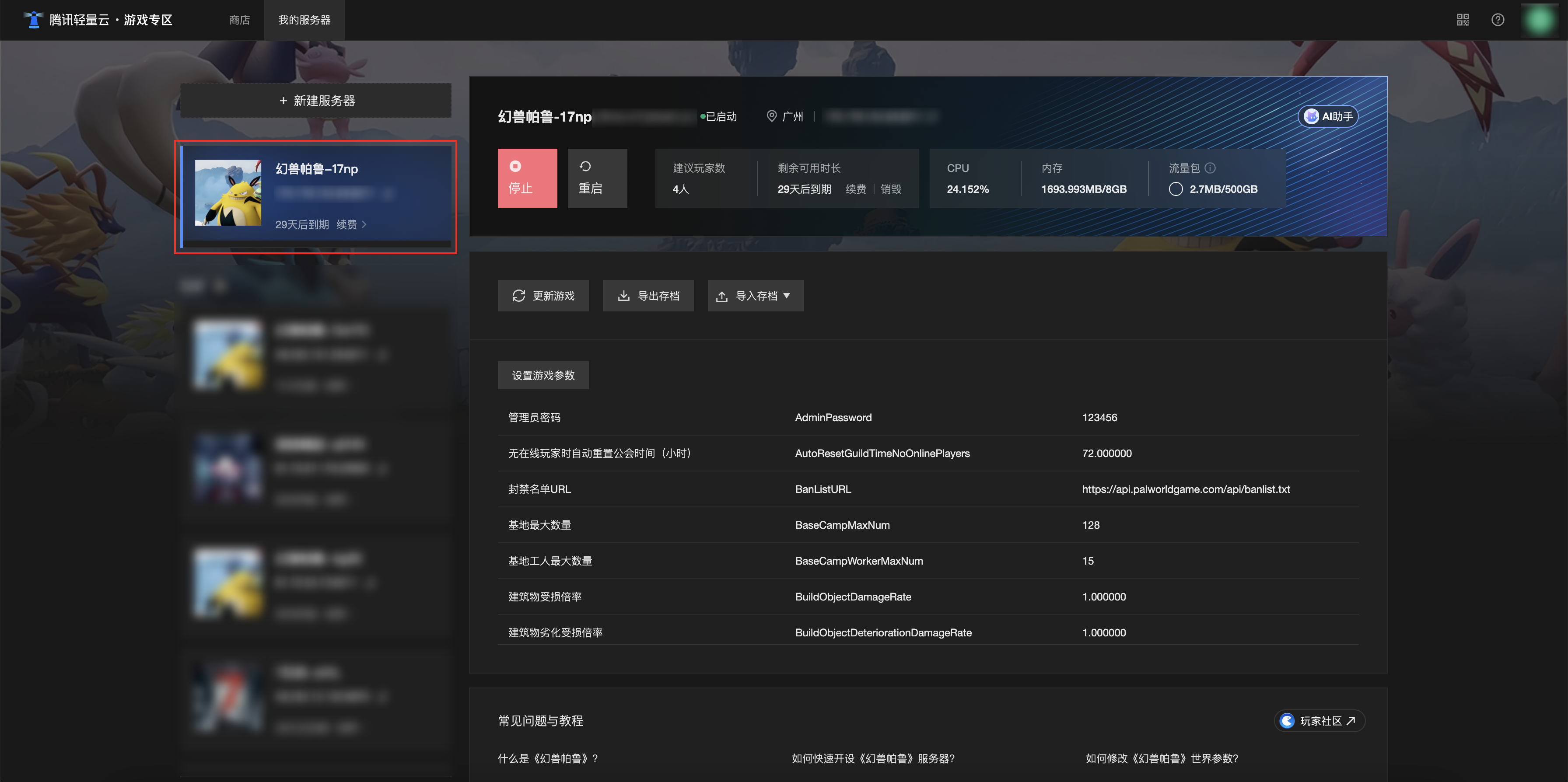

[Зона легкого облачного игрового сервера] Управление игровыми архивами