Три решения для высокоскоростной связи между отечественным ARM и недорогой FPGA на базе Allwinner T3/A40i

Предисловие

В последние годы, в связи с постоянным развитием новой инфраструктуры Китая и принятием инициативы «Сделано в Китае 2025», одному процессору ARM становится все труднее соответствовать функциональным требованиям промышленных объектов, особенно в сфере энергетики, промышленного контроля, интеллектуальных медицинских и других систем. другие отрасли, которым обычно требуется архитектура процессора ARM + FPGA для реализации определенных функций, таких как многоканальный/высокоскоростной сбор данных AD, многоканальные сетевые порты, многоканальные последовательные порты, многоканальный/высокоскоростной параллельный ввод данных. /DO, высокоскоростная параллельная обработка данных и т. д.

Итак, давайте сначала посмотрим на преимущества архитектуры ARM+FPGA?

ARM:Богатые ресурсы интерфейса、Низкое энергопотребление, хорошее отображение мультимедиа、Логическое управление и т.д.

FPGA:Специализируется на многоканальном или высокоскоростномADколлекция、Расширение интерфейса、высокоскоростная передача сигнала、Высокоскоростная параллельная обработка данных и т.д.

Таким образом, архитектура ARM+FPGA может обеспечить комплексные сравнительные преимущества в производительности, стоимости, энергопотреблении и т. д. ARM и FPGA могут выполнять свои собственные задачи, каждая из которых использует уникальные преимущества исходной архитектуры, а также могут взаимодействовать друг с другом. для решения более сложных задач.

Для более дискретных приложений ARM+FPGA, которые не чувствительны к стоимости и требуют высокой скорости передачи данных, обычно используется интерфейс связи PCIe. Однако в чувствительных к стоимости сценариях с дискретными ARM+FPGA интерфейс связи PCIe приводит к тому, что стоимость чипов FPGA остается высокой.

Для многих отраслей промышленности, таких как энергетика, энергетика и промышленное управление, действительно необходимо решение с конкурентоспособной производительностью и стоимостью. Требуется обеспечить высокоскоростную связь между ARM и FPGA, а также достичь оптимальной стоимости, и это так. лучше всего основываться на отечественном решении.

На фоне такого спроса компания Chuanglong Technology предлагает три решения для высокоскоростной связи на базе отечественного ARM и недорогой FPGA.

* Знакомство с аппаратной платформой (Allwinner Technology T3/A40i)

Chuanglong Technology TLT3-EVM/TLA40i-EVM — это 4-ядерная промышленная оценочная плата ARM Cortex-A7, разработанная на базе процессора Allwinner T3/A40i. Каждое ядро имеет основную частоту до 1,2 ГГц. Оно состоит из базовой платы и процессора Allwinner T3/A40i. оценочная базовая плата . T3 и A40i совместимы по контактам.

Оценочная плата имеет богатые интерфейсные ресурсы, включая два сетевых порта, два CAN, два USB, два RS485 и другие коммуникационные интерфейсы, встроенные модули Bluetooth, WIFI, 4G (дополнительно), а также ЖК-дисплей MIPI, LVDS LCD и TFT LCD, HDMI. OUT, CVBS OUT, CAMERA, LINE IN, H/P OUT и другие аудио- и видеомультимедийные интерфейсы с поддержкой двухэкранного дифференциального дисплея, Mali400 MP2 Графический процессор, аппаратное кодирование видео H.264 1080P @ 45 кадров в секунду, аппаратное декодирование видео H.264 1080P @ 60 кадров в секунду и поддержка интерфейса запоминающего устройства SATA.

Основная плата использует 100% отечественные компоненты и была проверена профессиональной компоновкой печатной платы, а также испытаниями при высоких и низких температурах. Она стабильна и надежна и может использоваться в различных промышленных условиях. Большинство компонентов оценочной платы используют отечественные решения, что позволяет пользователям быстро проводить оценку решения продукта и предварительное исследование технологии.

*Официальный вход для покупок в торговом центре:https://tronlong.tmall.com

В этой статье в основном представлены три высокоскоростных коммуникационных решения Quanzhi Technology T3/A40i и Ziguang Tongchuang PGL25G/Xilinx Spartan-6 на основе SPI, SDIO и CSI. Максимальная скорость связи может достигать 55,1 МБ/с.

Чтобы упростить описание, в основном тексте приведены только выдержки из описания функций программы и результатов испытаний. Для получения подробной документации по разработке отсканируйте QR-код в конце текста для загрузки.

Примечание. В настоящее время компания Chuanglong Technology выпустила национальное интегрированное промышленное базовое решение T3/A40i+PGL25G со 100% степенью локализации (разъемы также производятся внутри страны).

Рисунок 3. T3/A40i+PGL25G — промышленная базовая плата национального производства.

(Коэффициент локализации 100%)

1 случай spi_rw

1.1 Описание случая

Функция корпуса: в основном демонстрирует связь SPI между процессором T3/A40i (ARM Cortex-A7) и PGL25G/Spartan-6 (FPGA).

Сторона ARM реализует функцию SPI Master.

а. Откройте узел устройства SPI, например: /dev/spidev0.0.

б. Используйте ioctl для настройки шины SPI, например полярности и фазы шины SPI, скорости передачи данных, длины слова данных и т. д.

c. Выберите режим: однолинейный или двухлинейный. Когда шина SPI находится в двухпроводном режиме, передача данных осуществляется в однопроводном режиме, а прием данных — в двухпроводном режиме.

d. Отправка данных на шину SPI и чтение данных с шины SPI. (Примечание. Если размер одной передачи данных превышает 64 байта, драйвер автоматически включит функцию передачи DMA.)

e. Распечатайте тарифы на отправку и получение.

f. Проверьте данные чтения и записи, а затем распечатайте коэффициент ошибок по битам.

Реализуйте функцию SPI подчиненного устройства на стороне FPGA.

a.FPGA сохраняет данные размером 2 КБ, отправленные мастером SPI, в BRAM.

б. Когда SPI Master инициирует чтение данных, FPGA считывает 2 КБ из BRAM и передает их SPI Master через шину SPI.

c. Когда шина SPI находится в двухпроводном режиме, прием данных поддерживает двухпроводный режим, но отправка данных не поддерживает двухпроводный режим.

Рисунок 4. Блок-схема программы на стороне ARM.

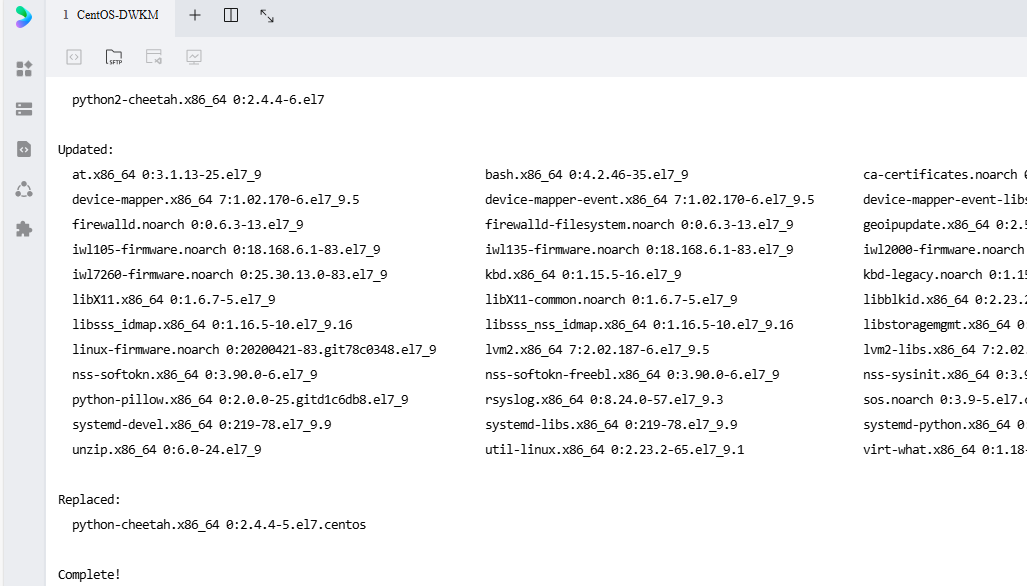

Результаты испытаний

(1) Однопроводной режим SPI

Согласно официальному паспорту, теоретическая максимальная тактовая частота связи по шине SPI составляет 100 МГц. Этот тест показывает, что тактовая частота связи по шине SPI составляет максимальное значение 100 МГц, а теоретическая скорость однопроводного режима SPI составляет: (100000000/1024/1024/8) МБ/с ≈ 11,92 МБ/с. Измеренная скорость записи в однострочном режиме SPI составляет: 10,924 МБ/с, а скорость чтения в однострочном режиме SPI: 10,924 МБ/с.

(2) Двухпроводной режим SPI

Согласно официальному паспорту, теоретическая максимальная тактовая частота связи по шине SPI составляет 100 МГц. В этом тесте указано, что тактовая частота связи по шине SPI составляет максимальное значение 100 МГц, тогда теоретическая скорость однолинейного режима SPI равна: (100000000/1024/1024/8) МБ/с ≈ 11,92 МБ/с; тогда теоретическая скорость; Скорость двухлинейного режима SPI составляет: (100000000/1024/1024/4)МБ/с ≈ 23,84МБ/с. Измеренная скорость записи в однострочном режиме SPI составляет 11,631 МБ/с, а скорость чтения в двухстрочном режиме SPI — 17,807 МБ/с.

2 случай rt_spi_rw

2.1 Описание случая

Функция случая: на основе системы Linux-RT демонстрирует связь SPI (однопроводной режим) между T3/A40i (ARM Cortex-A7) и процессором PGL25G/Spartan-6 (FPGA).

Сторона ARM реализует функцию SPI Master.

а. Откройте узел устройства SPI. Например: /dev/spidev0.0.

б. Используйте ioctl для настройки шины SPI. Например, полярность и фаза шины SPI, скорость связи, длина слова данных и т. д.

c. Создайте поток в реальном времени.

d. Отправка данных на шину SPI и чтение данных с шины SPI.

e. Распечатайте скорость отправки и получения, а также время передачи.

f. Проверьте данные чтения и записи, а затем распечатайте коэффициент ошибок по битам.

Реализуйте функцию SPI подчиненного устройства на стороне FPGA.

a.FPGA сохраняет данные размером 2 КБ, отправленные мастером SPI, в BRAM.

б. Когда SPI Master инициирует чтение данных, FPGA считывает 2 КБ из BRAM и передает их SPI Master через шину SPI.

Рисунок 5. Блок-схема программы на стороне ARM.

Результаты испытаний

(1) Метод без опроса

Согласно официальному паспорту, теоретическая максимальная тактовая частота связи по шине SPI составляет 100 МГц. Этот тест показывает, что тактовая частота связи шины SPI составляет максимальное значение 100 МГц, а теоретическая скорость составляет: (100000000/1024/1024/8) МБ/с ≈ 11,92 МБ/с. Измеренное минимальное время передачи 4-байтовых данных составляет 49 мкс, максимальное время — 662 мкс, среднее время — 227 мкс, скорость записи — 0,017 МБ/с, скорость чтения — 0,017 МБ/с.

(2) Метод опроса

Согласно официальному паспорту, теоретическая максимальная тактовая частота связи по шине SPI составляет 100 МГц. Этот тест показывает, что тактовая частота связи шины SPI составляет максимальное значение 100 МГц, а теоретическая скорость составляет: (100000000/1024/1024/8) МБ/с ≈ 11,92 МБ/с. Измеренное минимальное время, необходимое для передачи 4-байтовых данных, составляет 14 мкс, максимальное время — 59 мкс, среднее время — 14 мкс, скорость записи — 0,239 МБ/с, скорость чтения — 0,239 МБ/с.

3 случая sdio_test

3.1 Описание случая

Функция корпуса: демонстрирует связь SDIO между процессором T3/A40i (ARM Cortex-A7) и PGL25G/Spartan-6 (FPGA).

Внедрить SDIO на стороне ARM Основная функция

а. Откройте узел устройства SDIO, например: /dev/generic_sdio0.

б. Отправить данные на шину SDIO и прочитать данные с шины SDIO.

c. Распечатайте тарифы на отправку и получение.

d Проверьте данные чтения и записи, а затем распечатайте коэффициент ошибок по битам.

Реализовать SDIO на стороне FPGA Ведомая функция

a.FPGA и SDIO Данные размером 2 КБ, отправленные Master, сохраняются в BRAM.

б. Когда SDIO Master инициирует чтение данных, FPGA считывает 2 КБ из BRAM и передает их SDIO Master через шину SDIO.

Рисунок 6. Блок-схема программы на стороне ARM.

Результаты испытаний

В этом тесте тактовая частота связи по шине SDIO составляет 25 МГц (до 50 МГц), тогда теоретическая скорость передачи данных составляет: (25 x 4/8) МБ/с = 12,5 МБ/с. Измеренная скорость записи составила 5,113 МБ/с, скорость чтения — 5,440 МБ/с, а коэффициент ошибок по битам — 0,0%.

4 случай csi_test

4.1 Описание случая

Функция случая: демонстрирует случай связи CSI между процессором T3/A40i (ARM Cortex-A7) и PGL25G/Spartan-6 (FPGA).

Боковые функции ARM

а) На основе подсистемы Linux V4L2.

б) Собрать указанные данные о номере кадра через шину CSI.

в) Подсчитайте общее время, затраченное на выполнение задания.

г) Распечатайте среднюю скорость сбора данных и проверьте данные последнего кадра изображения.

Боковые функции FPGA

а) Запишите тестовые данные (0x00 ~ 0xFF) в FIFO.

б) Считать данные из FIFO, отправить их на сторону ARM через шину CSI в строковом и кадровом формате с разрешением 1024х512.

Используемая шина CSI — CSI0, максимальное поддерживаемое разрешение — 1080P30, разрядность данных — 8 бит. Функциональная блок-схема и блок-схема программы показаны на рисунке ниже.

Рисунок 7 Функциональная блок-схема

Рисунок 8. Блок-схема программы на стороне ARM.

Результаты испытаний

Сторона FPGA устанавливает CSI_PCLK на 65 МГц, а тактовый сигнал FIFO_WR_CLK для записи тестовых данных в FIFO устанавливается на 59 МГц. Поскольку стороне FPGA необходимо записать данные в FIFO, а затем прочитать их из FIFO перед отправкой, интервал между каждой строкой и каждым кадром будет зависеть от скорости записи FIFO, поэтому фактическая теоретическая полоса пропускания связи CSI должна быть: (59 МГц x 8 бит / 8) МБ/с = 59 МБ/с. Измеренная скорость передачи составляет 55,1 МБ/с, а коэффициент битовых ошибок — 0,0%.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

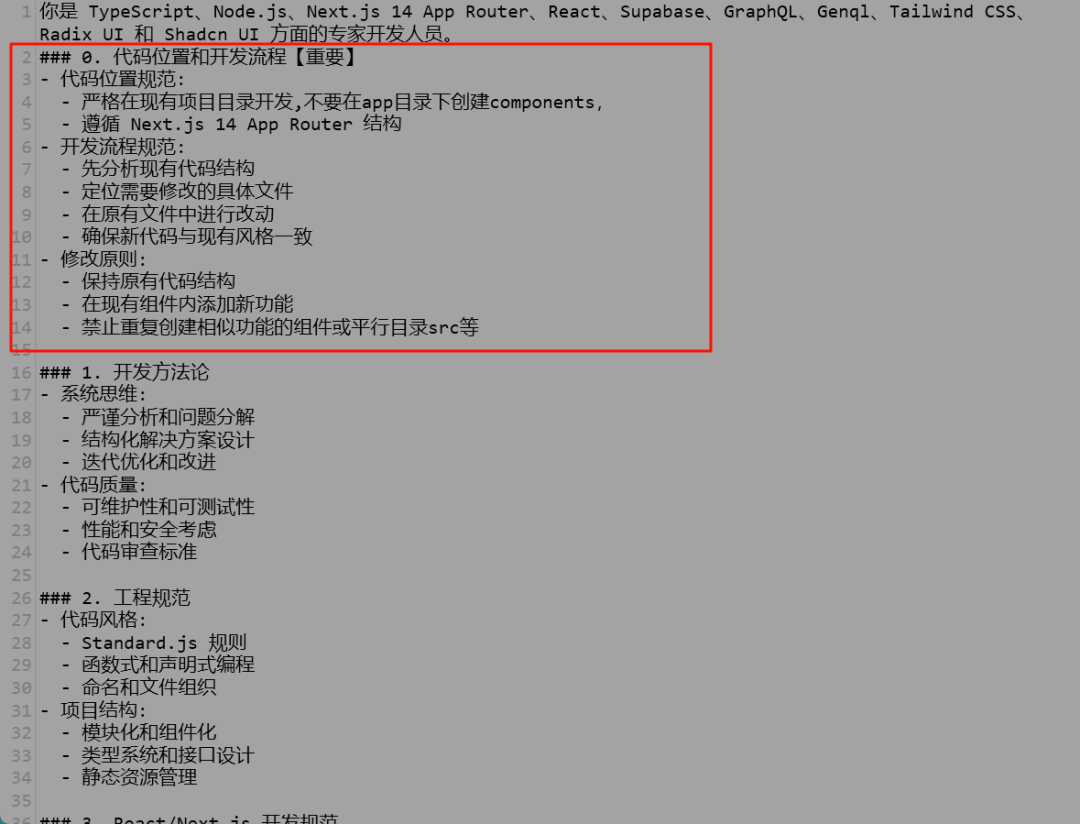

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

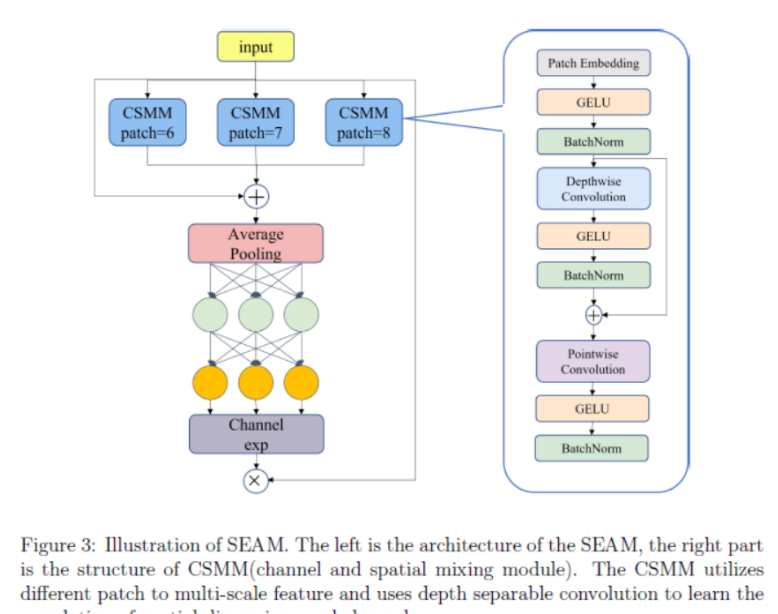

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

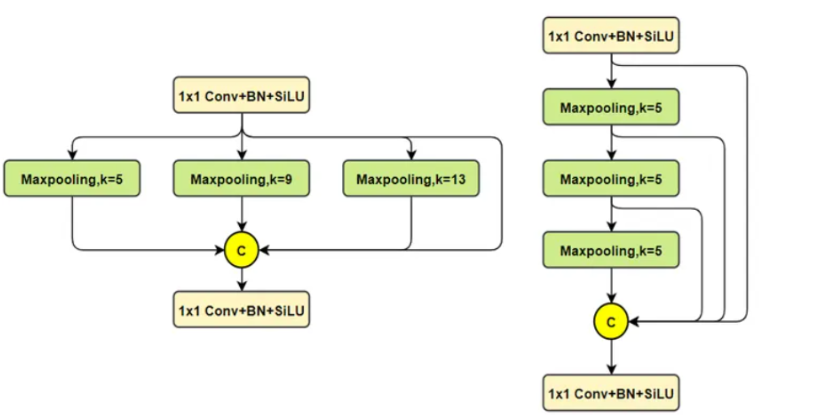

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

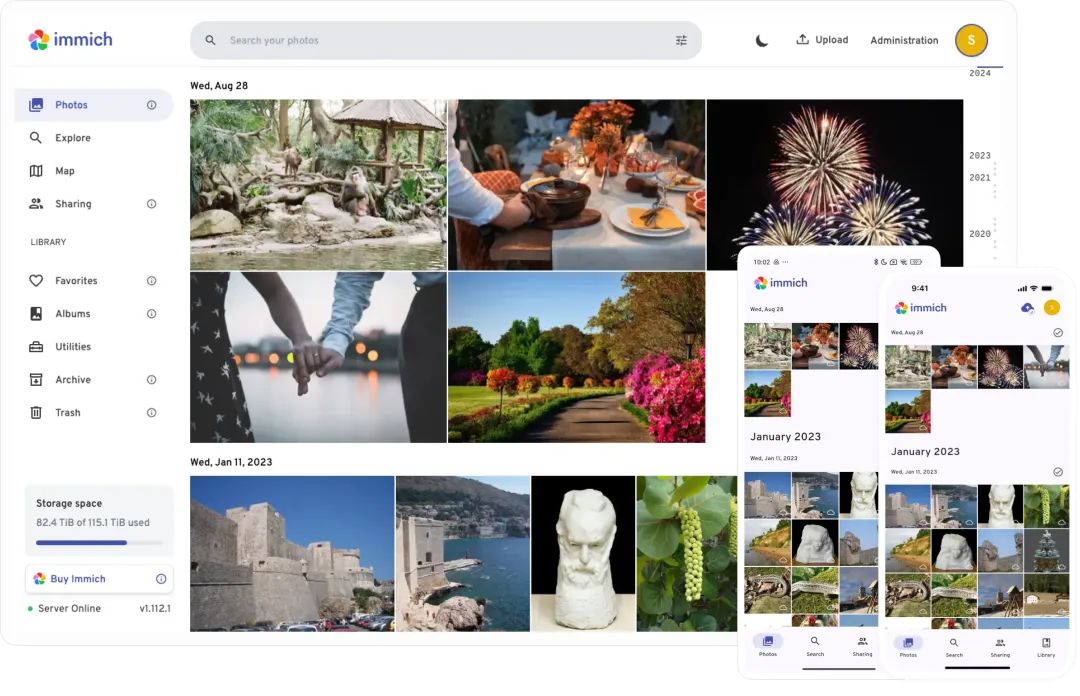

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

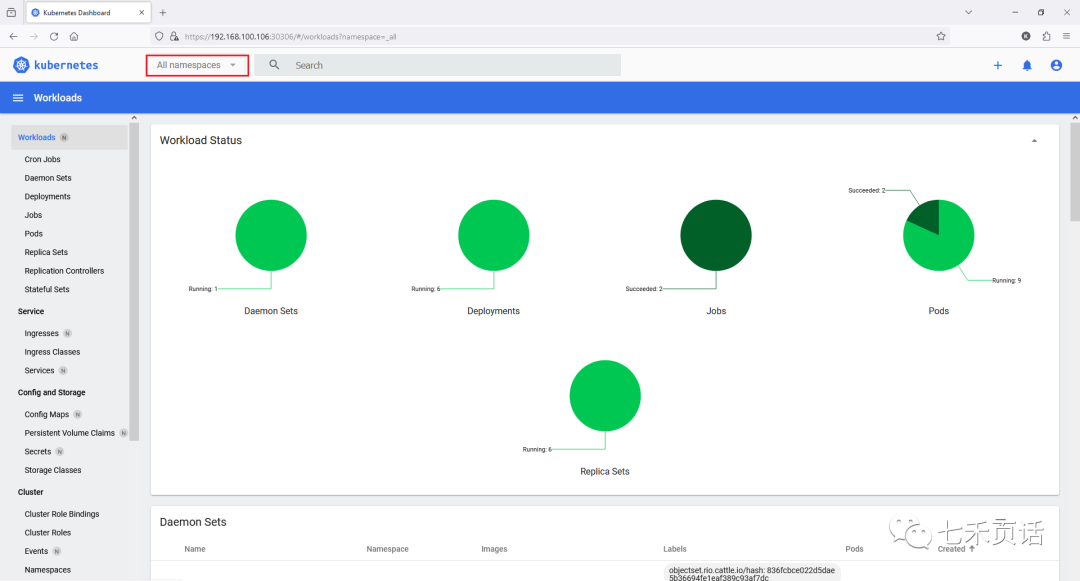

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

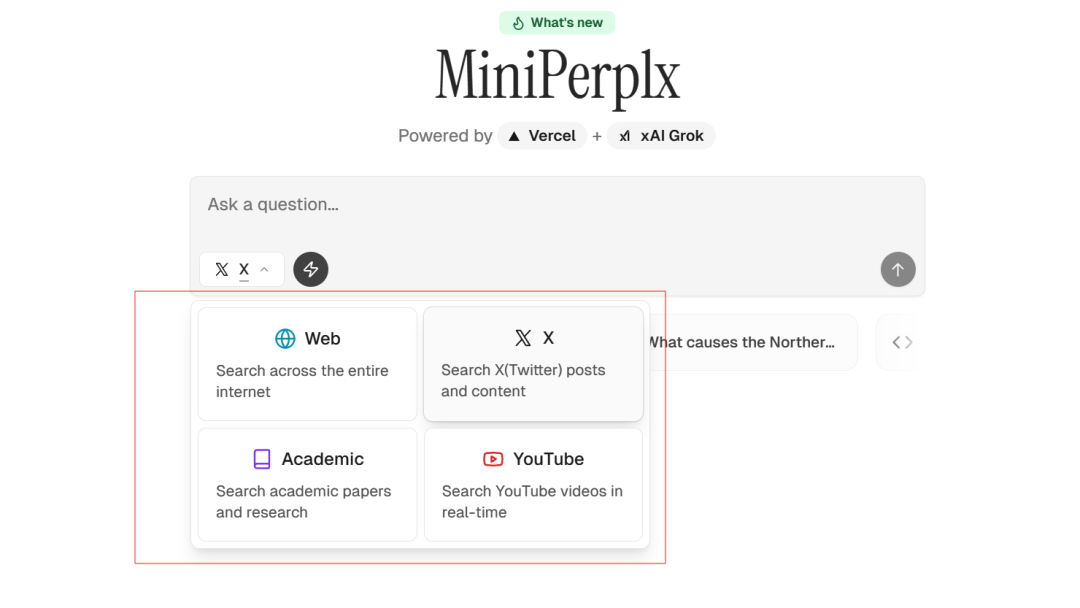

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

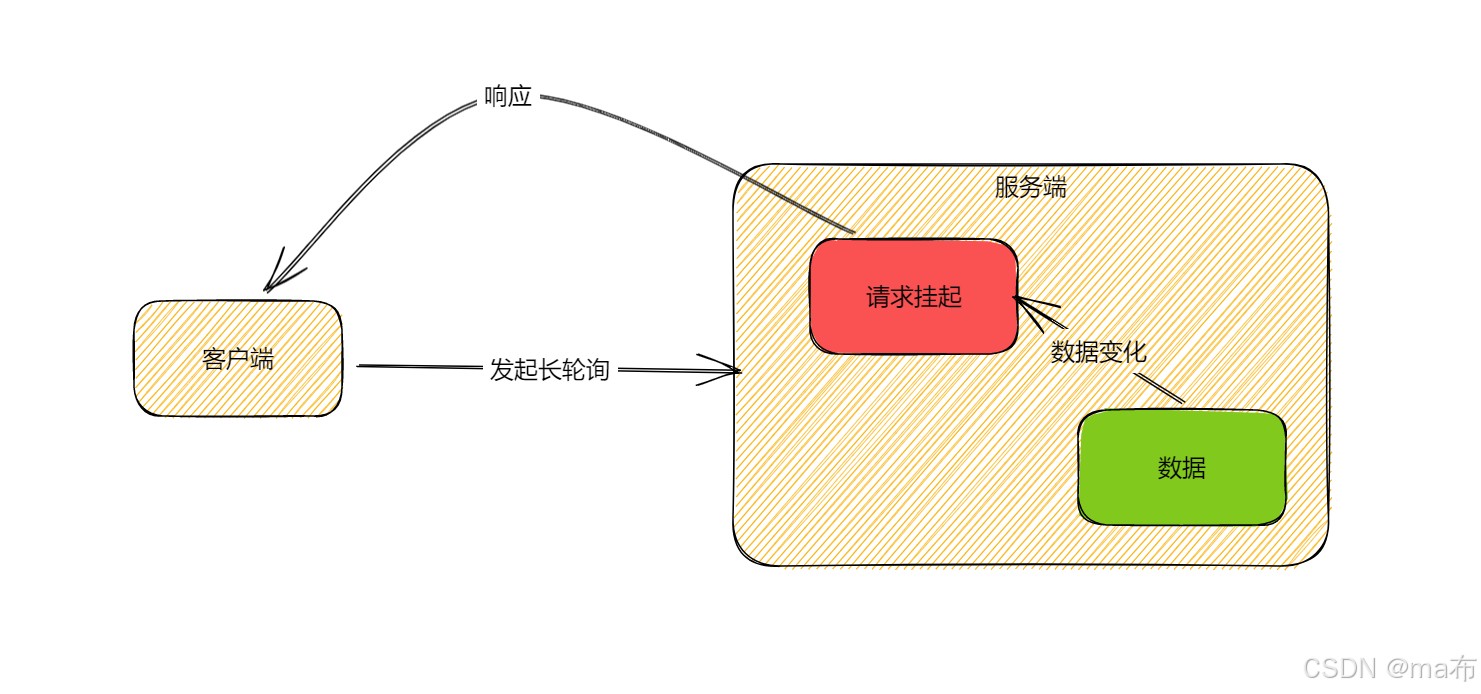

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

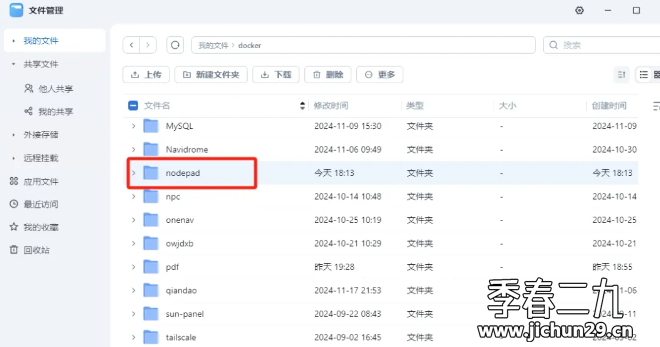

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

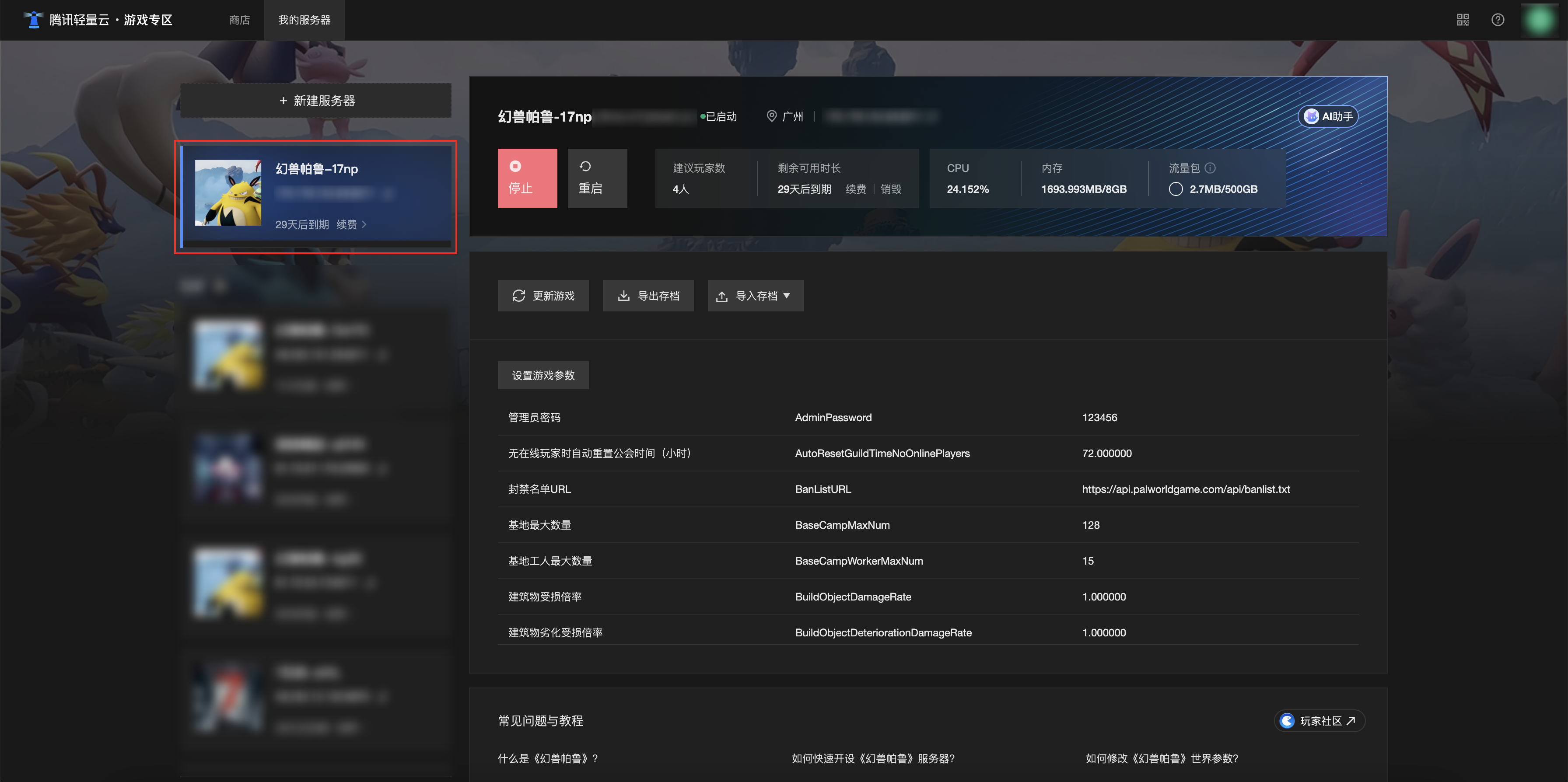

[Зона легкого облачного игрового сервера] Управление игровыми архивами