Шлейфовое тестирование связи Ethernet

Чипы PHY обычно имеют функцию обратной связи для тестирования канала связи PHY. В этой статье в основном обсуждаются функции обратной связи трех часто используемых микросхем PHY, а также используется микросхема Broadcom B50612D для выполнения тестирования обратной связи PHY.

1 функция обратной связи обычных PHY-чипов

1.1 KSZ9031

Микросхема KSZ9031 поддерживает следующие два режима шлейфа:

- Местная (цифровая) петля, местная (цифровая) петля

- Удаленная (аналоговая) петля, удаленная (аналоговая) петля

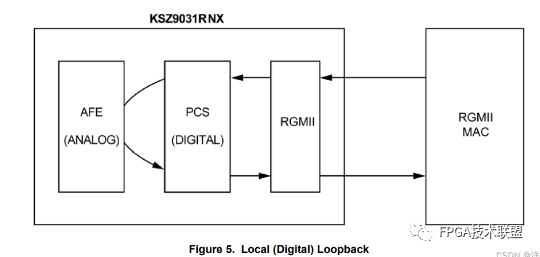

Локальный (цифровой) режим шлейфа используется для проверки канала передачи и приема данных между MAC и PHY, поддерживая три скорости (10/100/1000 Мбит/с) и полнодуплексный режим. Кадры Ethernet отправляются со стороны MAC, а чип PHY отправляет полученные кадры обратно на сторону MAC.

Путем настройки регистров 00h и 09h включается функция локального (цифрового) шлейфа. Значения и значения настроек регистра следующие:

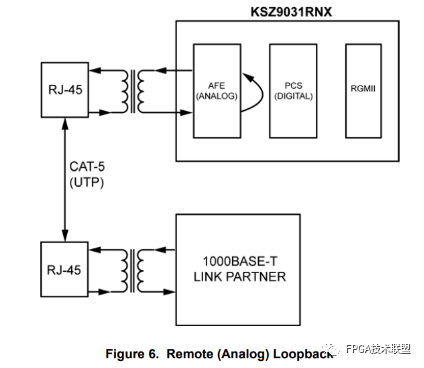

Режим удаленного (аналогового) шлейфа используется для проверки работы дифференциальных линий, разъемов RJ45 или кабелей Ethernet. Он поддерживает только полнодуплексный режим 1000M.

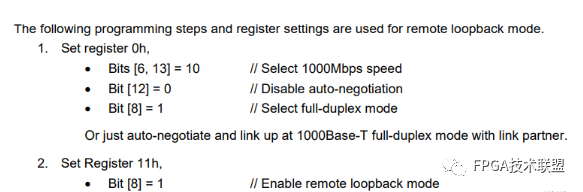

Включите функцию удаленного (аналогового) шлейфа, настроив регистры 00h и 11h. Настройки и значения регистров следующие:

1.2 RTL8211

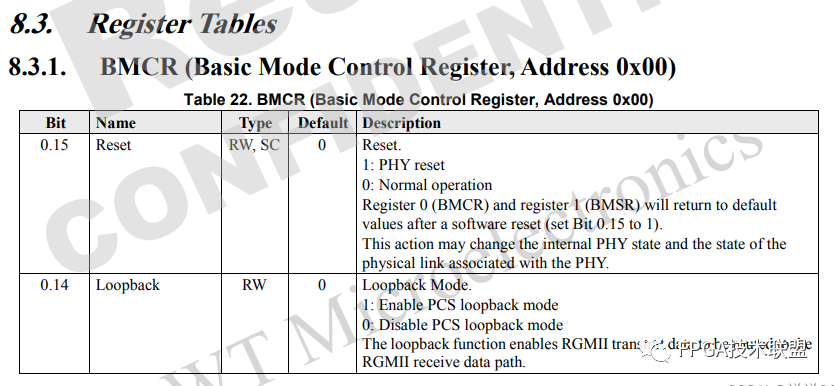

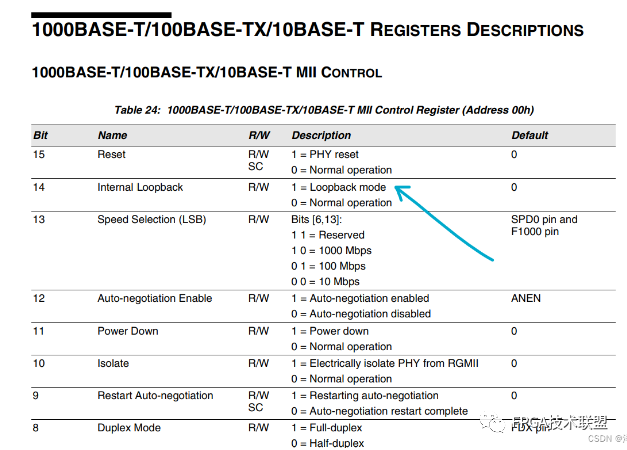

Микросхемы RTL8211Dx, RTL8211E(G) и RTL8211Fx поддерживают только режим шлейфа PCS, аналогичный локальному (цифровому) режиму шлейфа вышеупомянутой микросхемы KSZ9031, который включается путем настройки бита 14 регистра управления базовым режимом.

1.3 B50610/B50612

Микросхемы B50610 и B50612 поддерживают следующие три режима обратной связи:

- Режим внутренней петли, режим внутренней петли

- Режим внешней петли, режим внешней петли

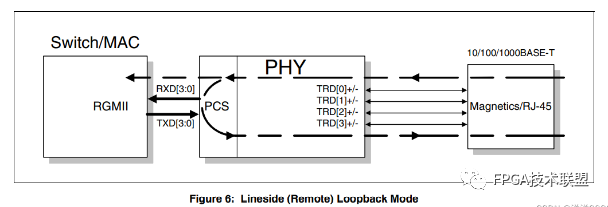

- Режим линейного (дистанционного) шлейфа, режим шлейфа линии

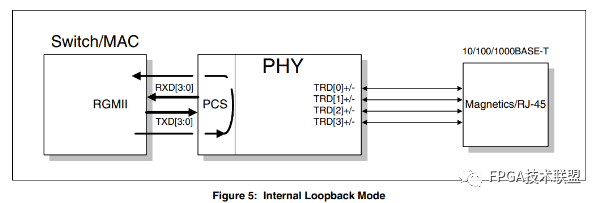

В режиме внутреннего шлейфа PHY отправляет пакет данных с терминала RGMII TXD обратно на терминал RGMII RXD. Дифференциальный терминал TRD± выводит состояние с высоким импедансом, и пакеты внешних данных будут игнорироваться. Этот режим аналогичен локальному (цифровому) режиму шлейфа микросхемы KSZ9031.

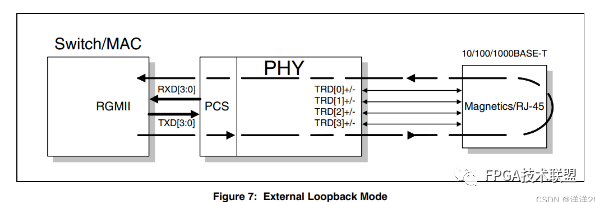

В режиме внешнего шлейфа пакеты, отправленные с MAC на PHY, проходят через разъем RJ45, повторно отправляются обратно на PHY и затем поступают на сторону MAC.

Режим линейного шлейфа в основном используется для проверки рабочего состояния интерфейса MDI. В этом режиме уровень PHY PCS можно настроить как выход с тремя состояниями, а также управлять концом RGMII RXD.

2 PHY-тест шлейфа

В этом тесте используется PHY-чип Broadcom B50612D, а режим шлейфа выбирает режим внутреннего шлейфа. Согласно руководству, чтобы включить функцию внутреннего шлейфа, вам необходимо настроить внутренний регистр PHY 00h и установить бит 14 в 1.

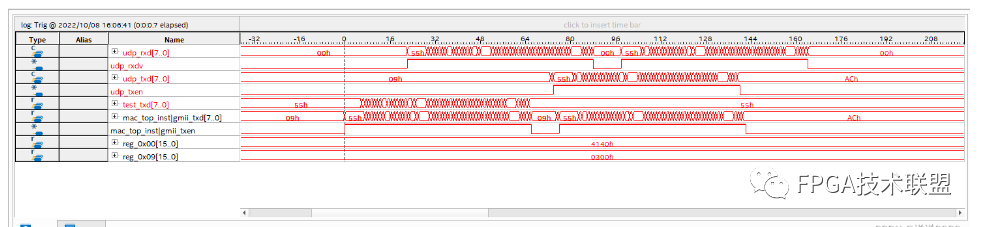

Процесс проверки внутреннего шлейфа выглядит следующим образом:

(1) FPGA генерирует тестовый кадр каждые 1 с и отправляет его на PHY;

(2) PHY получает тестовый кадр и передает его обратно в FPGA через порт RGMII RXD;

(3) FPGA получает тестовый кадр, анализирует и генерирует кадр ответа UDP;

(4) PHY получает кадр ответа UDP и снова передает его обратно в FPGA, но поскольку MAC-адреса удаленного конца и исходного конца были обменены, FPGA в это время не отвечает.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

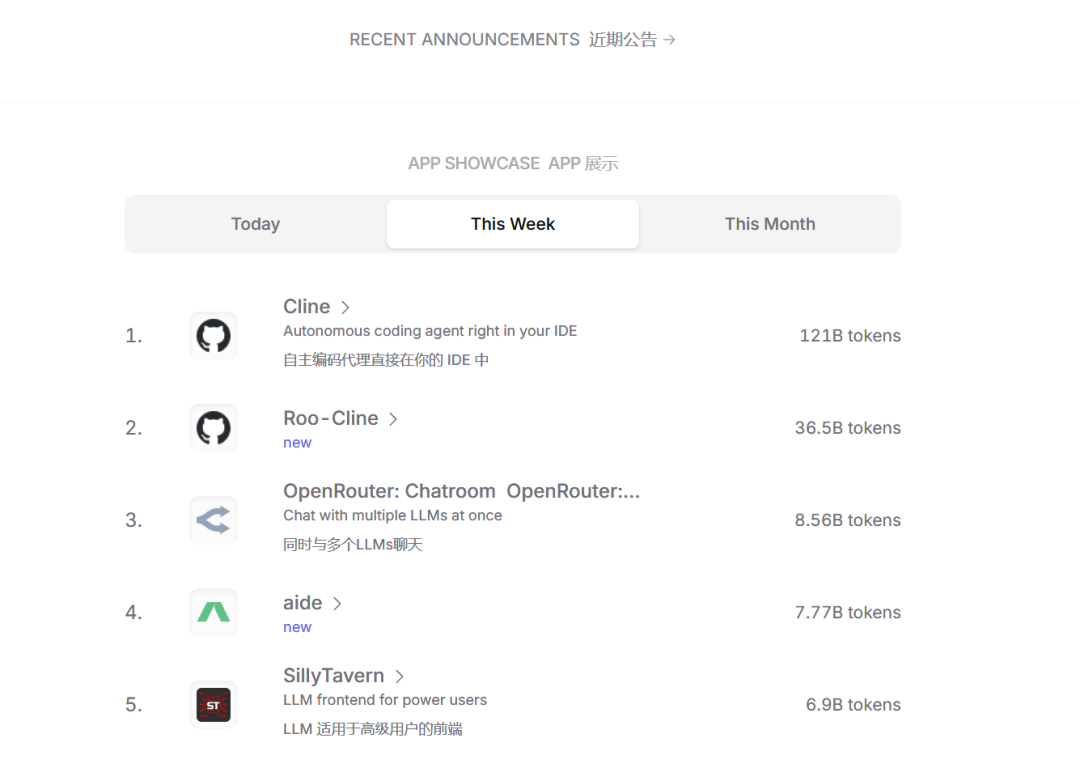

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

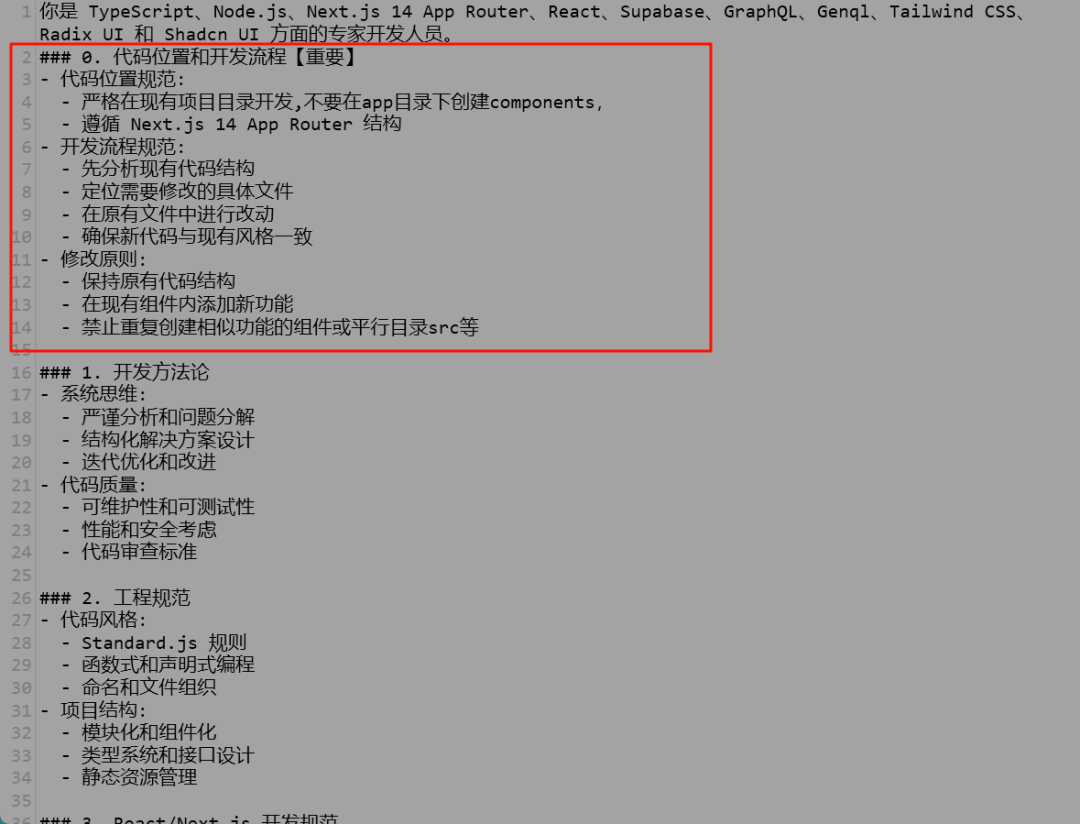

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

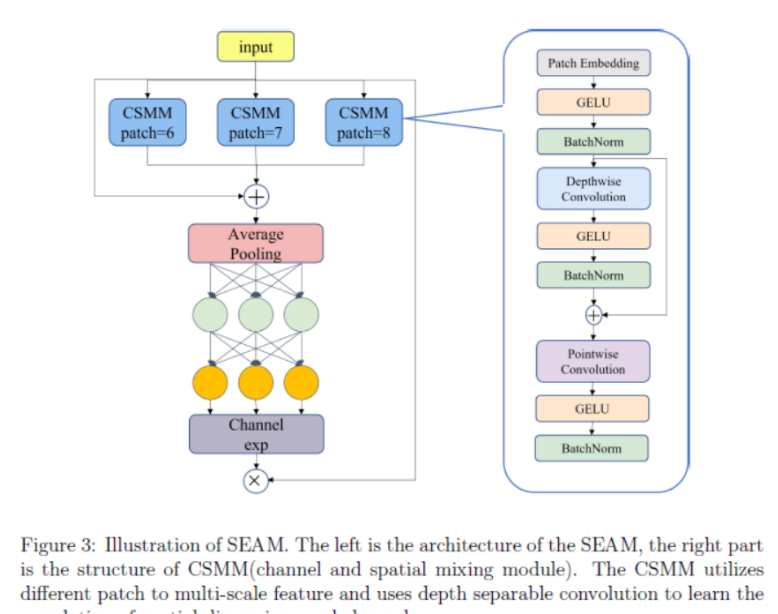

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

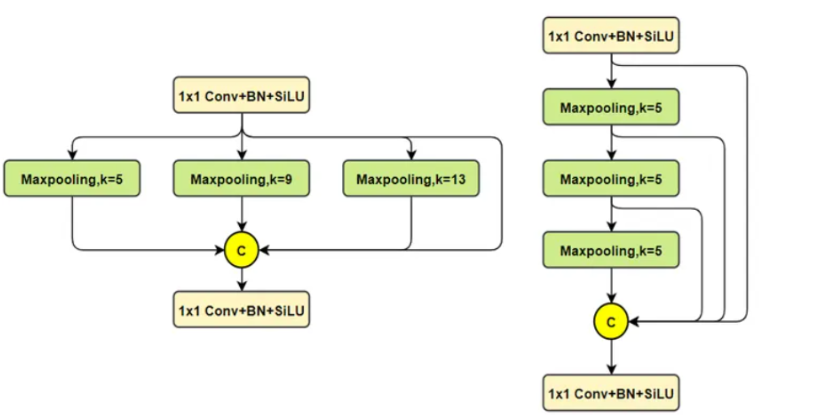

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

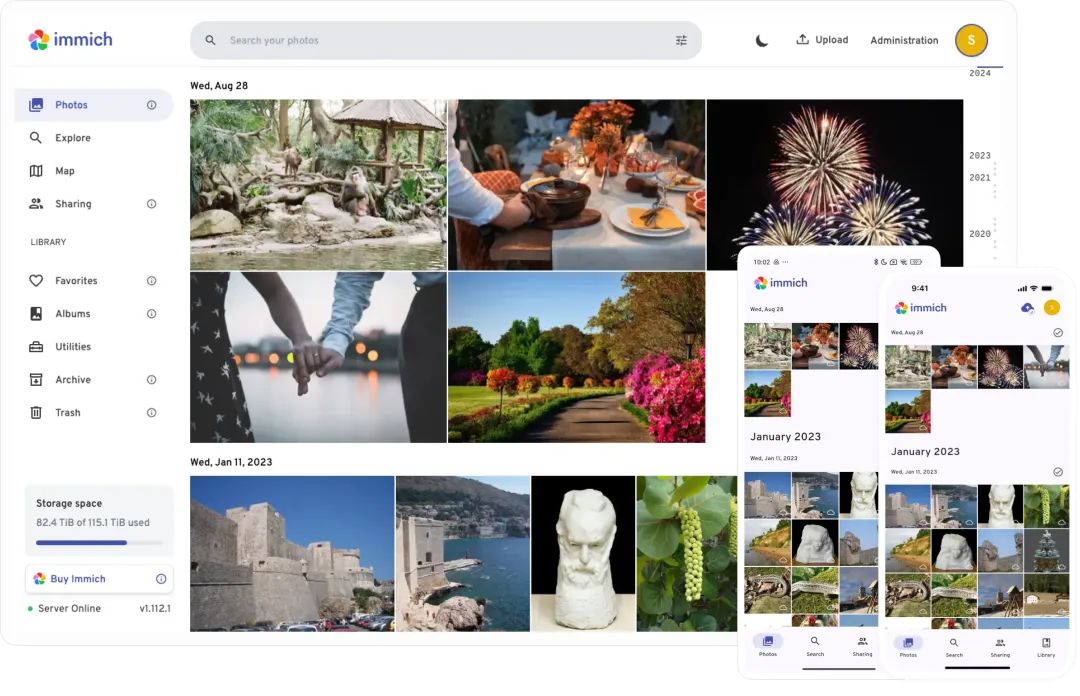

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

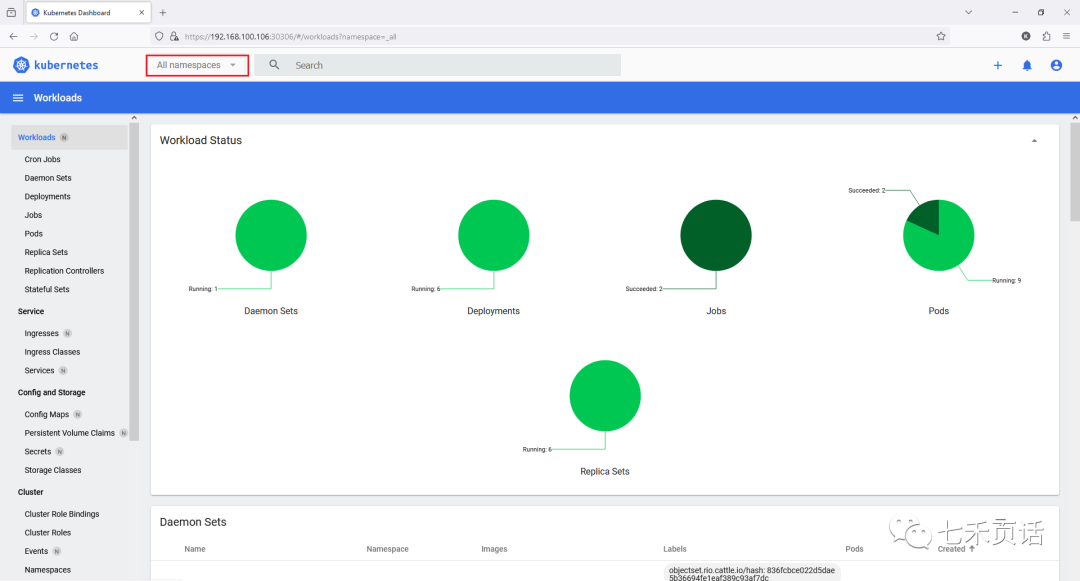

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

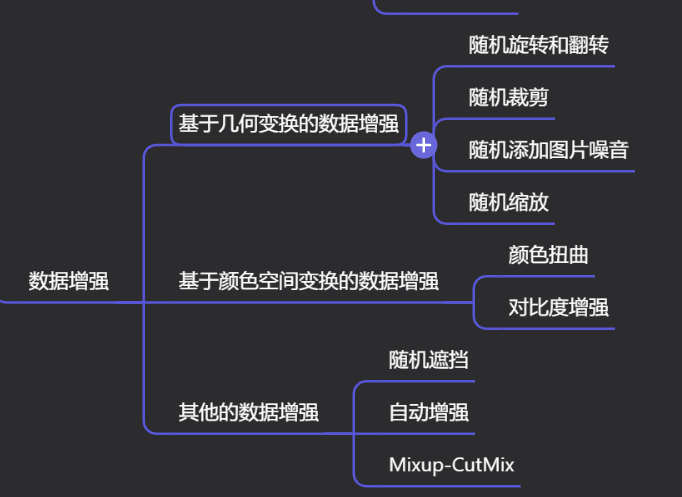

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

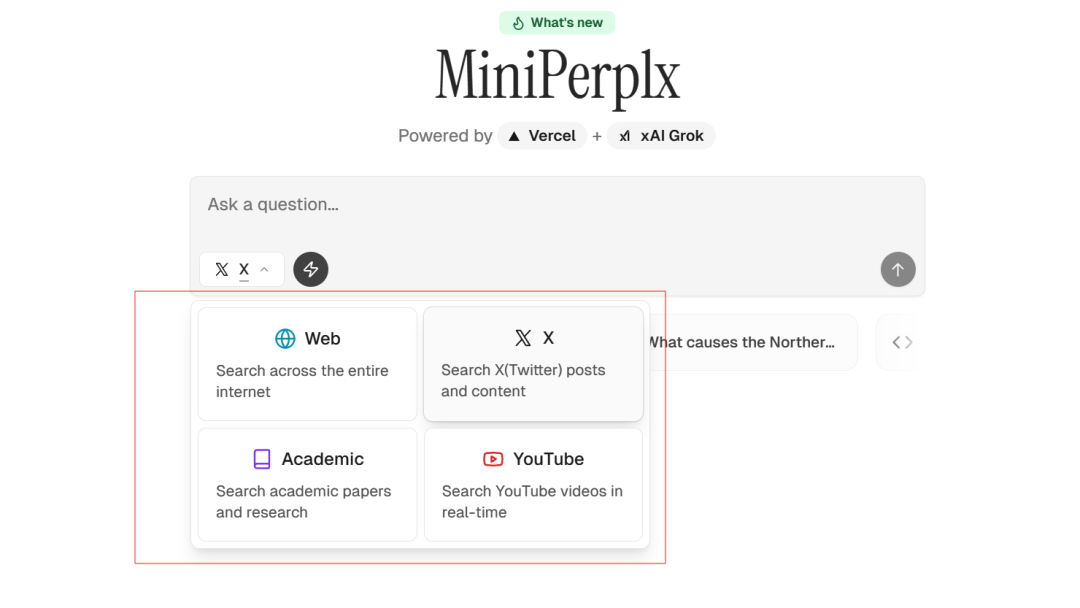

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

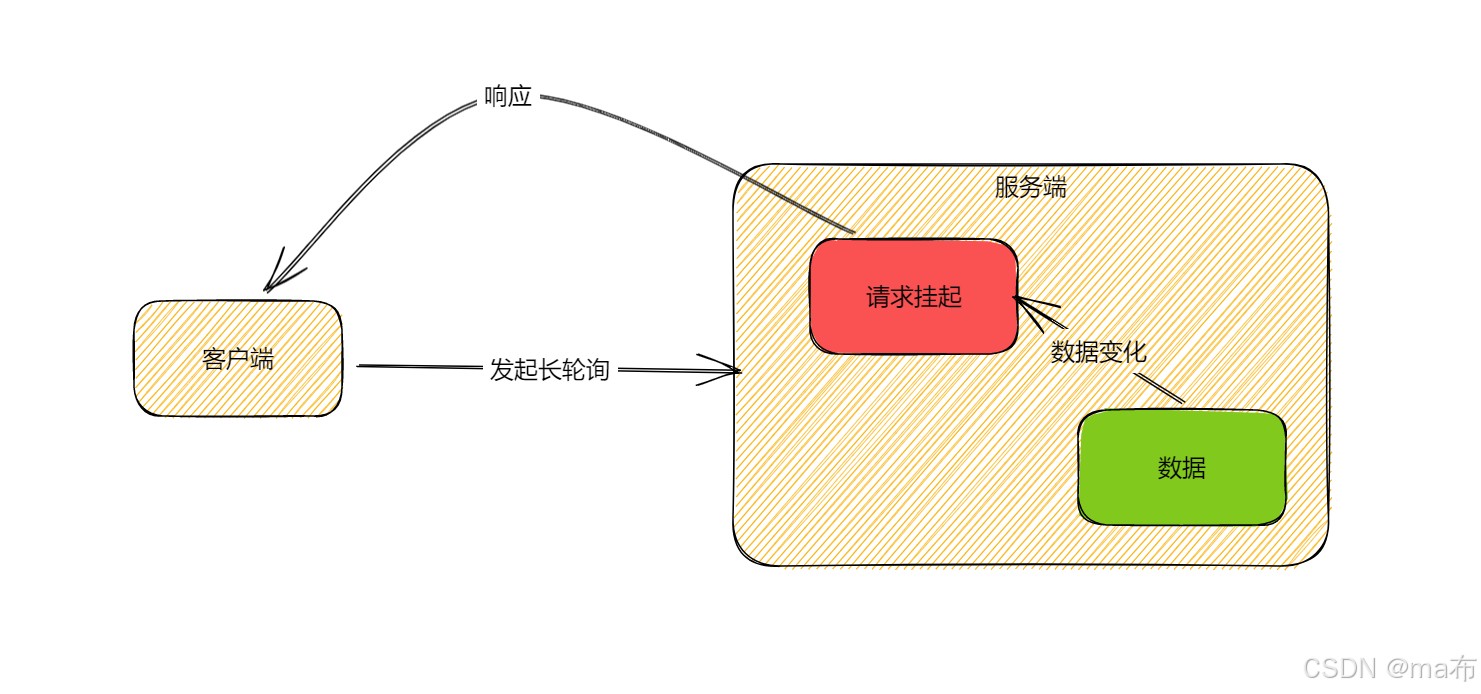

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

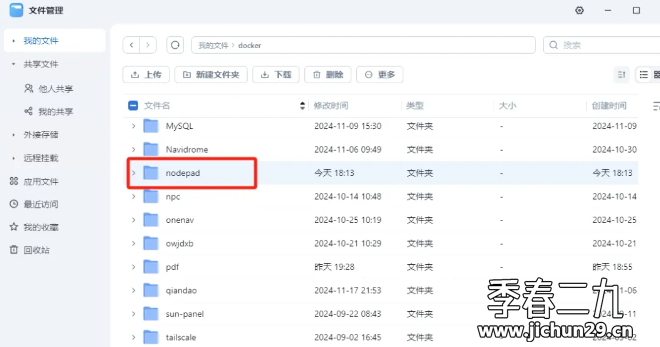

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

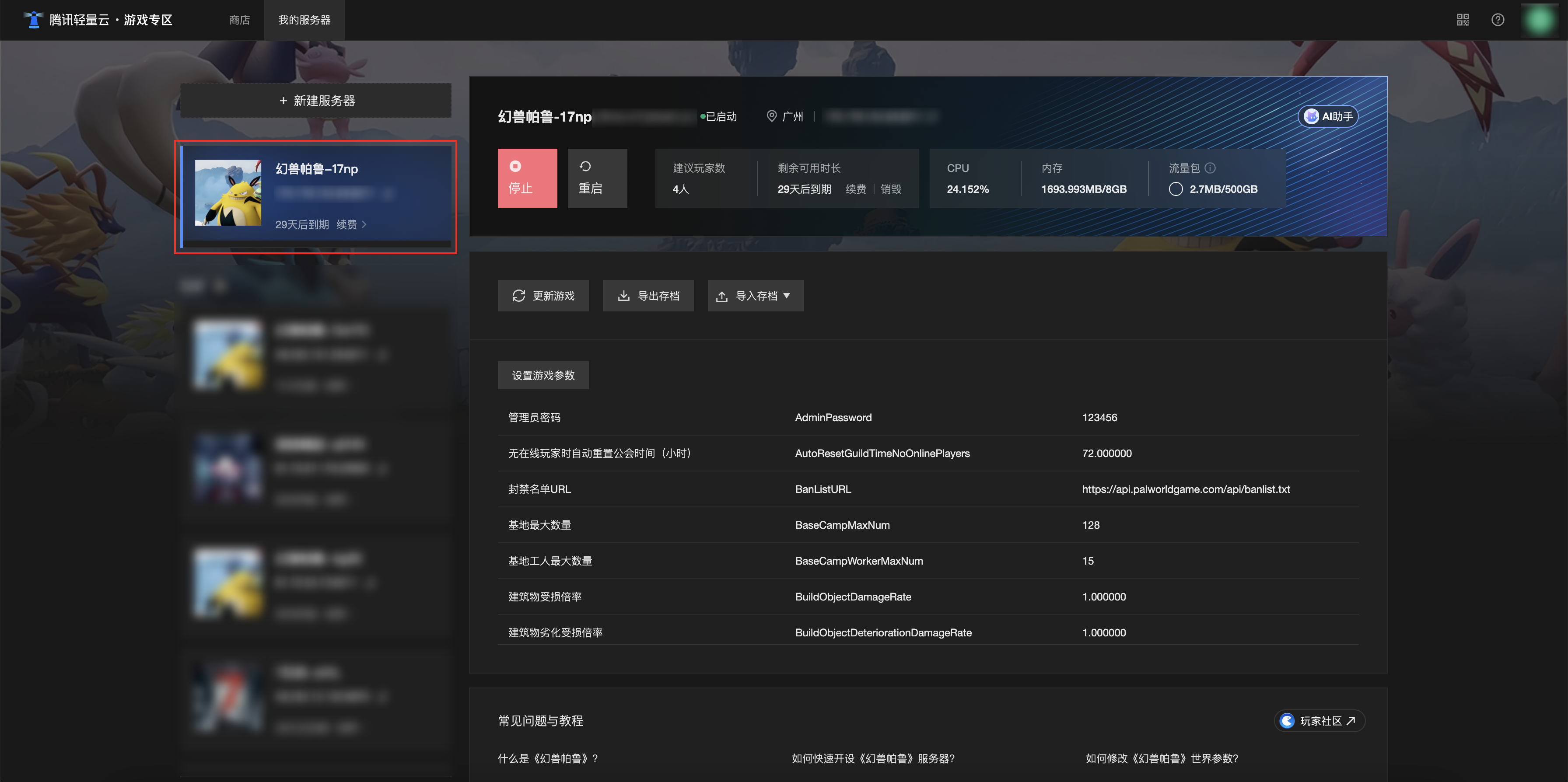

[Зона легкого облачного игрового сервера] Управление игровыми архивами