Самый мощный из выпущенных серверных чипов RISC-V: 4 нм, 192 ядра, производительность превосходит AMD Epyc 9754!

Согласно новостям от 9 ноября, компания Ventana Micro Systems, производитель серверных чипов RISC-V, представила на саммите RISC-V 2023 года свой серверный CPU-Veyron V2 второго поколения. Он имеет множество преимуществ в расширении инструкций, дизайне ядра и межсоединении. стандарты, технологические процессы и т. д. Он был полностью модернизирован, и официальные лица утверждают, что его производительность превосходит высокопроизводительный серверный чип AMD Epyc 9754, что делает его самым мощным серверным процессором RISC-V! Ventana также позволяет клиентам добавлять собственные ускорители в собственные схемы систем на кристалле (SoC).

Уже в декабре 2022 г.,VentanaКомпания выпустила первый в мире мобильный телефон на базеRISC-VархитектурныйсерверCPU——Veyron V1,Использование 5-нм техпроцесса,На основе собственной разработки Ventana высокой производительности RISC-ВЯдро.,8 проектирование сборочной линии,Поддержка внеочередного исполнения,Основная частота превышает 3 ГГц,До 16 Ядро на кластер,Мультикластерное масштабирование до 192ядерный,Имеет общий кэш L3 объемом 48 МБ.,Улучшенная защита от атак по побочным каналам, расширенная архитектура прерываний IOMMU (AIA), поддержка комплексных функций RAS, нисходящая производительность программного обеспечения.,Может удовлетворить различные потребности центров обработки данных. Говорят, что производительность может превзойти AMD EPYC 7763!

Согласно плану Ventana, Veyron V1 будет доступен во второй половине этого года, но пока ни один клиент не решился его принять. Возможно, именно поэтому Ventana так хочет выпустить Veyron V2.

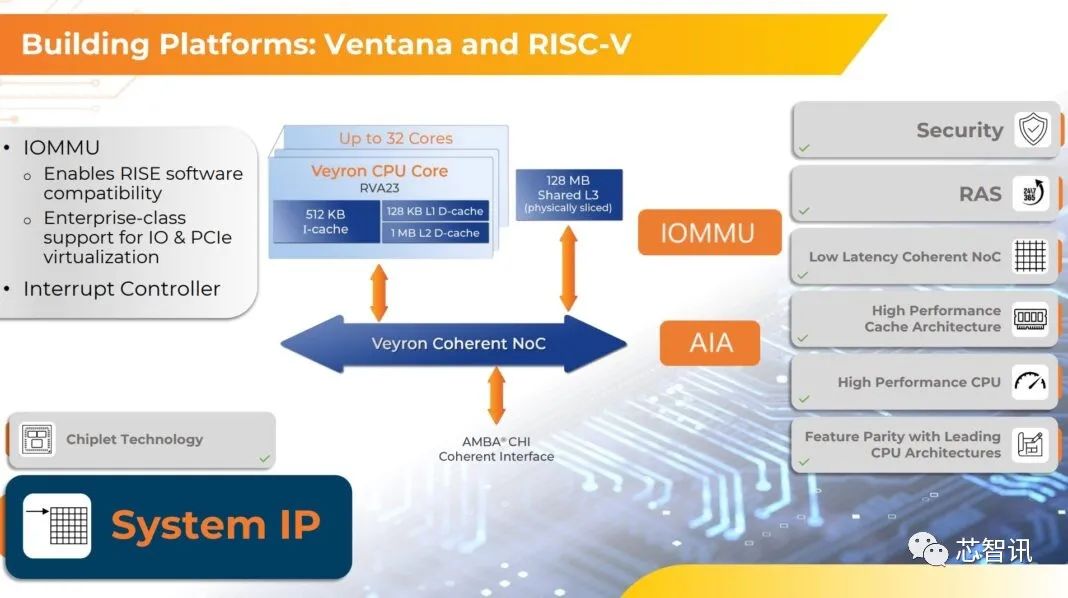

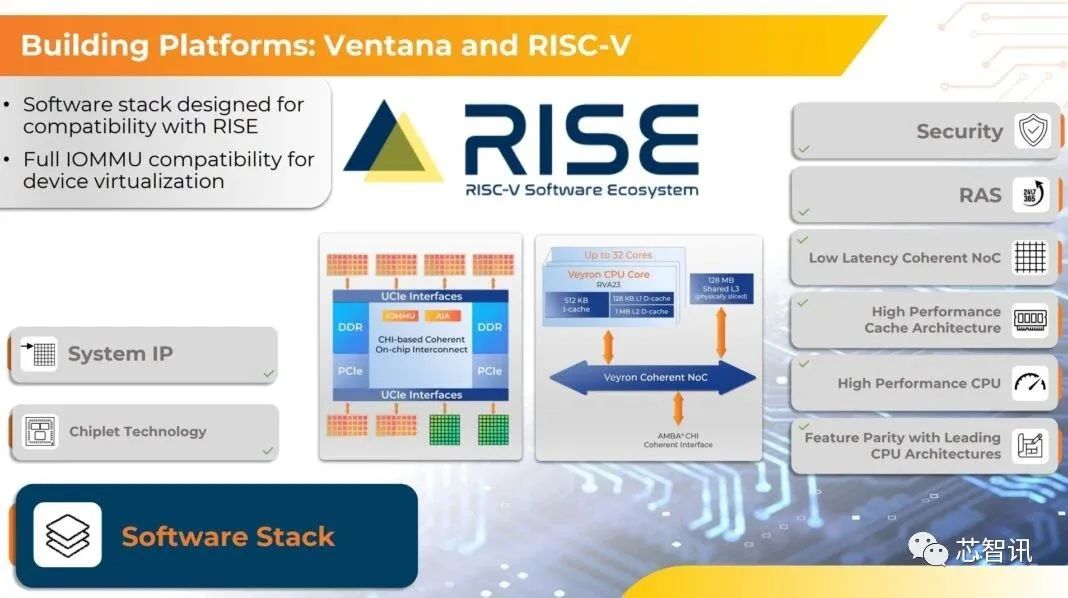

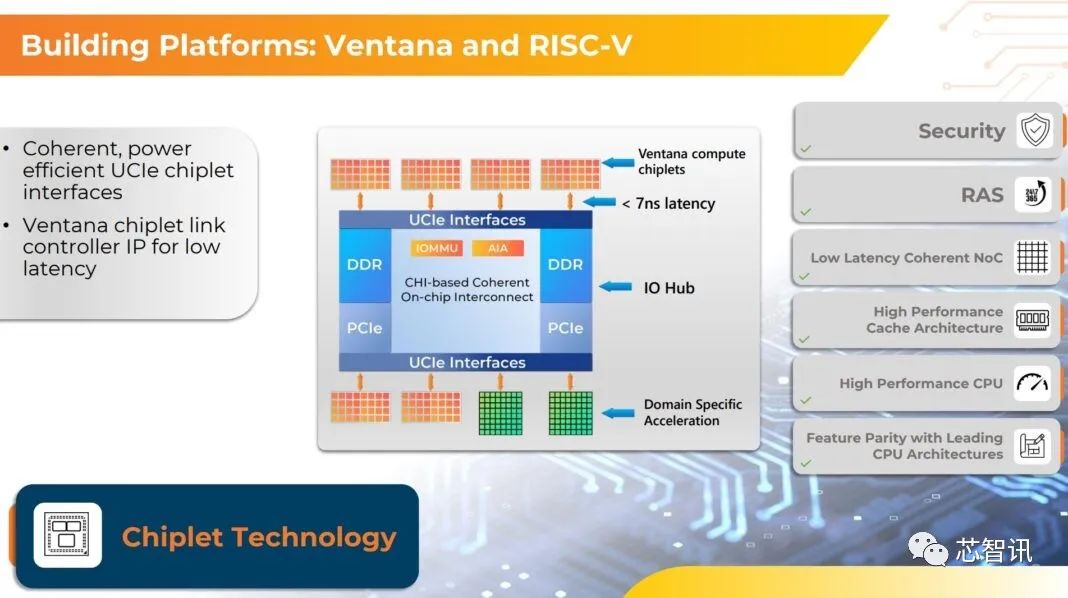

По словам вице-президента Ventana по маркетингу и продуктам Трэвиса Ланье, новый Veyron V2 будет включать в себя все обновления спецификации RISC-V, такие как набор функций RVA23, который является последним профилем набора команд RISC-V этого года и реализует RISC. -V Спецификация блока управления памятью ввода-вывода (IOMMU), а также поддержка стандарта межсоединений UCIe для небольших микросхем.

Ланье сказал, что ратификация спецификации IOMMU «является большим событием в мире RISC-V». «Каждый раз, когда у вас есть виртуальная машина и вам нужен прямой доступ к одному из устройств PCIe, вам не нужно выполнять все накладные расходы на программное обеспечение для ее переключения, поэтому это критически важная возможность для приложений центра обработки данных».

Veyron V2 также надеется, что его конструкция будет соответствовать стандарту RISC-V, поэтому поддержка RISE важна.

“Это такжеИнициатива экосистемы программного обеспечения RISC-V (RISE)Ключевые части совместимости,Это отраслевой проект,Направлен на создание необходимой экосистемы приложений на основе RISC-V. Далее Ланье пояснил.

Ventana также использует спецификацию векторного расширения RISC-V для добавления 512-битного векторного процессора к своему ядру, а также имеет матричные расширения AI. Ланье утверждает, что это будет «большим подспорьем для определенных рабочих нагрузок генеративного ИИ или вывода».

Кроме того, поддержка стандарта DSA и Chiplet UCIe позволяет быстрее производить микросхемы, а также позволяет клиентам добавлять FPGA, ускорители ASIC и т. д. Это повышает гибкость, но также снижает барьер для входа, поскольку позволяет создавать пакеты с использованием меньших блоков IP с использованием UCIe и концентраторов ввода-вывода.

Соучредитель и генеральный директор Ventana Баладжи Бакта также заявил на саммите RISC-V, что клиенты Ventana могут использовать ее интеллектуальную собственность и другую интеллектуальную собственность для создания потенциальных проектов процессоров на Veyron V2.

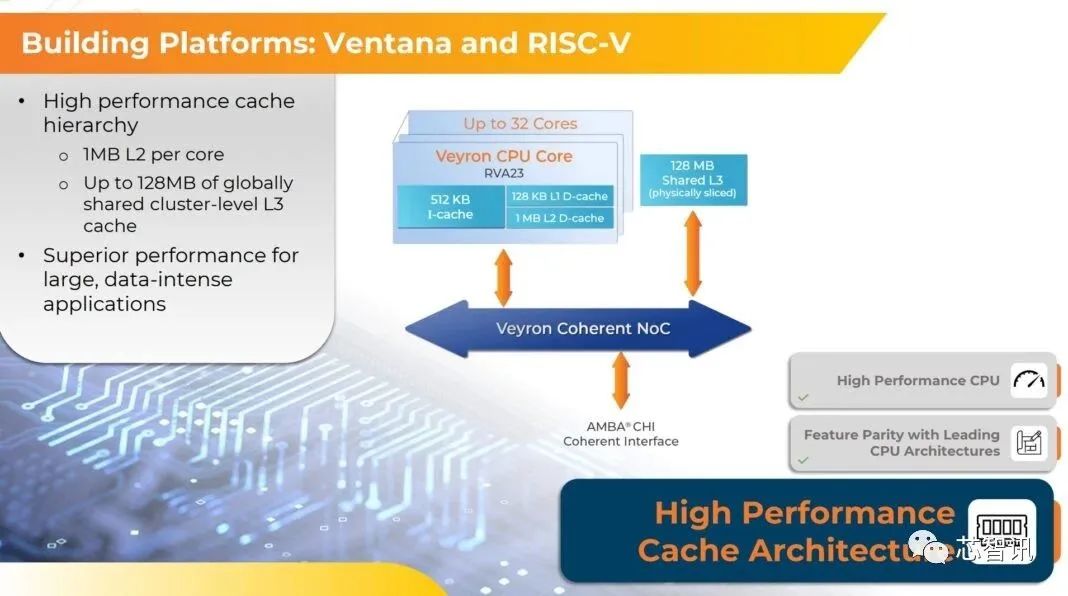

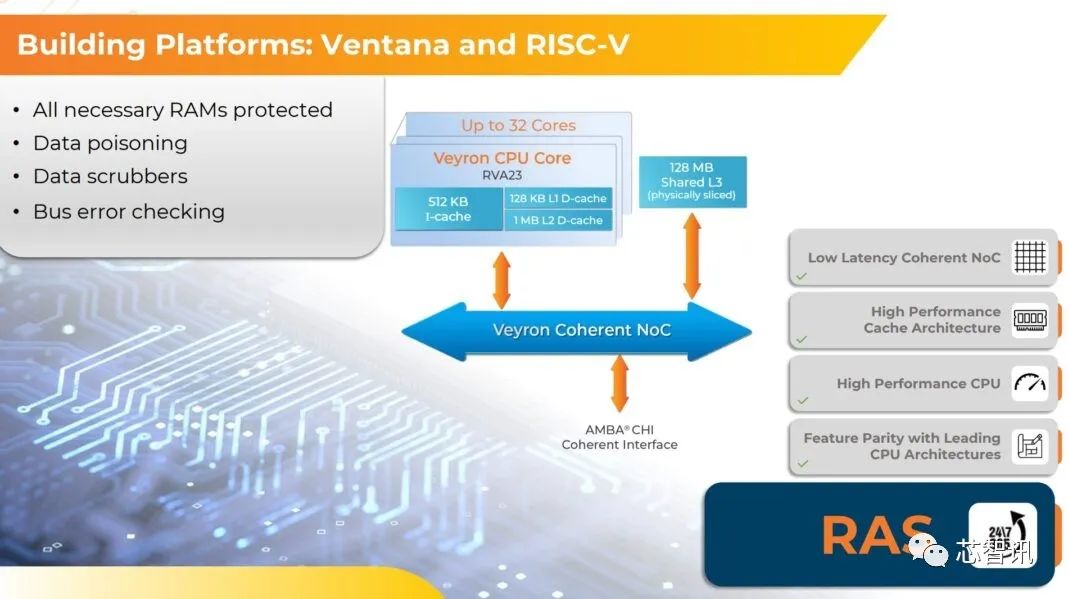

Характерная для конфигурации ядра Veyron V2, она основана на 4-нм техпроцессе TSMC, по-прежнему основанном на 8-конвейерной конструкции, поддерживает выполнение вне очереди и имеет основную частоту до 3,6 ГГц. количество одного кластера увеличено до 32, что вдвое больше, чем в предыдущем поколении, мультикластер можно расширить до 192 ядер. Размер кэша также был увеличен до 1 МБ кэша L2 на ядро и 128 МБ общего кэша L3 на уровне кластера.

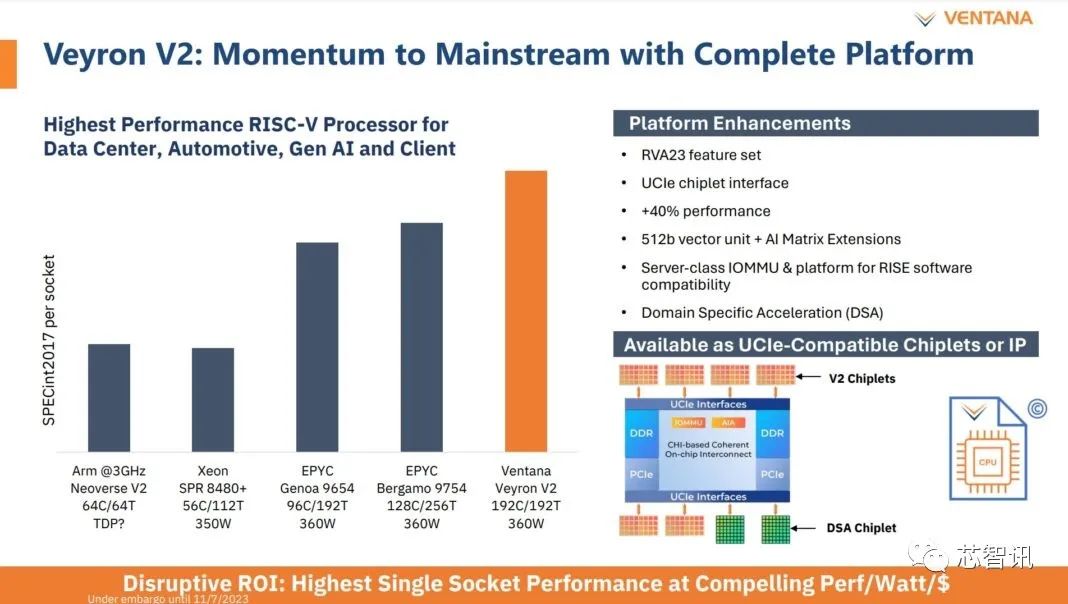

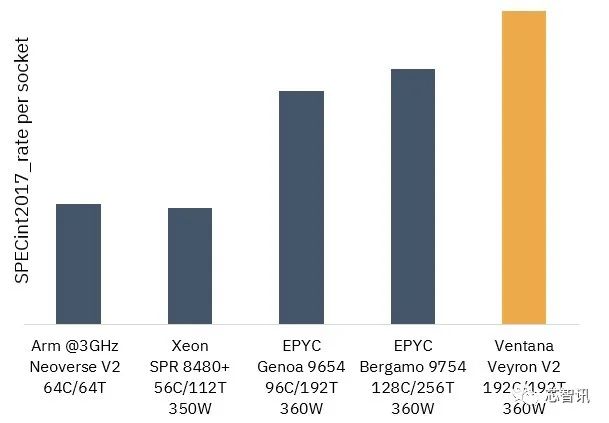

Ланье утверждает, что все новые обновления Veyron V2 повышают его производительность почти на 40% по сравнению с предыдущим поколением. Официальные данные прогнозирования производительности показывают, что производительность 192-ядерного Veyron V2 превосходит высокопроизводительный серверный чип AMD Epyc 9754!

Ниже приводится подробное описание нескольких ключевых обновлений Veyron V2:

Изменение стандартов Интернета

Veyron V2 Большим сдвигом является поддержка поддержки, посколькуChiplet(Маленькийчип)Стандарт подключенияСтандарт UCIe (Universal Chiplet Interconnect Express),а не предыдущее поколениеVeyron BoW в V1 (Bunch of Провода) стандарт протокола шины межсетевого взаимодействия интерфейса.

Понятно, что протокол BoW является открытым стандартом, контролируемым группой открытой архитектуры в рамках проекта Open Compute Project. Включая Ampere Computing, Alibaba, AMD, Arm, Cisco Systems, Dell, Eliyan, Fidelity Investments, Goldman Sachs, Google, Hewlett Packard Enterprise, IBM, Intel, Lenovo, Meta Platforms, Microsoft, Nokia, NVIDIA, Rackspace, Seagate Technology, Ventana и Wiwynn поддерживают BoW, широкий и дешевый протокол межчипового соединения, который делает реальностью обещание гибридных чиплетов для разных процессов и поставщиков.

Но в марте 2022 года десять крупных отраслевых гигантов, включая Intel, AMD, Arm, Qualcomm, TSMC, Samsung, ASE, Google Cloud, Meta (Facebook) и Microsoft, создали Chiplet Standard Alliance и официально запустили стандарт высокоскоростного межсоединения для универсальных Чиплеты «UCIe» призваны определить открытый, совместимый стандарт для объединения нескольких кремниевых чипов (или кристаллов) в один корпус посредством усовершенствованной упаковки.

Стандарт UCIe надеется стать таким же распространенным, как и другие стандарты подключения (такие как USB, PCIe и NVMe), обеспечивая при этом отличные показатели мощности и производительности для соединений чиплетов, снижая затраты на трансплантацию IP и увеличение количества SKU продуктов, а также ускоряя инновации в конструкции чиплетов. .

Хотя крупные производители, такие как HPE, IBM и Nvidia, не значились в первоначальном списке учредителей, в конечном итоге они присоединились к UCIe Alliance.

Баладжи Бакта сказал, что при обсуждении проектов процессоров Veyron V1 и V2 с 46 существующими и потенциальными клиентами стало очевидно, что UCIe — это направление развития межсетевых соединений малых чипов. В результате Ventana ускорила выпуск Veyron V2, который включает в себя многочисленные усовершенствования ядра RISC-V, поскольку для межсоединения чиплетов используется UCI Express вместо BoW.

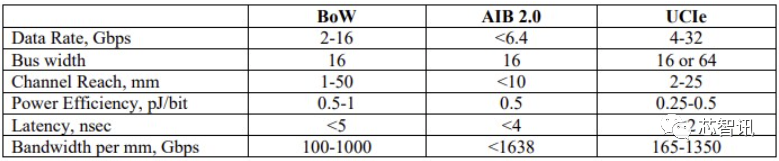

Ниже приводится сравнение межсоединений BoW, AIB 2.0 и UCIe 1.1, которое является дополнением к статье, написанной Лэй Шанем. Лэй Шан работал над межсетевым оборудованием в Исследовательском центре Ти Джея Уотсона IBM, а сейчас работает в стартапе по производству серверных процессоров Arm Ampere Computing:

Как видите, UCIe имеет вдвое большую скорость передачи данных, чем BoW, а пропускная способность шины может быть такой же или в 4 раза выше. Покрытие канала вдвое меньше, чем у UCIe, но канал в два раза более энергоэффективен, имеет менее половины задержки BoW и на 35–65 % больше пропускной способности на миллиметр.

Баладжи Бакта сказал: «Если разработчики чипов хотят использовать чиплеты, они должны поддерживать UCIe». «За UCIe был огромный толчок, потому что все хотели единого стандарта. BoW мог бы стать таким стандартом. Но мы не хотели продолжать его создавать, потому что стандарт UCIe эффективно решает затраты на упаковку и разрабатывается с наименьшими затратами». Эффективный UCIe также решает проблему стекирования 3D-памяти. Таким образом, можно легко реализовать Express 2.0 с помощью UCIe и использовать наш собственный опыт, чтобы преодолеть разрыв с UCIe 1.0. Например, UCIe вообще не предоставляется в AMBA. Связь с шиной согласованного интерфейса CHI. Поэтому мы добавили функциональность AMBA в UCIe 2.0».

Поддерживает 512-битное векторное расширение.

Еще одно большое изменение, которое Ventana надеется быстро реализовать и внедрить в конструкцию ядра Veyron V2, — это 512-битное векторное расширение RISC-V Vector 1.0.

Расширение аналогично расширениям, доступным на процессорах Intel Xeon Phi, начиная с 2015 года, и на процессорах Skylake Xeon SP, выпущенных в 2017 году. Расширение также было добавлено в процессоры AMD Genoa Epyc чуть больше года назад. Эти 512-битные векторные движки на самом деле не являются клонами Intel AVX-512 (как те, что используются в чипах AMD Genoa, по крайней мере, на программном уровне), но они достаточно близки, чтобы не стать проблемой, если вы захотите. портирование кода с X86 на RISC-V создает программный кошмар.

Кроме того, 512-битные векторные расширения обеспечат производительность, конкурентоспособную с процессорами X86 и Arm для рабочих нагрузок HPC и искусственного интеллекта, где вычисления искусственного интеллекта будут выполняться на ЦП, а не на ЦП, как на графических процессорах и других ускорителях, или использовать ускорители, внешние по отношению к ЦП.

Компания Ventana добавила 512-битные векторные расширения к ядру Veyron V2, что позволяет векторному движку поддерживать матричные операции и позволяет клиентам добавлять в архитектуру свои собственные матричные механизмы либо в ядре, либо в дискретном чиплете, используя каналы UCIe с соседними это.

Между прочим, ядро Veyron V1 не имеет каких-либо расширений векторного или матричного движка, что, очевидно, является проблемой, поскольку в ЦП все еще происходит большая часть логических выводов ИИ, а в некоторых случаях обучение ИИ и моделирование и моделирование HPC. тоже Завершено на ЦП.

Совершенно новая архитектура ядра

Еще одним большим изменением в конструкции Veyron V2 является то, что Ventana создала значительно улучшенную архитектуру ядра RISC-V.

Более агрессивно сочетая обработку инструкций в ядрах Veyron V2 и внося множество других настроек, Ventana смогла повысить производительность инструкций за такт (IPC) на 20 % по корзине рабочих нагрузок.

По сравнению с ядром Veyron V1, работающим на частоте 3 ГГц, тактовая частота Veyron V2 также была увеличена до 3,6 ГГц, что повышает производительность ядра еще на 20%. Таким образом, в конструкции ядра Veyron RISC-V от Ventana используется версия V1. ядро до версии V2. Общая производительность ядра улучшена на 40%.

Ядро Veyron V2 разработано на основе 4-нм техпроцесса TSMC, который был дополнительно улучшен по сравнению с Veyron V1 предыдущего поколения, основанного на 5-нм техпроцессе TSMC.

Ядро Veyron V2 также поддерживает профиль архитектуры RVA23, который требует использования 512-битных векторных расширений. Существуют также криптографические функции, работающие на векторном движке.

Ядро Ventana Veyron V2 также поддерживает спецификацию RV64GC и реализует суперскалярный конвейер внеочередного выполнения, который может декодировать и планировать до 15 инструкций за такт. Благодаря конструкции IOMMU и усовершенствованной архитектуре прерываний (AIA) ядро Veyron V2 может поддерживать серверные гипервизоры типа 1 и типа 2, а также вложенную виртуализацию.

Ядро Veyron V2 также имеет порты для отладки, трассировки и мониторинга производительности.

Все вышеперечисленное — это возможности, которыми должны обладать современные процессоры серверов гипермасштабируемых центров обработки данных.

Ни ядра V1, ни ядра V2 не поддерживают одновременную гиперпоточность, как и ядра Arm от Amazon Cloud и Ampere Computing, а также ядра «Siera Glen», используемые в будущих процессорах Xeon SP «Sierra Forest».

Кроме того, ядро Veyron V2 имеет 512 КБ кэша инструкций L1, 128 КБ кэша данных L1 и 1 МБ кэша данных L2. Эти ядра также имеют кэш-память L3 объемом 4 МБ, что в сумме составляет 128 МБ кэш-памяти L3 на 32 ядрах комплекса чиплетов Veyron V2. Ядра каждого чиплета соединены между собой с помощью собственной ячеистой сети, которая обеспечивает совокупную пропускную способность до 5 ТБ/с для ядер ЦП, памяти и других устройств ввода-вывода.

Четыре чиплета Veyron V2 можно соединить между собой с помощью UCIe, чтобы создать 128-ядерный комплекс, а если вы действительно хотите расширить границы возможного, вы можете соединить до шести чиплетов вместе для получения 192 ядер.

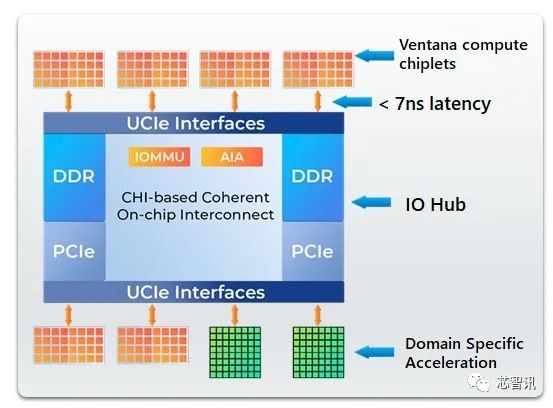

Вот концептуальная диаграмма процессора Veyron V2 на базе ядра с одним кристаллом ввода-вывода и шестью 32-ядерными чипсетами Veyron V2, а также некоторыми ссылками на ускорители для конкретной предметной области:

На изображении выше показан концентратор ввода-вывода, подключенный к контроллеру PCI Express 5.0 и контроллеру памяти DDR5, но Ventana может заменить его на контроллер памяти HBM3, если они того пожелают. Конструкция по умолчанию имеет двенадцать элементов управления памятью DDR5 на шести чипсетах Veyron V2 и восемь на четырех чипсетах Veyron V2, и это та же конфигурация, которую мы видим сегодня в любом серверном процессоре.

Производительность за пределами AMD Epyc 9754

Окно Вейрон Когда была выпущена версия V1, она называлась Производительность. за пределами AMD EPYC 7763. Итак, Вейрон Насколько сильной может быть производительность V2?

Вот как Ventana имитирует целочисленную производительность Veyron V2, а также необработанную производительность SPECint2017 для каждого слота:

Согласно данным, опубликованным Ventana, 192-ядерный процессор Veyron V2 RISC-V будет иметь целочисленную пропускную способность на 23% выше, чем процессор AMD «Bergamo» Epyc 9754, который оснащен тем же диапазоном мощности 360 Вт и 128 ядрами. 256 потоков, аналогично Veyron V2 быстрее 96-ядерного AMD «Genoa» Epyc; 9654 примерно на 34% выше; по сравнению с 56-ядерным Intel «Sapphire Rapids» Xeon SP 8480+ производительность Veyron V2 даже в 2,7 раза выше, что неудивительно, поскольку у Veyron V2 в 3,4 раза больше ядер и в 1,7 раза больше потоков, хотя ядра Veyron V2 должны работать на более низких тактовых частотах, другое основано на Arm Neoverse; 64-ядерный продукт V2, похоже, является заменой Amazon Cloud (AWS) Graviton3. Он имеет 64 ядра и имеет немного более высокую производительность, чем ядро Intel Sapphire Rapids Xeon SP 8480+, но это лишь половина от Veyron V2.

Поддержка ДСА

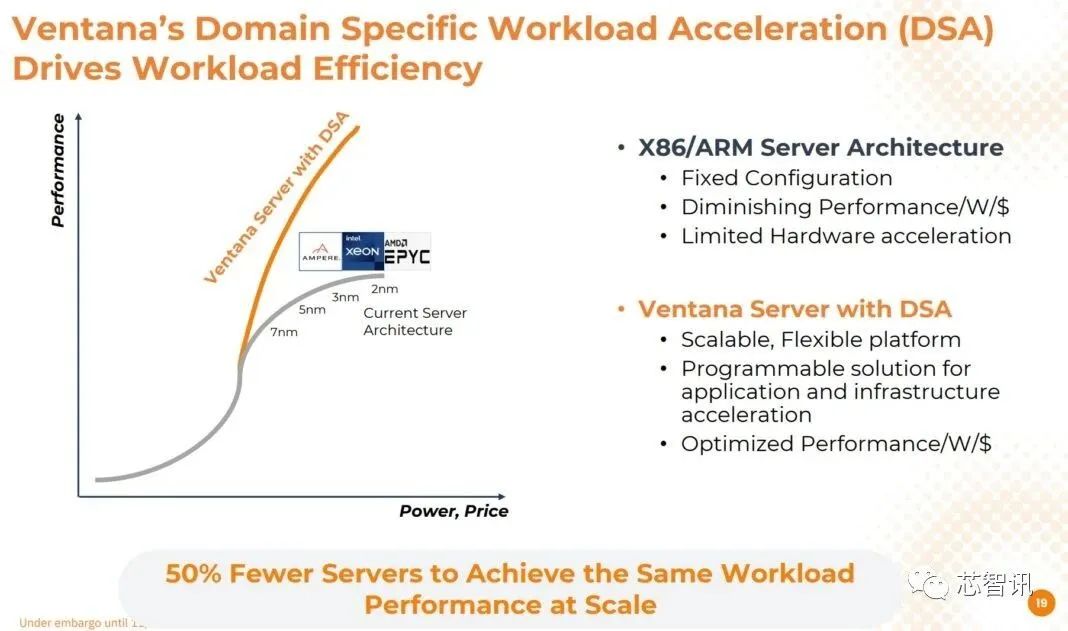

Veyron V2 также поддерживает DSA (дизайн, оптимизированный для определенной области), функцию, которая позволяет клиентам добавлять собственные чипы-ускорители в свои SoC.

Ланье сказал, что это нацелено на гипермасштабных клиентов, которые могут захотеть увеличить определенные рабочие нагрузки в своих центрах обработки данных, такие как сжатие и шифрование, обработка разгрузки TCP в сети или обработка ключей/значений в базах данных. Эти чипсеты-ускорители питаются от ядер Veyron V2 с помощью специальных инструкций, добавленных Ventana, что является большим преимуществом для всей архитектуры RISC-V.

В этом случае пользовательские инструкции позволяют программному обеспечению вызывать ускоритель, что можно рассматривать как отголосок того, как процессоры Intel использовали инструкции для вызова блока с плавающей запятой (FPU), когда одна из них была дополнительным отдельным FPU (FPU).

△Программируемый DSA Ventana

Подводя итог, цель Ventana — предоставить своим клиентам возможность использовать эти микросхемы DSA (будь то FPGA или ASIC) для повышения эффективности рабочей нагрузки, а не просто максимальной пропускной способности SPECint.

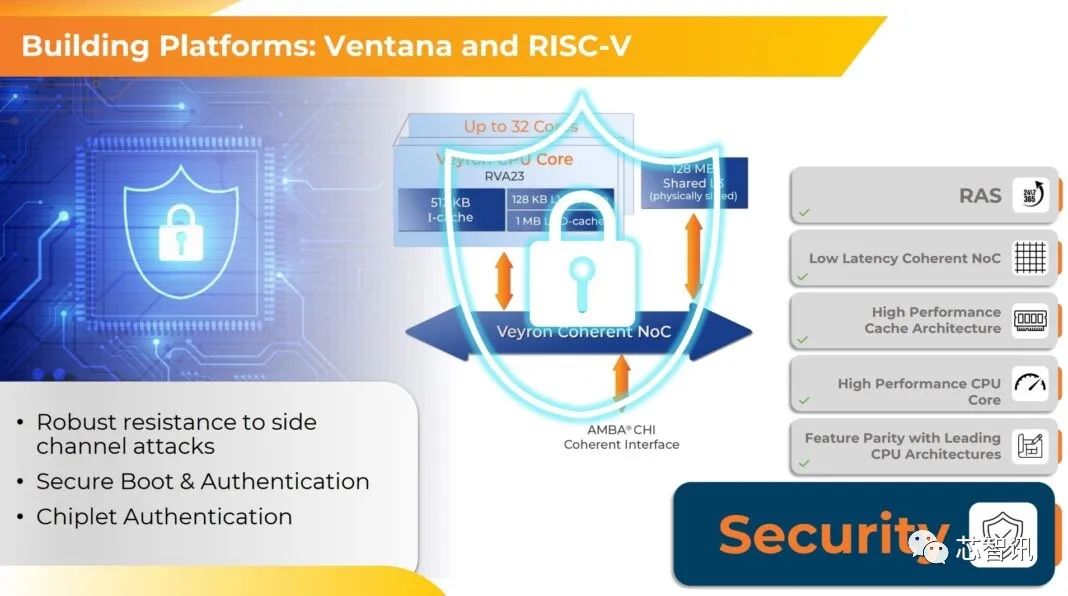

Безопасность значительно улучшена

Еще одна особенность Veyron V2 заключается в том, что он поддерживает комплексный RAS, имеет возможности ECC и предотвращает искажение данных.

Сегодня процессоры центров обработки данных также должны иметь возможности безопасной загрузки и аутентификации. Veyron V2 также спроектирован так, чтобы быть более устойчивым к атакам по побочным каналам, таким как уязвимости Spectre и Meltdown, которые могут привести к краже данных из памяти сервера.

Однако Ланье подчеркнул, что это не означает, что чип Veyron V2 не может быть атакован такими атаками, а то, что V2 понимает, как эти атаки выполняются во время проектирования, и может в определенной степени предотвратить их. «Затраты клиентов центров обработки данных на установку исправлений программного обеспечения или средств защиты на затронутых серверах часто могут снизить производительность на 10 или даже 20 процентов».

Запущен в производство в третьем квартале 2024 года.

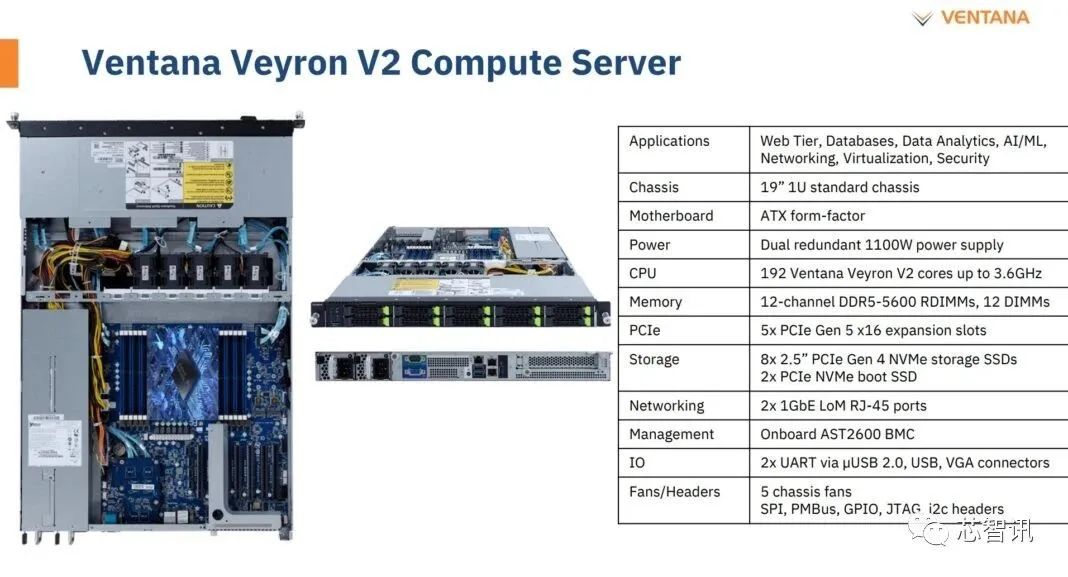

Ventana также предоставит эталонный дизайн 192-ядерного сервера высотой 1U на базе Veyron V2 с четырьмя 128-ядерными чипсетами и 12 каналами памяти DDR5-5600. На чиплете имеется межсоединение UCI Express и интерфейс ввода-вывода, который можно разместить. их внутри сокета ЦП сервера.

По имеющимся данным, Veyron V2будет Запущен в производство в третьем квартале 2024 года., UCIe для соединения небольших чипов 1.1 Ожидается, что PHY будет доступен на рынке.

Редактор: Core Intelligence — Меч Руруни

Источник:

https://www.theregister.com/2023/11/07/ventana_riscv_server/

https://www.servethehome.com/ventana-veyron-v2-risc-v-cpu-launched-for-the-dsa-future/

https://www.nextplatform.com/2023/11/07/ventana-launches-veyron-v2-risc-v-into-the-datacenter/

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

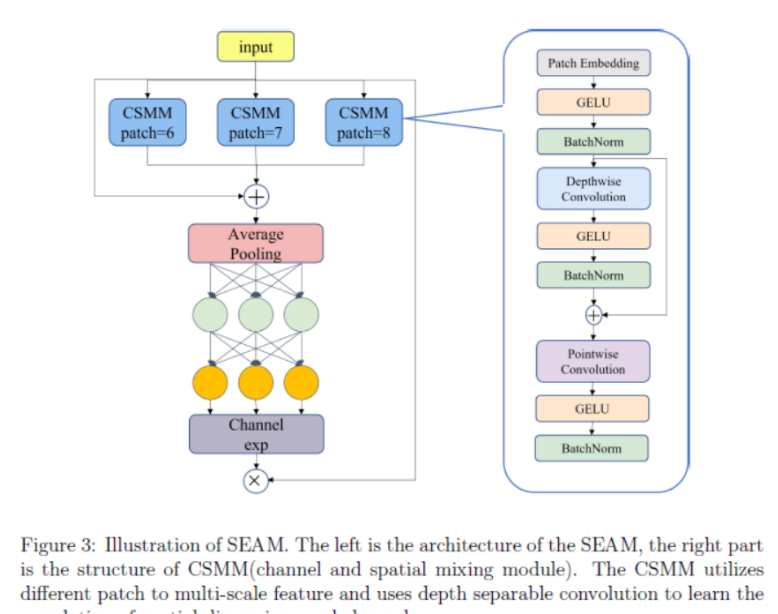

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

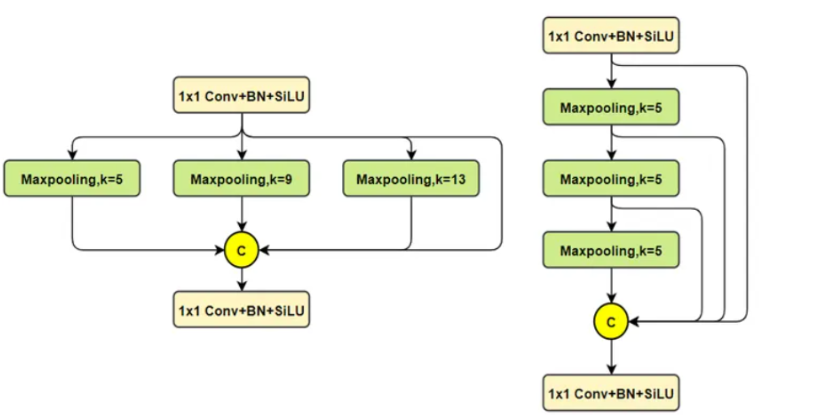

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

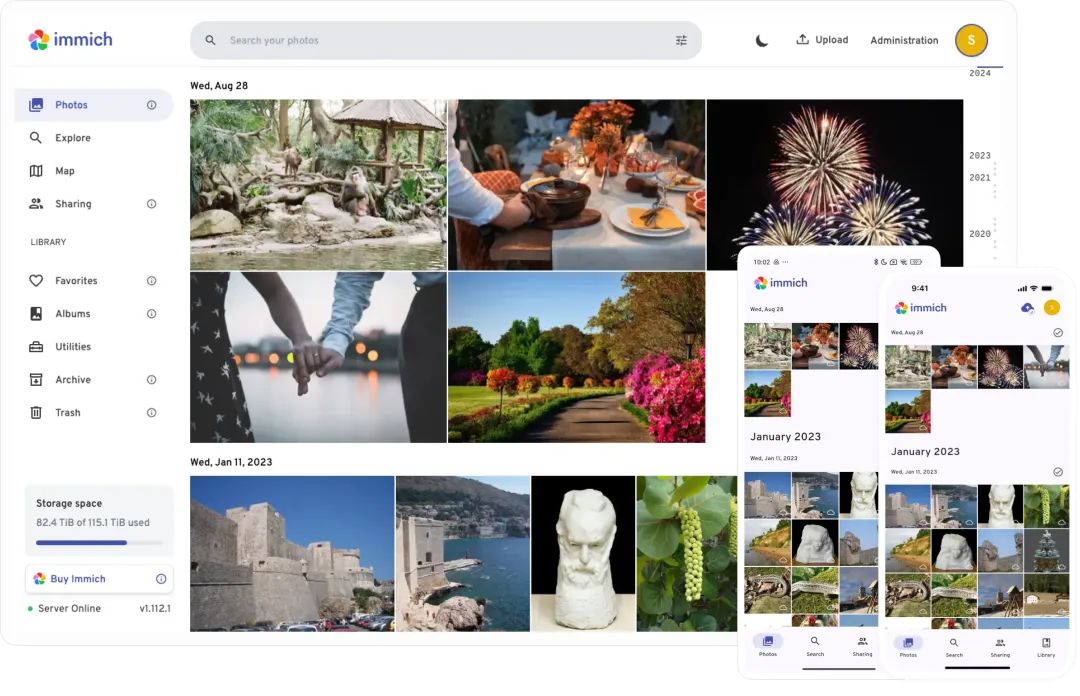

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

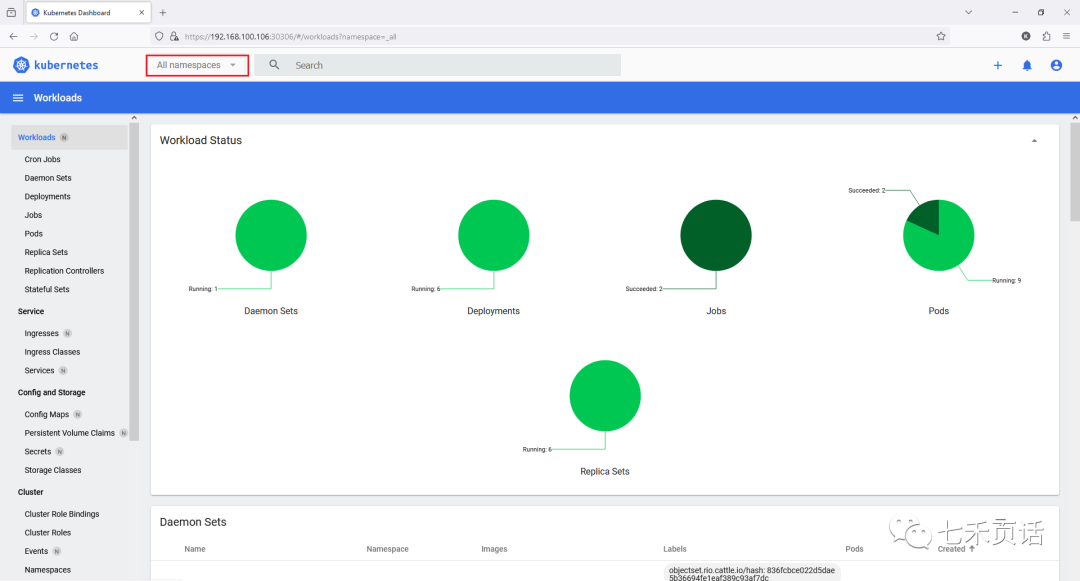

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

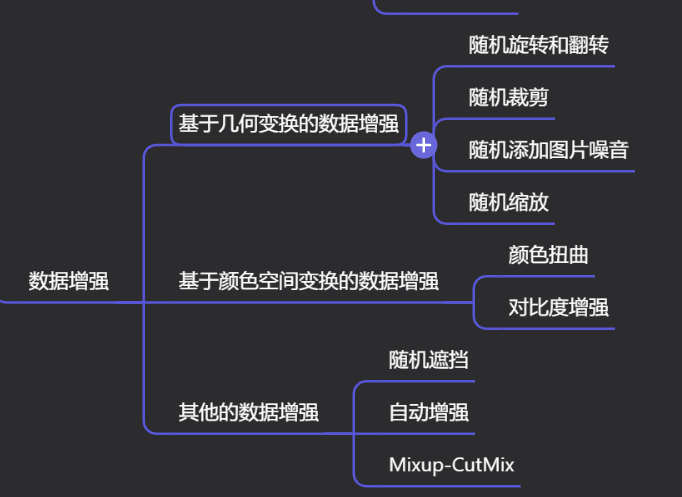

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

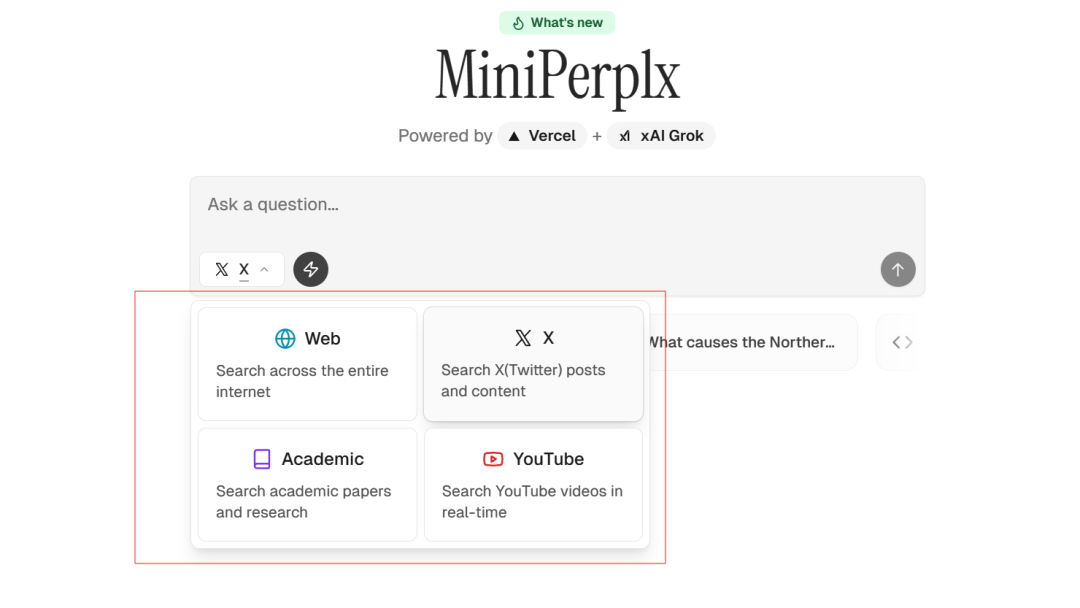

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

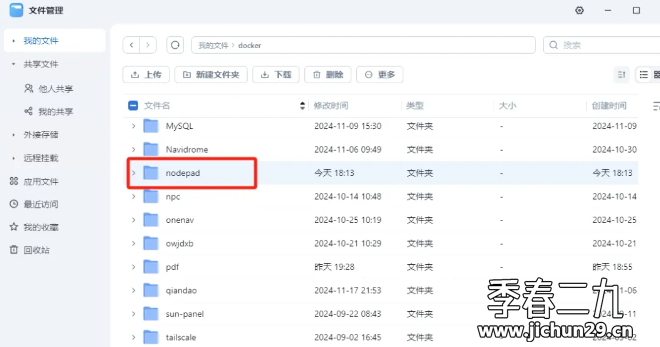

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

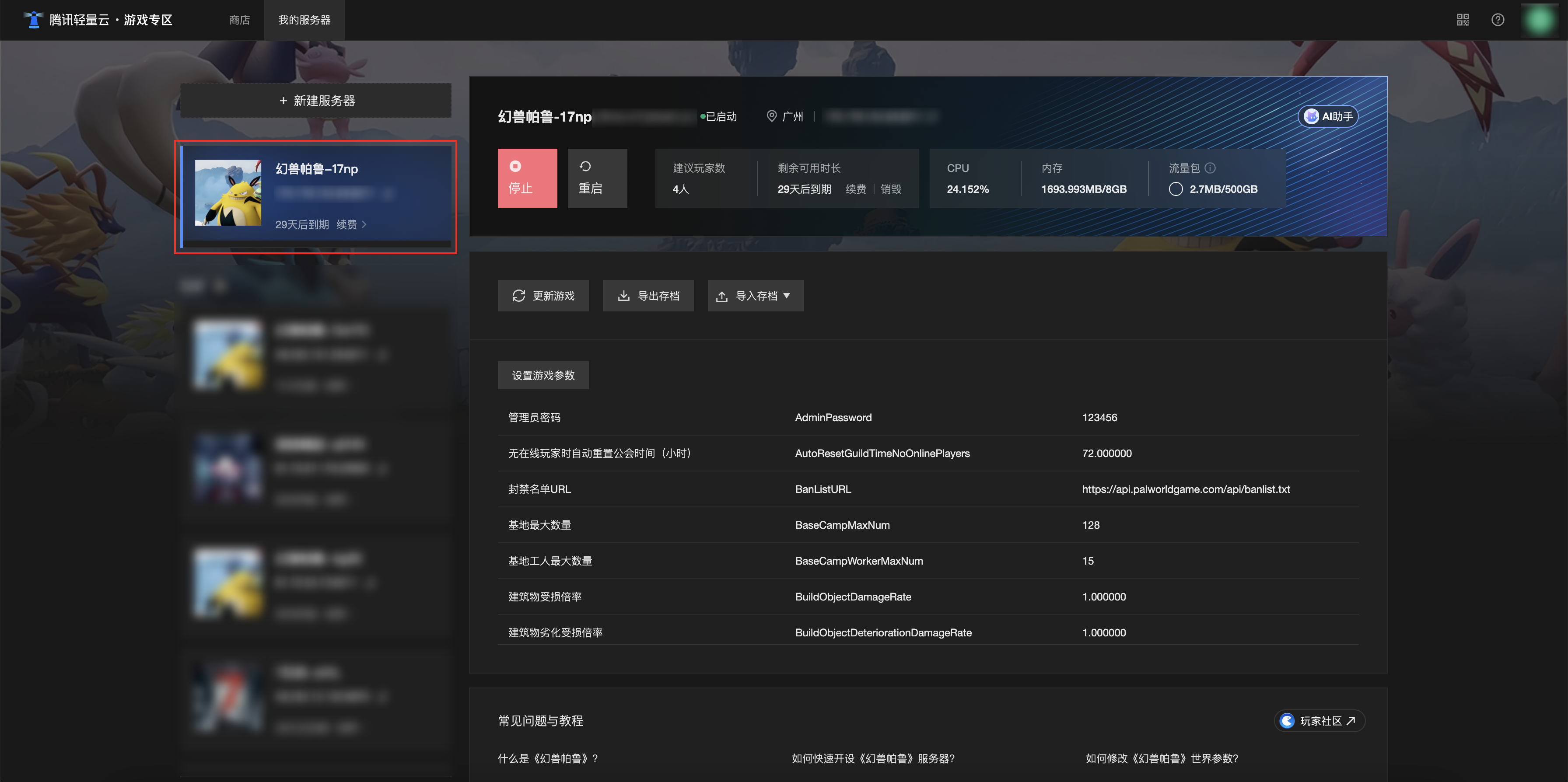

[Зона легкого облачного игрового сервера] Управление игровыми архивами