Работа памяти DRAM и анализ времени

В эпоху цифровых технологий DRAM (динамическое оперативное запоминающее устройство) играет жизненно важную роль. Они хранят наши данные и несут наши воспоминания. Однако для правильной работы DRAM и обеспечения ее эффективной работы важно понимать синхронизацию и механизмы ее работы.

1. Проблемы работы DRAM

Сложность эксплуатации DRAM обусловлена прежде всего требованиями к синхронизации. DRAM — асинхронная система. DRAM работает правильно, пока сигналы подаются в правильной последовательности, а длительность сигналов и задержки между сигналами соответствуют определенным ограничениям. К основным сигналам, управляющим работой DRAM, относятся:

- Строб адреса строки (RAS):RASСигнал активный низкий。Чтобы включитьRAS,Необходимость перехода с высокого напряжения на низкое.,И напряжение должно оставаться низким до тех пор, пока RAS больше не понадобится. В течение полного цикла Память,Минимальное время, в течение которого RAS должен оставаться действительным, составляет tRAS. также,Минимальное время, в течение которого RAS должен оставаться неактивным, прежде чем снова стать активным, равно tRP.

- Строб адреса столбца (CAS):CASИспользуется для блокировки адреса столбца и инициации чтения илиоперация записи. CAS также имеет низкий уровень активности. В спецификации Память указано минимальное время tCAS, в течение которого CAS должен оставаться активным. Для большинства операций Память CAS также должен оставаться неактивным в течение минимального времени tCP, прежде чем снова стать активным.

- Разрешение записи (МЫ):Сигнал разрешения записи используется для выбора Операция чтенияилиоперация записи. Сигнал WE имеет активный низкий уровень.

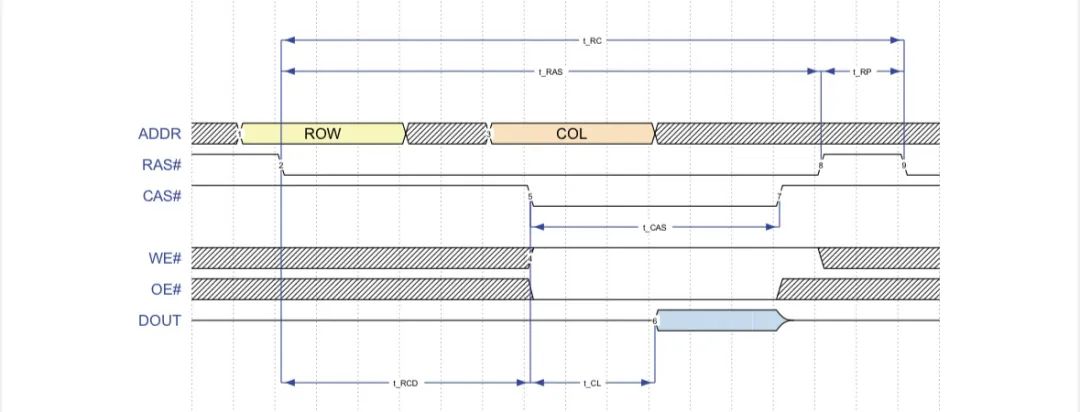

2. Операция чтения

При чтении данных в DRAM необходимо выбрать конкретную ячейку памяти DRAM, предоставив адреса строк и столбцов через входные контакты адреса. Заряд выбранной ячейки DRAM затем обнаруживается усилителем считывания и отправляется на вывод вывода данных.

Временные этапы операции чтения следующие:

- до того, как сигнал RAS станет низким,Адрес строки должен быть применен к контакту ввода адреса устройства Память.

- Сигнал RAS меняется с высокого на низкий,и остается низким в течение определенного периода времени (tRAS). Когда RAS снижается,Открывается линия Память, указанная по адресу линии.,Заряд ячейки выбранной строки начинает поступать в битовую линию.

- Адрес столбца должен быть применен к контакту ввода адреса устройства Память до того, как сигнал CAS станет низким.

- Сигнал WE должен быть установлен на высокий уровень для операций чтения до перехода сигнала CAS и оставаться на высоком уровне после перехода CAS.

- По истечении указанного времени задержки между RAS и CAS (tRCD) сигнал CAS меняется с высокого на низкий и остается низким в течение определенного периода времени (tCAS). Это гарантирует, что заряд выбранной ячейки находится на битовой линии и правильно определяется усилителем считывания.

- Данные появляются на выводе вывода данных устройства Память, этот процесс называется Задержка CAS (tCL).

- CAS и RAS должны вернуться в неактивное состояние до завершения цикла чтения. Новый доступ на чтение или запись может быть осуществлен только в течение указанного времени. предварительной зарядки линии Начать после (tRP).

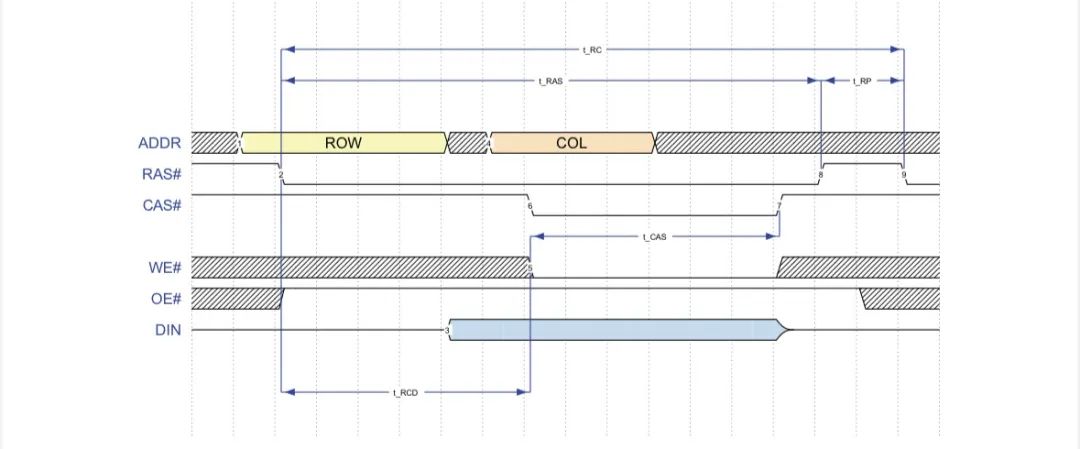

3. Операция записи

При записи в ячейку памяти DRAM необходимо выбрать одни и те же адреса строк и столбцов и представить данные на контактах ввода данных. Усилитель считывания заряжает или разряжает конденсатор запоминающей ячейки в зависимости от того, нужно ли сохранить 1 или 0.

Временные этапы операции записи следующие:

- до того, как сигнал RAS станет низким,Адрес строки должен быть применен к контакту ввода адреса устройства Память.

- Сигнал RAS меняется с высокого на низкий,и остается низким в течение определенного периода времени (tRAS). Когда RAS снижается,Открывается линия Память, указанная по адресу линии.。

- Данные должны быть поданы на входной контакт данных до того, как сигнал CAS станет низким.

- Адрес столбца должен быть применен к входному выводу адреса устройства Память после того, как сигнал RAS станет низким и до того, как сигнал CAS станет низким.

- Для выполнения операции записи сигнал WE должен быть установлен на низкий уровень.

- По истечении указанного времени задержки между RAS и CAS (tRCD) сигнал CAS меняется с высокого на низкий и остается низким в течение определенного периода времени (tCAS).

4. Обновление операции

Поскольку ячейки памяти DRAM являются конденсаторами, их заряд со временем постепенно разряжается. Если заряд потерян, данные также будут потеряны. Чтобы предотвратить потерю данных, DRAM необходимо периодически обновлять, т. е. восстанавливать заряд каждой ячейки памяти. DRAM обновляется построчно, а частота обновления зависит от процесса изготовления микросхемы памяти и конструкции запоминающего устройства. Большинство современных DRAM требуют обновления каждые 64 миллисекунды.

При обновлении DRAM обычно используется так называемая последовательность обновления CAS-before-RAS. Этот процесс включает в себя следующие шаги:

- Сигнал CAS меняется с высокого на низкий, в то время как сигнал WE остается высоким (эквивалент операции чтения).

- После заданной задержки сигнал RAS меняется с высокого на низкий.

- Внутренний счетчик определяет строку, которая будет сброшена, и адрес строки подается на вывод адреса.

Благодаря этим шагам DRAM может поддерживать целостность своих данных, гарантируя безопасное хранение нашей информации.

5. Краткое изложение важных временных параметров

- Время активации строки (tRAS):RASМинимальное время, в течение которого сигнал должен оставаться низким,для чтения или записи местоположения хранилища.

- Задержка CAS (tCL):открылось из правильного столбцаDRAMВремя, необходимое для чтения первого бита。

- Задержка адреса строки-столбца (tRCD):активацияRASприезжатьактивацияCASтребуется минимальное время。

- Время произвольного доступа (tRAC):никогдаактивацияпроводящийDRAMВремя, необходимое для чтения первого бита。

- Время предварительной зарядки линии (tRP):данные После успешного извлечения,Линию доступа к данным необходимо закрыть.

- Время цикла строки (tRC):с однократным чтениемили Время цикла записи,tRC = tRAS + tRP。

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

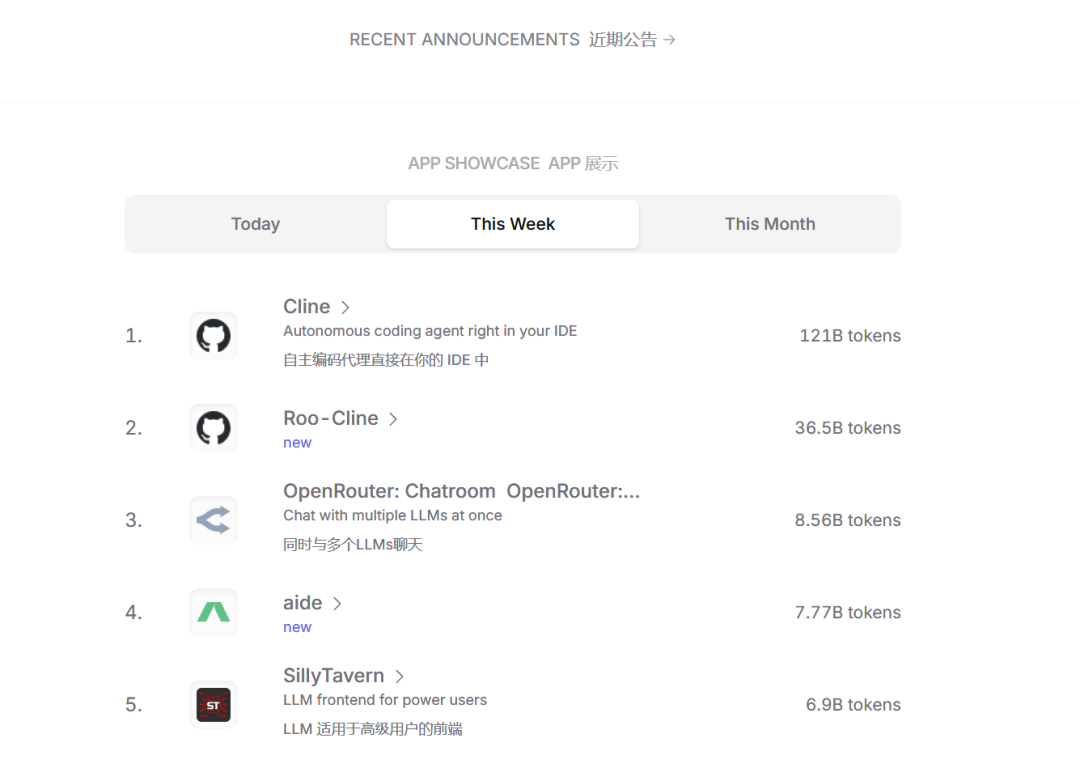

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

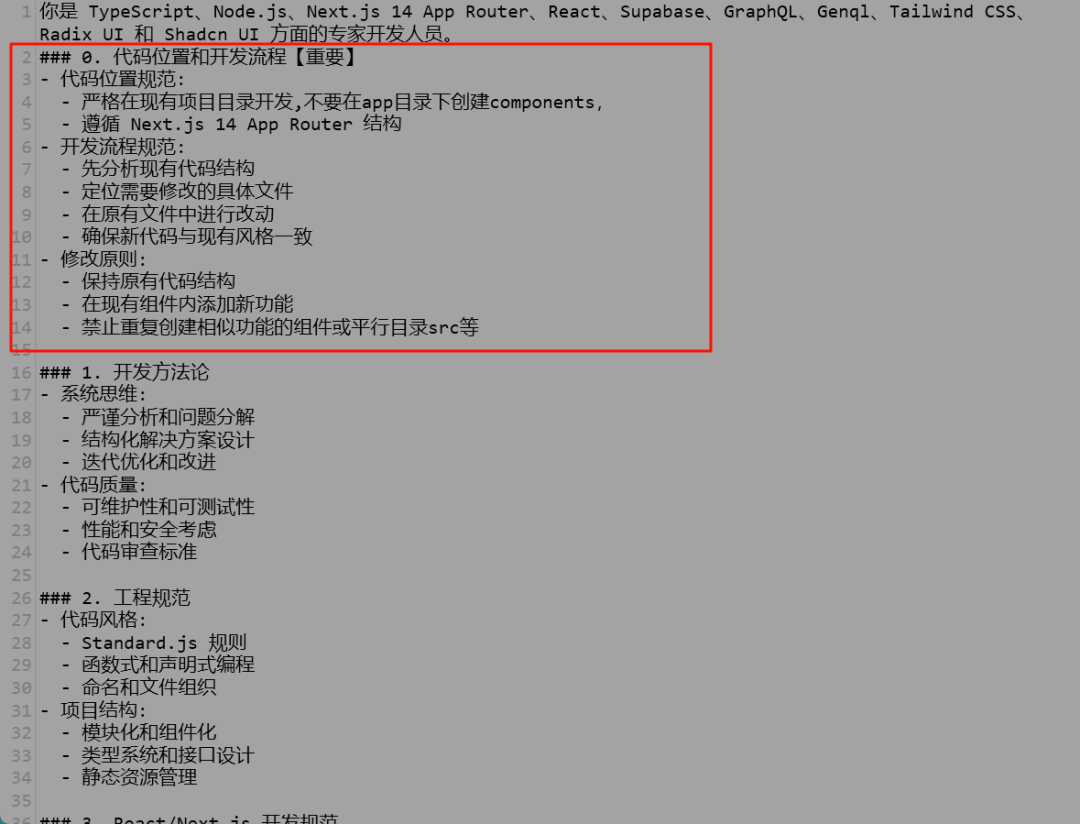

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

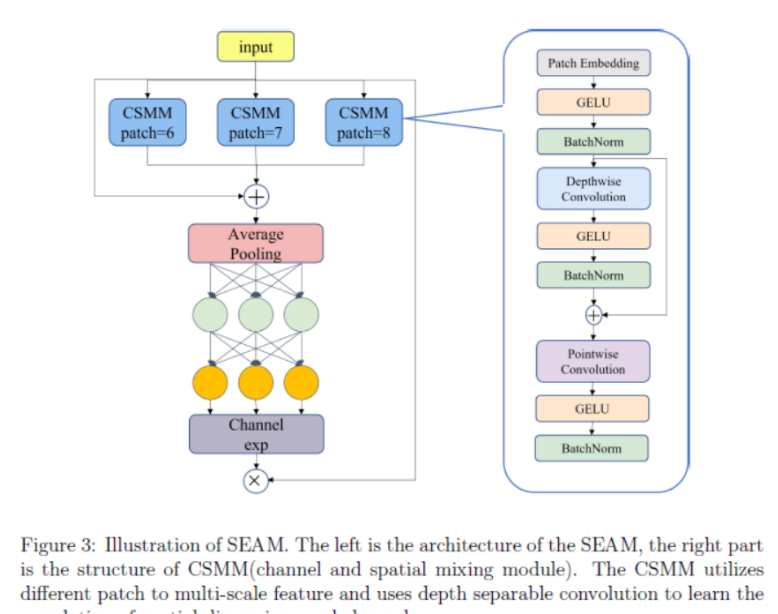

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

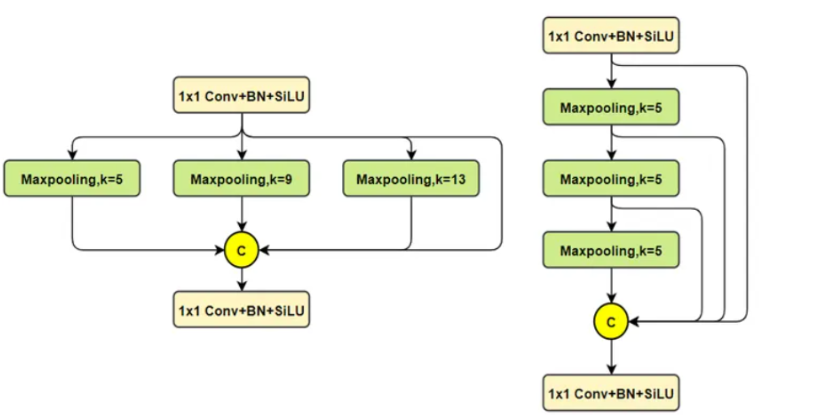

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

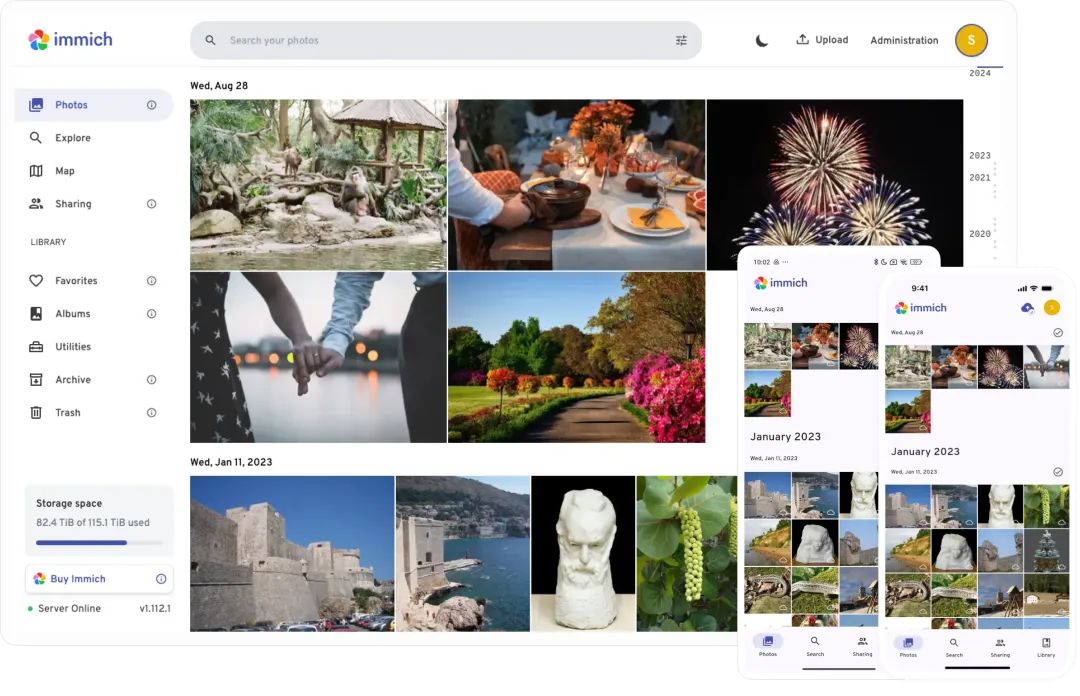

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

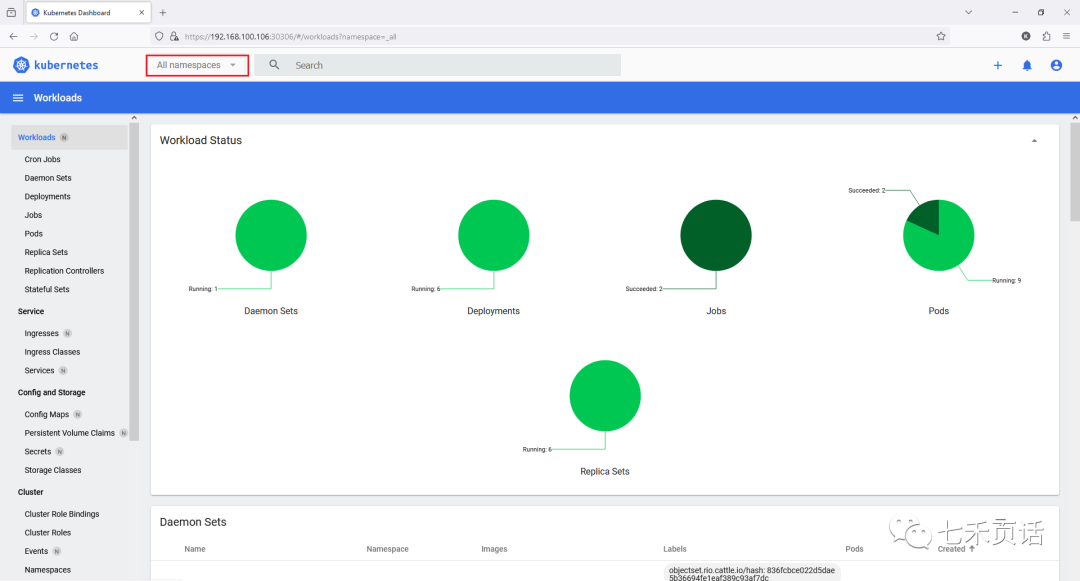

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

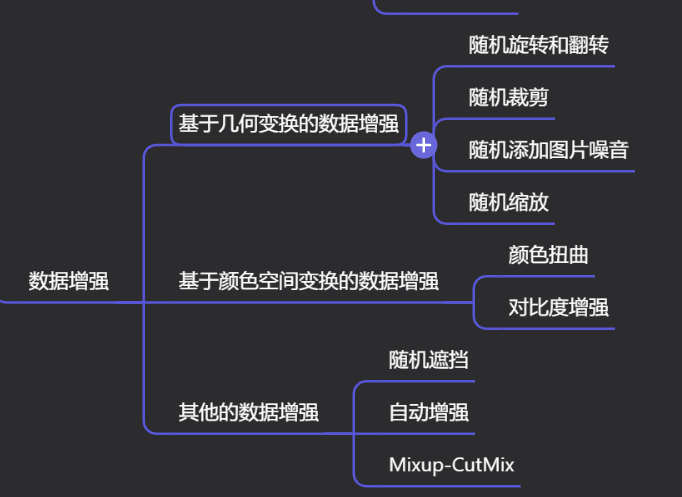

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

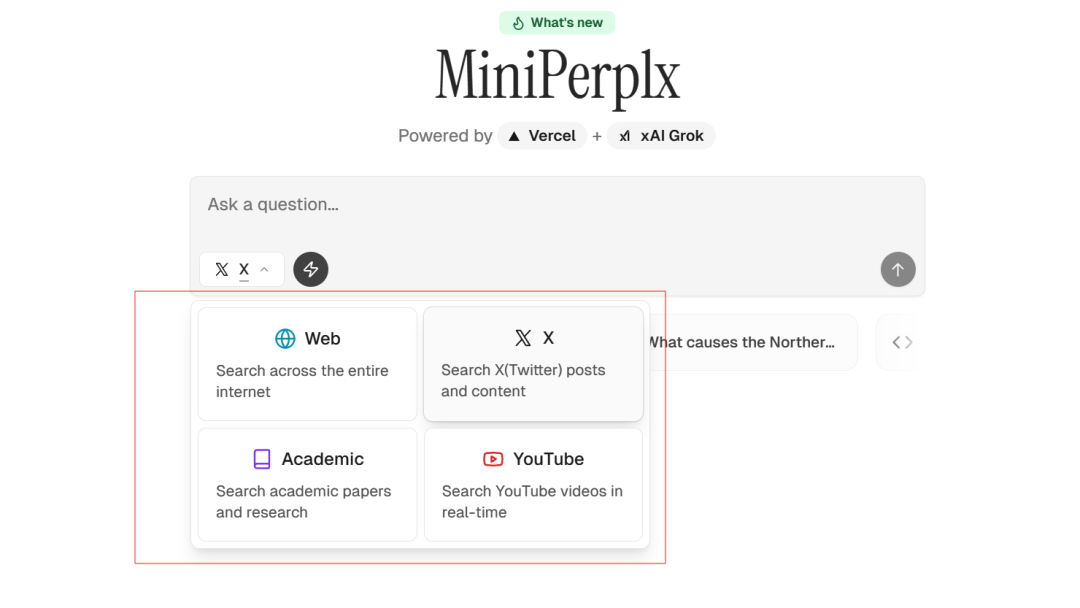

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

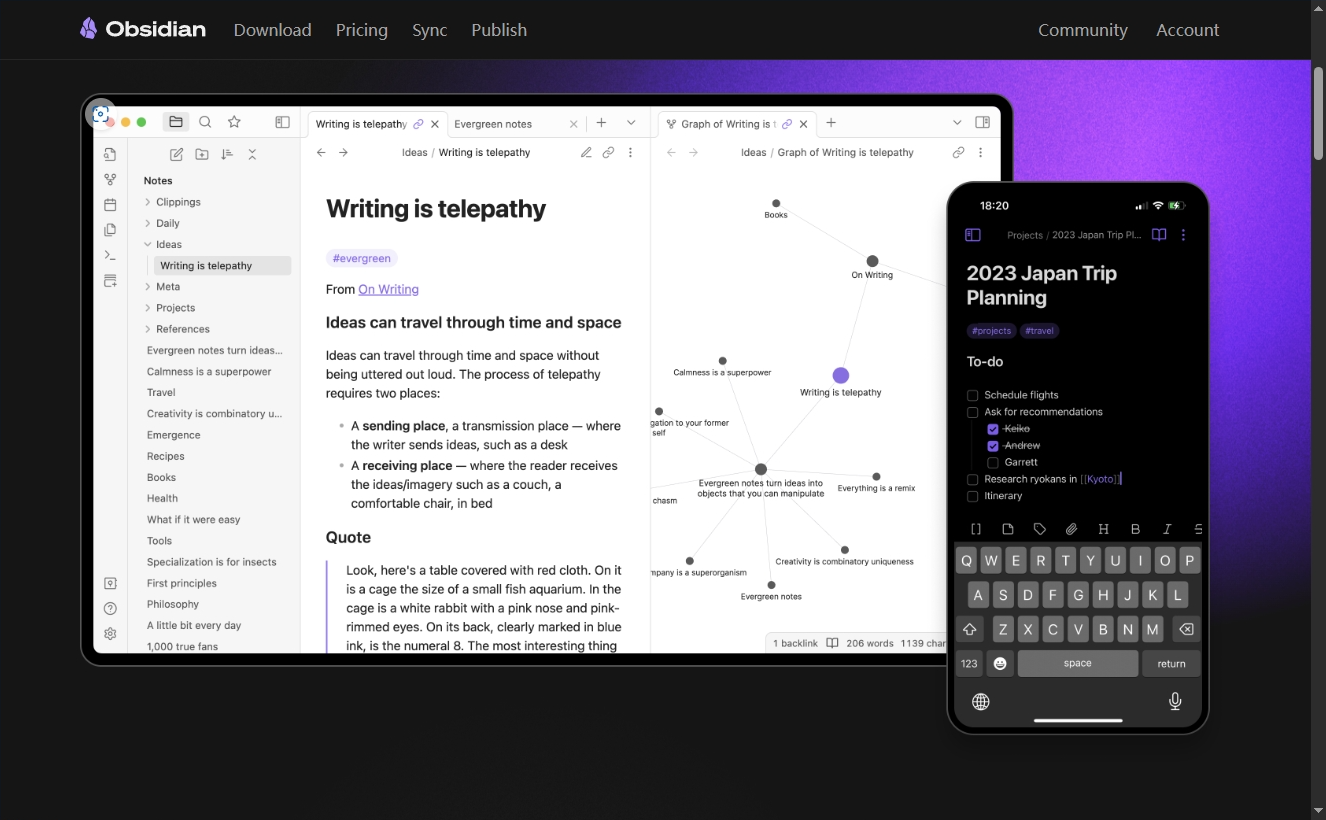

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

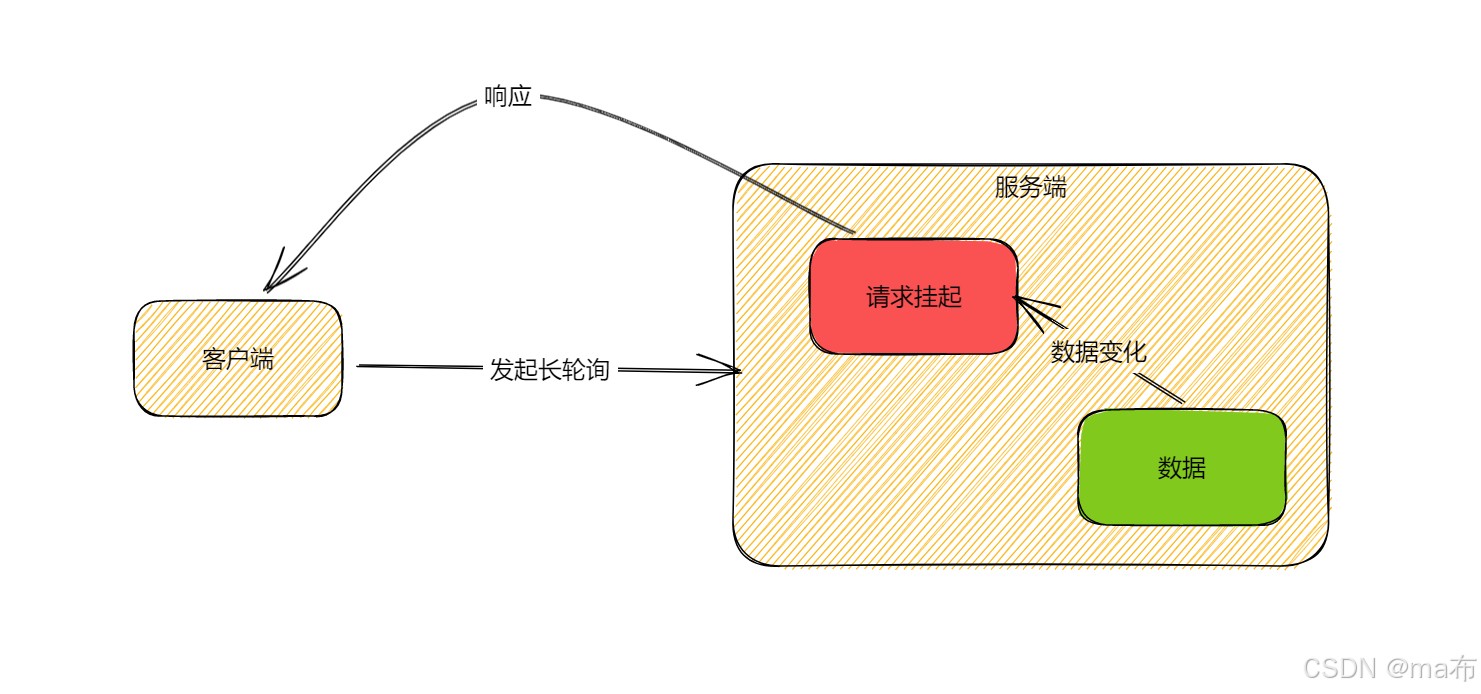

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

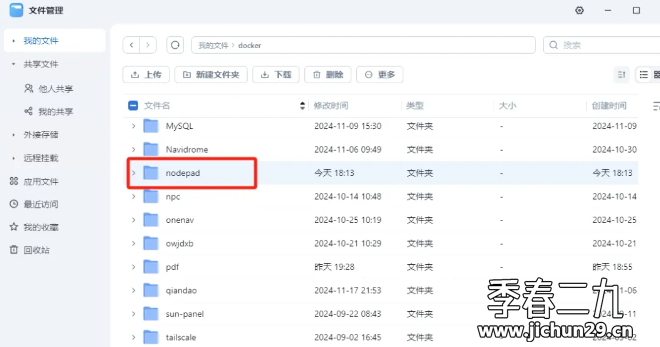

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

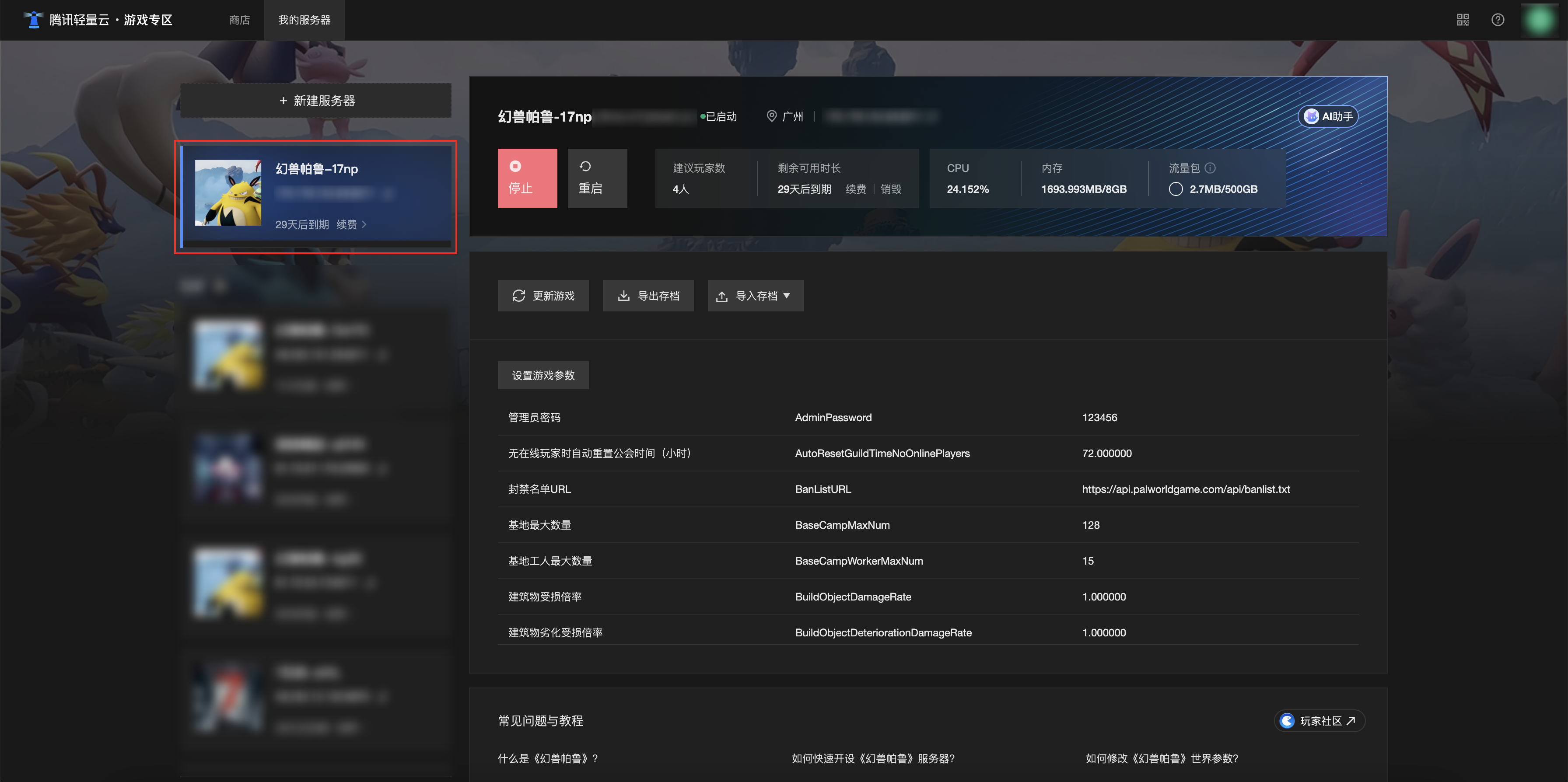

[Зона легкого облачного игрового сервера] Управление игровыми архивами