[Нарисуйте свой собственный ЦП] Конструкция ЦП с одной шиной (1)

🌷1. Цель

🌼Уровень 1: Разработка декодера инструкций MIPS

(1) Понять основные концепции декодирования инструкций;

(2) Декодировать 32-битное командное слово MIPS в различные сигналы декодирования команд.

🌼Уровень 2: Цикл команд фиксированной длины --- Проектирование FSM генератора времени

(1) Понять основные принципы генераторов синхронизации в традиционных трехуровневых системах синхронизации;

(2) Спроектировать и реализовать конечный автомат генератора синхронизации и функцию вывода для цикла команд фиксированной длины.

🌼Уровень 3: Цикл команд фиксированной длины — разработка выходной функции генератора синхронизации.

(1) Понять основные принципы генераторов синхронизации в традиционных трехуровневых системах синхронизации;

(2) Спроектировать и реализовать конечный автомат генератора синхронизации и функцию вывода для цикла команд фиксированной длины.

🌼Уровень 4: Комбинированный логический блок проводного контроллера

(1) Понять принципы проектирования проводных контроллеров в традиционных трехуровневых последовательных системах;

(2) Спроектировать и реализовать комбинационный логический блок жесткого контроллера.

🌼Уровень 5: Цикл команд фиксированной длины — конструкция жестко зашитого контроллера.

(1) Понять принципы проектирования проводных контроллеров в традиционных трехуровневых последовательных системах;

(2) Спроектировать и реализовать комбинационный логический блок жесткого контроллера с командным циклом фиксированной длины.

🌼Уровень 6: Цикл команд фиксированной длины — конструкция ЦП с одной шиной

(1) Понять основные принципы одношинной структуры ЦП;

(2) Разработать трехуровневую систему синхронизации, реализующую цикл команд фиксированной длины. Программа MIPS может работать на одной структуре шины, и, наконец, можно запустить простую программу сортировки sort-5.hex для реализации кодирования и декодирования. схема, соответствующая аппаратной схеме.

🌷2. Решающий уровень контент.

🌼Уровень 1: Разработка декодера инструкций MIPS

Функциональные модули, такие как компараторы, используются для декодирования 32-битных командных слов MIPS для генерации сигналов декодирования инструкций, таких как LW, SW, BEQ, SLT, ADDI и OtherInstr. Декодер инструкций является основным функциональным компонентом контроллера. Он отвечает за преобразование слов инструкций в сигналы декодирования инструкций. Каждый сигнал декодирования инструкций представляет собой конкретную инструкцию.

🌼Уровень 2: Цикл команд фиксированной длины --- Проектирование FSM генератора времени

Используйте соответствующие знания о цифровых логических схемах для разработки трехуровневой системы синхронизации с циклом команд фиксированной длины. Генератор синхронизации состоит из двух частей: конечного автомата и выходной функции. Этот эксперимент требует разработки конечного автомата. После реализации декодера команд на предыдущем уровне вы можете приступить к реализации другого основного функционального модуля, генератора синхронизации, который в основном состоит из трех частей: регистра состояния, логики комбинации конечных автоматов и логики комбинации выходных функций. Конечный автомат отвечает за преобразование между текущим состоянием и следующим состоянием, а функция вывода генерирует потенциал периода состояния и потенциал периода такта в соответствии с текущим состоянием. Если в структуре с одной шиной используется командный цикл фиксированной длины, все инструкции MIPS требуют 3 машинных цикла, 4 тактовых импульсов на машинный цикл и всего 12 состояний. После заполнения соответствующей таблицы Excel в соответствии с диаграммой состояний и автоматического создания логического выражения подсостояния схема может быть автоматически сгенерирована в logisim.

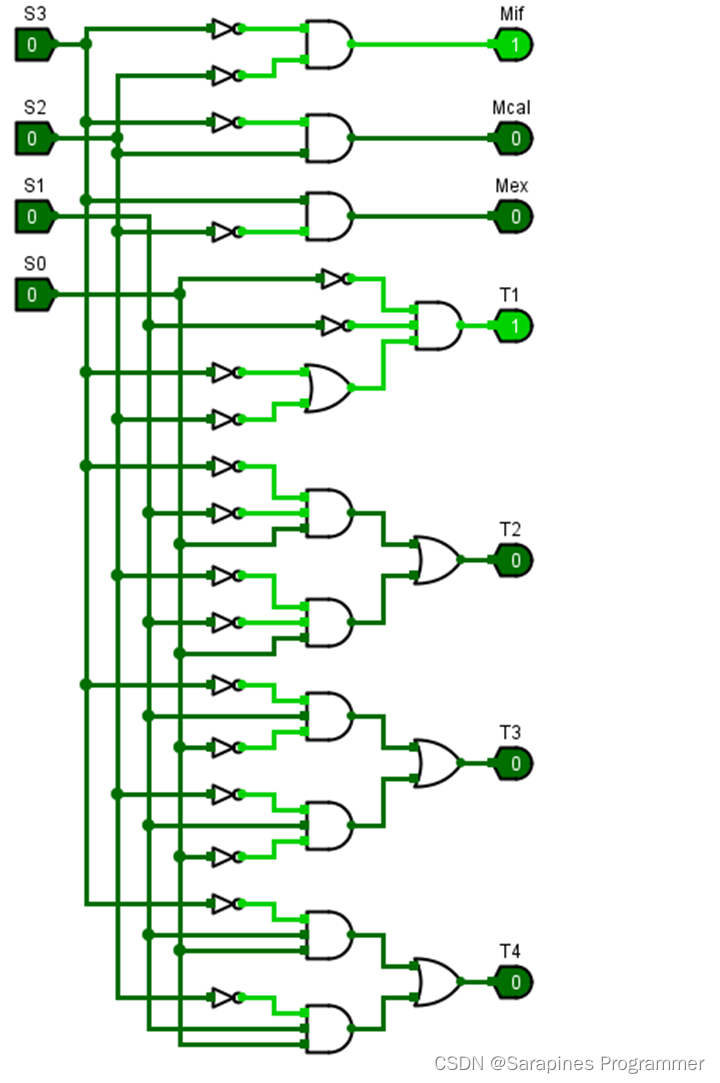

🌼Уровень 3: Цикл команд фиксированной длины — разработка выходной функции генератора синхронизации.

Используйте соответствующие знания о цифровых логических схемах для разработки трехуровневой системы синхронизации с циклом команд фиксированной длины. Генератор синхронизации состоит из двух частей: конечного автомата и выходной функции. Этот эксперимент требует разработки конечного автомата. После реализации декодера команд на предыдущем уровне вы можете приступить к реализации другого основного функционального модуля — генератора синхронизации. Внутренняя блок-схема генератора синхронизации в основном состоит из трех частей: регистр состояния, логика комбинации конечных автоматов и логика комбинации выходных функций. . Конечный автомат отвечает за преобразование между текущим состоянием и следующим состоянием, а функция вывода генерирует потенциал периода состояния и потенциал периода такта в соответствии с текущим состоянием. Если в структуре с одной шиной используется командный цикл фиксированной длины, все инструкции MIPS требуют 3 машинных цикла, 4 тактовых импульсов на машинный цикл и всего 12 состояний. После заполнения соответствующей таблицы Excel в соответствии с диаграммой состояний и автоматического создания логического выражения подсостояния схема может быть автоматически сгенерирована в logisim.

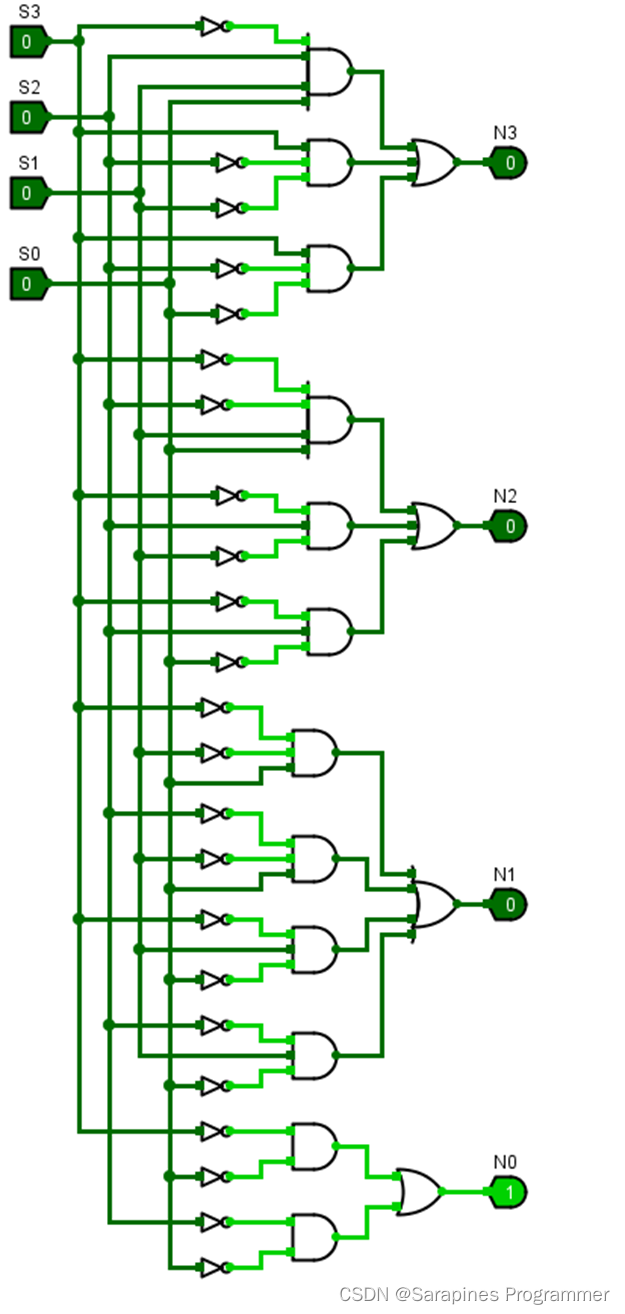

🌼Уровень 4: Комбинированный логический блок проводного контроллера

После реализации основных функциональных компонентов логики декодирования инструкций и генератора синхронизации мы дополнительно разработали и внедрили аппаратный комбинированный логический блок контроллера основного модуля контроллера. Все сигналы управления микрооперациями являются сигналами обратной связи, сигналами декодирования команд и статусом. циклические потенциалы. Комбинационная логическая функция потенциала биения. Вы можете перечислить условия генерации всех сигналов микроопераций, заполнить форму Excel ниже, автоматически генерировать логические выражения, а затем автоматически генерировать схемы в Logisim.

🌼Уровень 5: Цикл команд фиксированной длины — конструкция жестко зашитого контроллера.

После реализации функциональных модулей, таких как декодирование инструкций, ключевые функциональные компоненты генератора синхронизации и проводных контроллеров, наконец реализуется интеграция аппаратного контроллера. Общая структура аппаратного контроллера показана на рисунке ниже:

Рисунок 5.1-1

Структура генератора синхронизации показана ниже:

Рисунок 5.1-2

Для реализации логики генератора синхронизации необходимо правильно подключить последовательный конечный автомат с выходной функцией и регистром состояния в подсхеме проводного контроллера. Обратите внимание, что вам нужно только изменить логику в поле в левом нижнем углу и подключиться. правильно проверьте каждый функциональный компонент перед тестированием.

🌼Уровень 6: Цикл команд фиксированной длины — конструкция ЦП с одной шиной

После прохождения всех предыдущих экспериментальных уровней проведите финальную совместную отладку на этом уровне для тестирования программы сортировки. Загрузите программу sort-5.hex в ОЗУ, ctrl+k запустится автоматически. Программа должна запуститься до такта 0xbbb и остановиться. Количество инструкций равно 251. Обратите внимание, что последняя инструкция — это инструкция перехода beq, которая выполняет возврат. к текущей инструкции для продолжения выполнения. Да Бесконечный цикл.

🌷3. Шаги для прохождения уровня.

🌼Уровень 1: Разработка декодера инструкций MIPS

Рисунок 5.1-3

🌼Уровень 2: Цикл команд фиксированной длины --- Проектирование FSM генератора времени

Рисунок 5.1-4

🌼Уровень 3: Цикл команд фиксированной длины — разработка выходной функции генератора синхронизации.

Рисунок 5.1-5

🌼Уровень 4: Комбинированный логический блок проводного контроллера

Рис. 5.1-6 Изображение слева — это верхняя половина изображения, а изображение справа — нижняя половина изображения.

🌼Уровень 5: Цикл команд фиксированной длины — конструкция жестко зашитого контроллера.

Рисунок 5.1-7

🌼Уровень 6: Цикл команд фиксированной длины — конструкция ЦП с одной шиной

Рисунок 5.1-8

🌷4. Краткое описание прорыва уровня.

🌼Уровень 1: Разработка декодера инструкций MIPS

1. Вам необходимо обратить внимание на то, соответствует ли рамка выводов тестируемой схемы предыдущему рисунку. Регулировка выводов приведет к изменению интерфейса корпуса тестируемого компонента, в противном случае тест не будет проходить нормально;

2. Проверьте, соответствует ли внешний вид подсхемы проверяемой схемы, то есть корпуса, предыдущему изображению, положению контактов, последовательности контактов, количеству контактов и т. д. Эта разница также приведет к провалу теста. .

🌼Уровень 2: Цикл команд фиксированной длины --- Проектирование FSM генератора времени

1. Щелкните проект в Logisim, чтобы выбрать комбинационную логическую схему анализа, заполнить соответствующую таблицу Excel в соответствии с диаграммой состояний и автоматически сгенерировать логические выражения подсостояний для автоматического создания схемы в Logisim. Следует отметить, что при заполнении таблицы истинности следует быть внимательным. Просто проверяйте чаще и ошибок, как правило, не допустите.

🌼Уровень 3: Цикл команд фиксированной длины — разработка выходной функции генератора синхронизации.

1. Идея прохождения уровня аналогична второму уровню. Также заполните форму на основе тестовых примеров при анализе комбинационных логических схем по инженерному проекту на logisim.

🌼Уровень 4: Комбинированный логический блок проводного контроллера

1. Следует отметить, что выходной сигнал цикла выполнения инструкции slt имеет вид: T1: rout xin; T2: rout rs/rt slt; T3: zout rin regdst, где rs/rt — сигнал regtgt, а Cin — PCin. (когда входное значение равно=1, когда T3=1, beq, выходное PCin=1) и, наконец, введите выражение, сгенерированное Excel, в logisim.

2. Если в части slt есть ошибка, часть T1 должна устранить сигнал Rs/Rt и сигнал slt.

🌼Уровень 5: Цикл команд фиксированной длины — конструкция жестко зашитого контроллера.

1. Конструкция таможенного оформления: правильно подключите последовательный конечный автомат к выходной функции и регистру состояния в подсхеме проводного контроллера, чтобы реализовать логику генератора синхронизации.

2. Вам необходимо обратить внимание только на изменение логики в поле в левом нижнем углу и правильно подключить каждый функциональный компонент для проверки.

🌼Уровень 6: Цикл команд фиксированной длины — конструкция ЦП с одной шиной

1. Проект таможенного оформления: сначала загрузите программу sort-5.hex (загрузите образ данных) в ОЗУ и автоматически запустите ctrl+k. Программа должна запуститься до такта 0x81d и остановиться, а количество инструкций равно 251.

2. Следует отметить, что последняя инструкция является инструкцией ветвления beq, которая выполняет возврат к текущей инструкции для продолжения выполнения.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

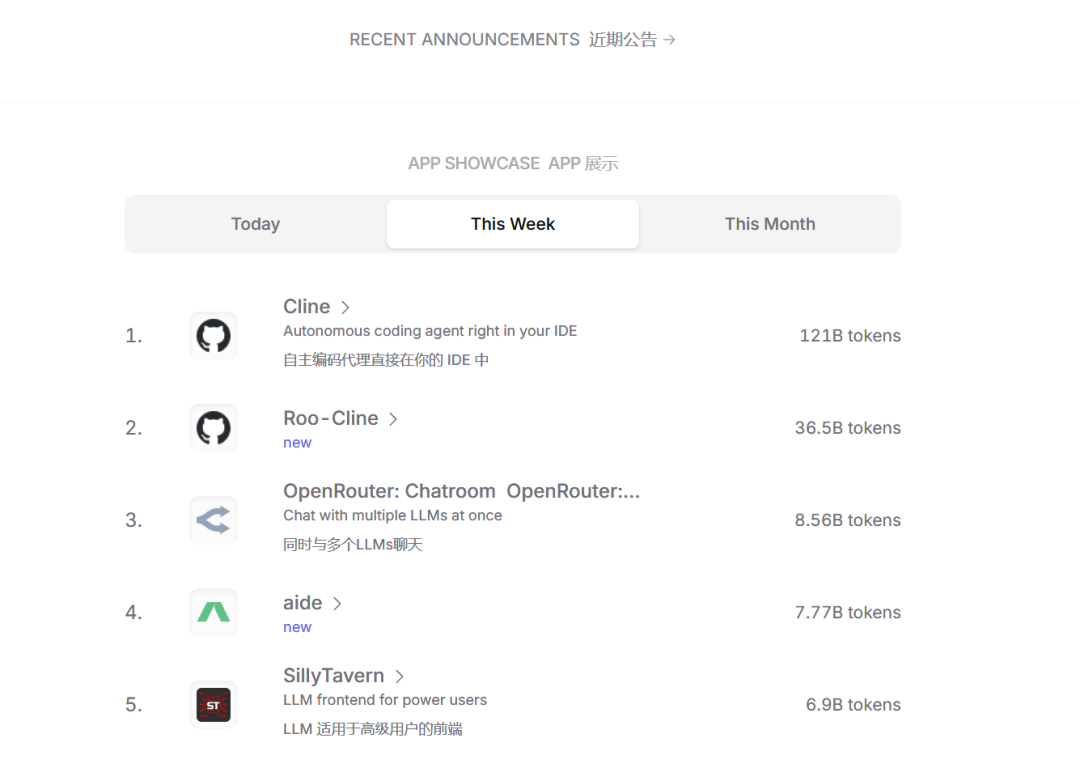

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

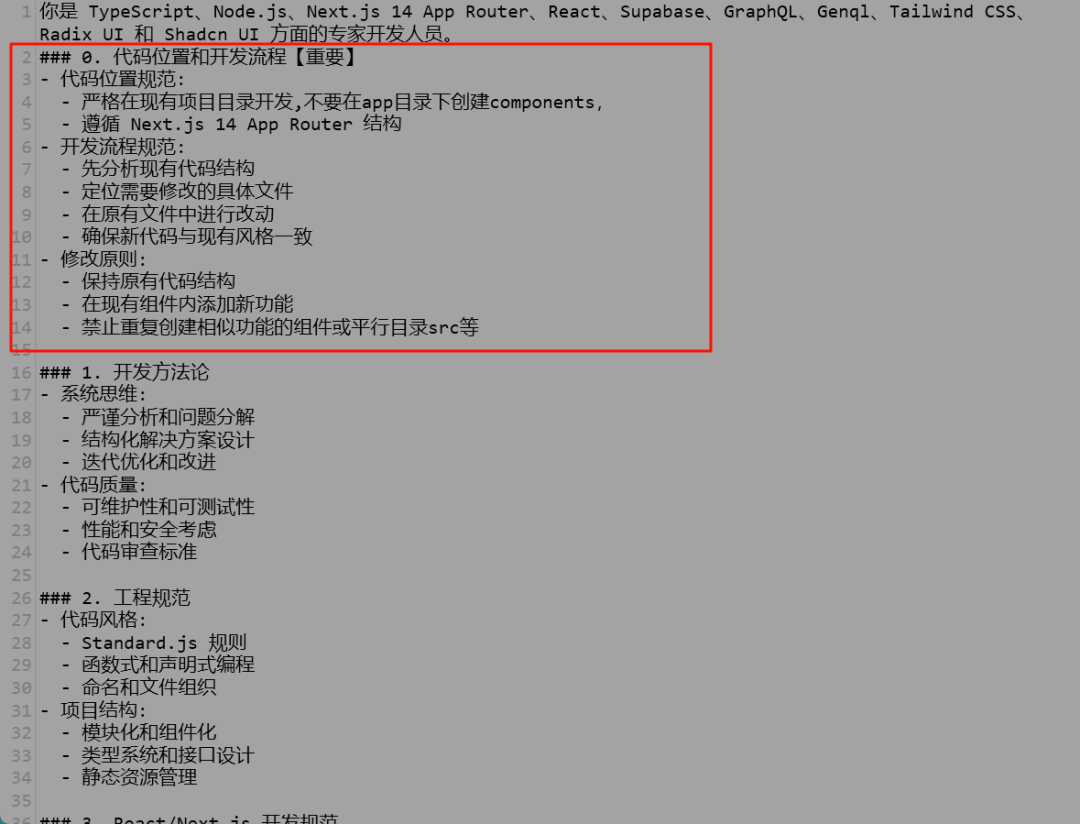

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

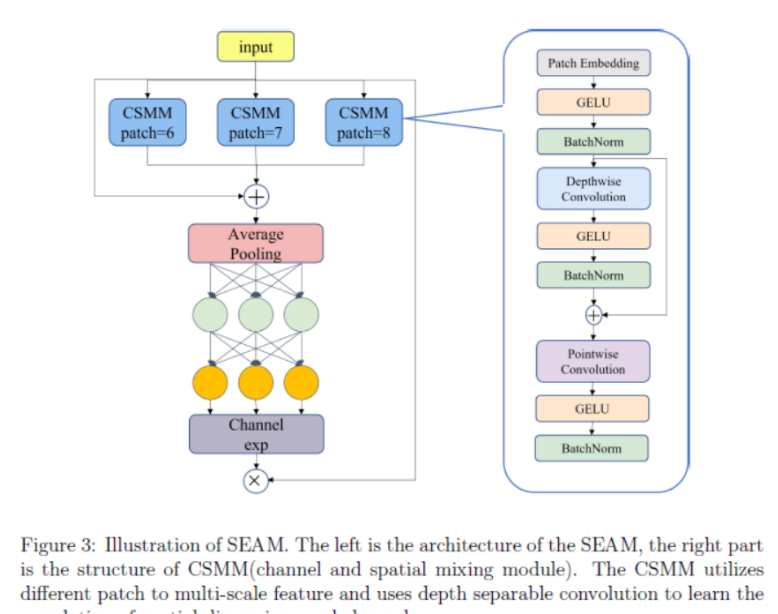

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

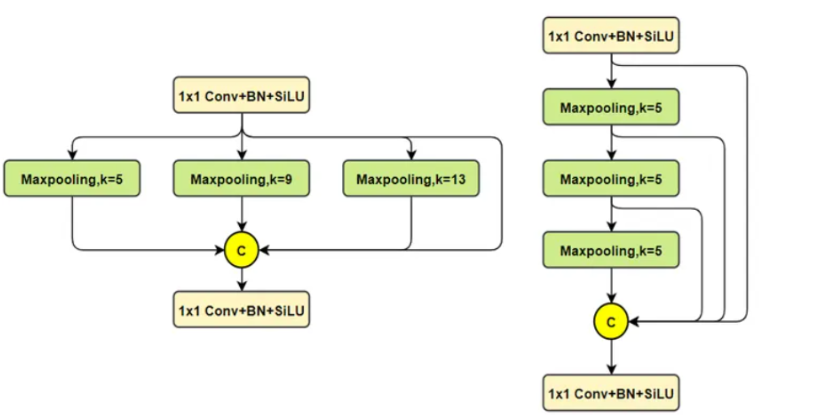

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

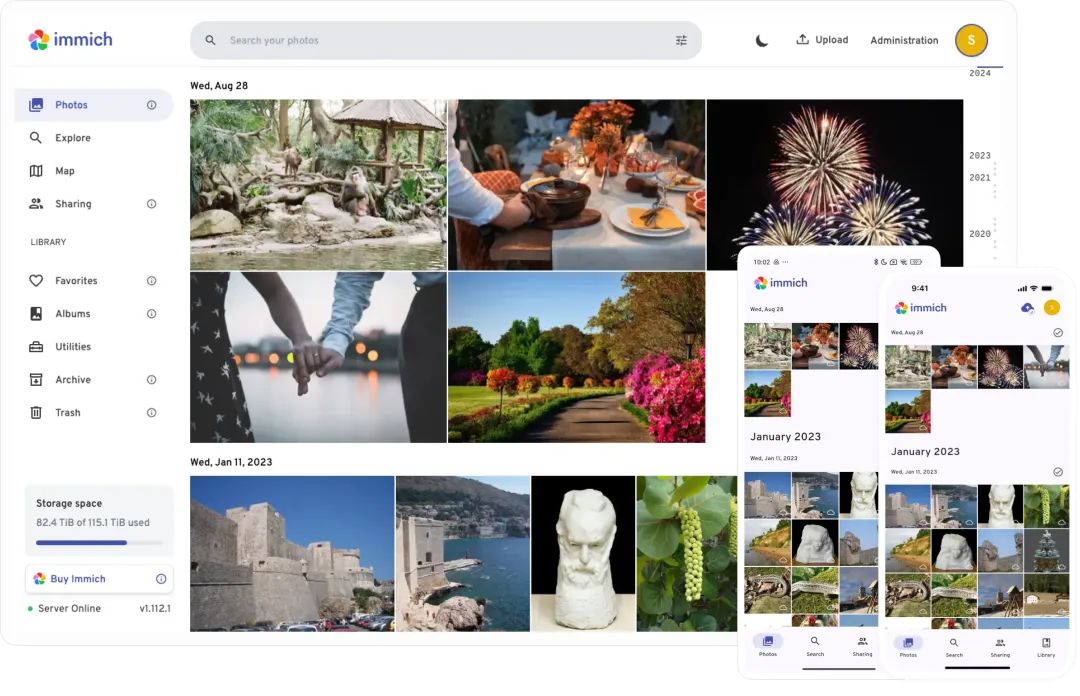

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

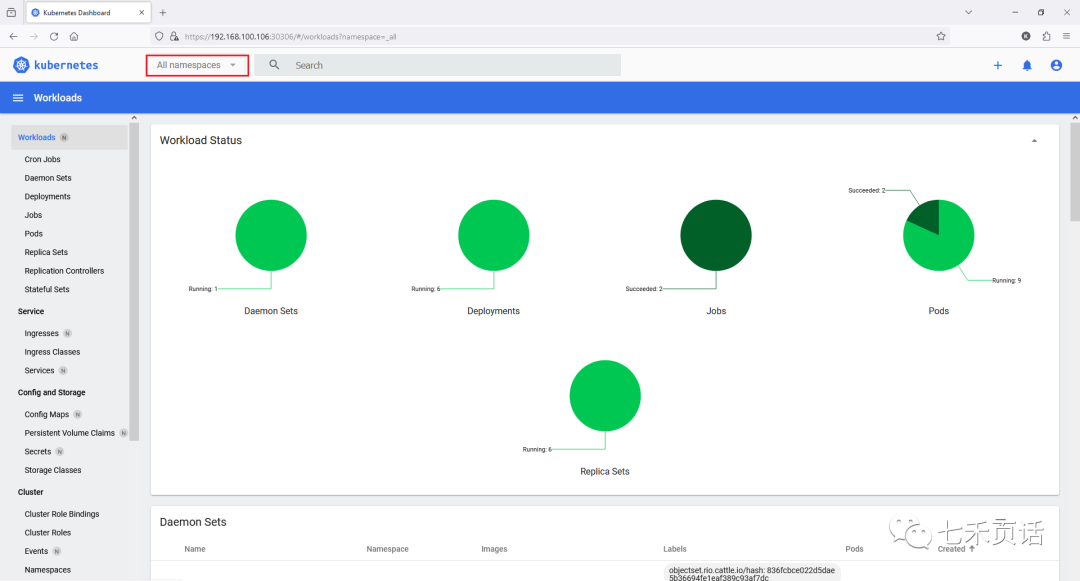

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

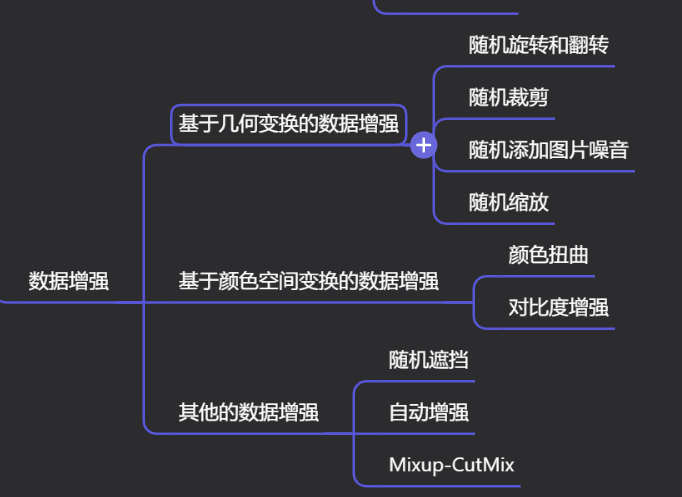

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

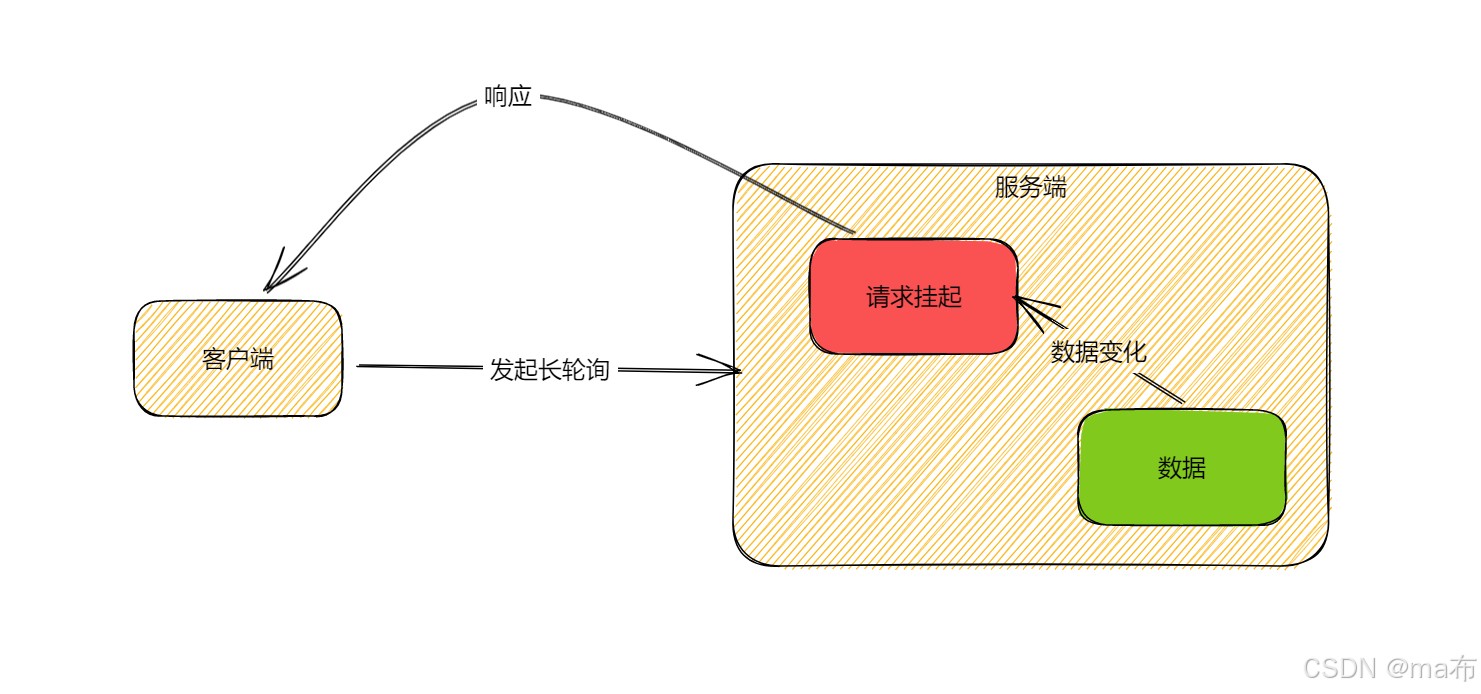

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

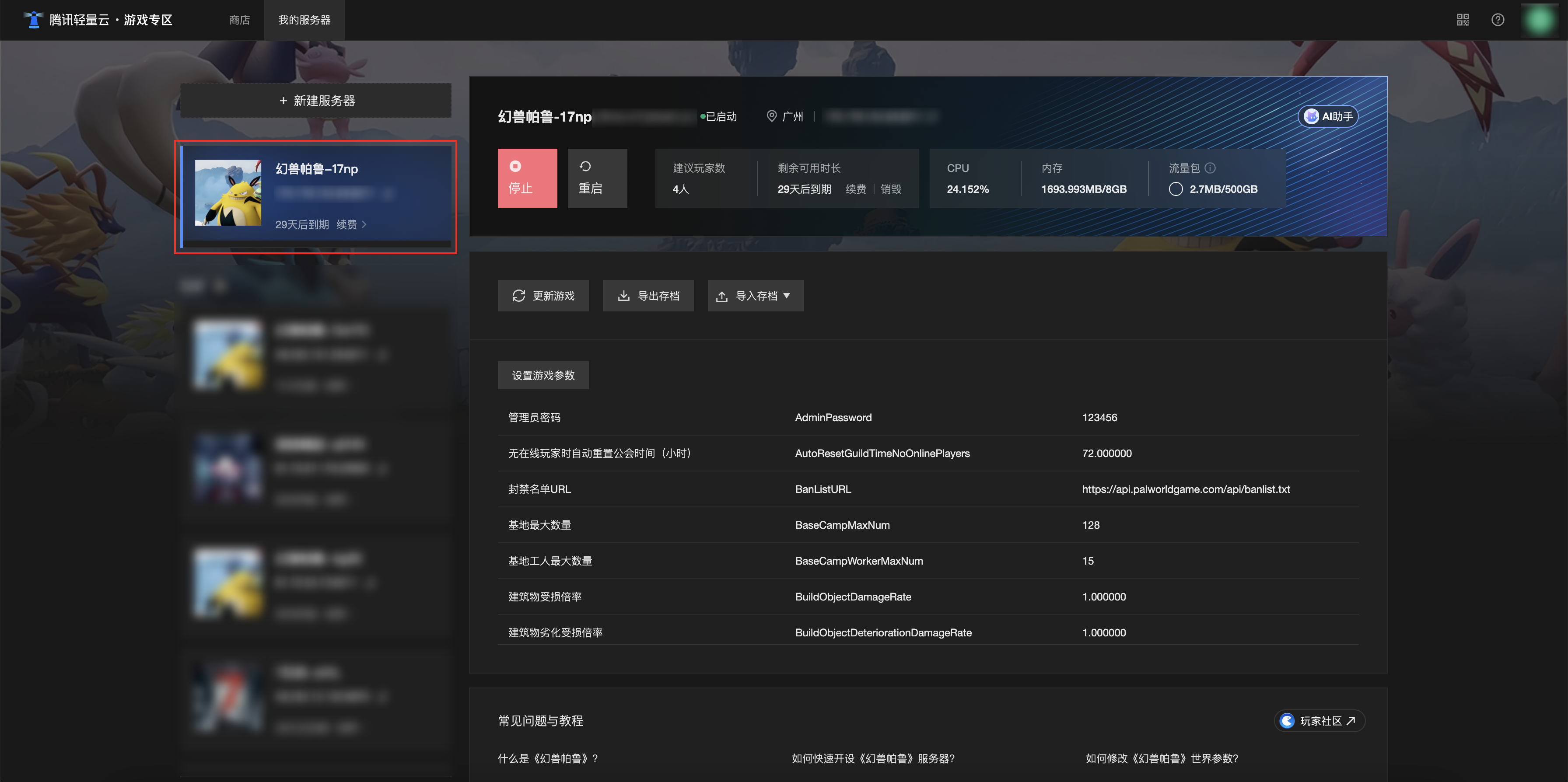

[Зона легкого облачного игрового сервера] Управление игровыми архивами