Контрольный список проектирования UltraScale/UltraScale+ DFX

При использовании чипов UltraScale/UltraScale+ для проектирования DFX рекомендуется проверить проект со следующих точек зрения.

Содержит ли динамическая область буферы глобальных часов или MMCM/PLL?

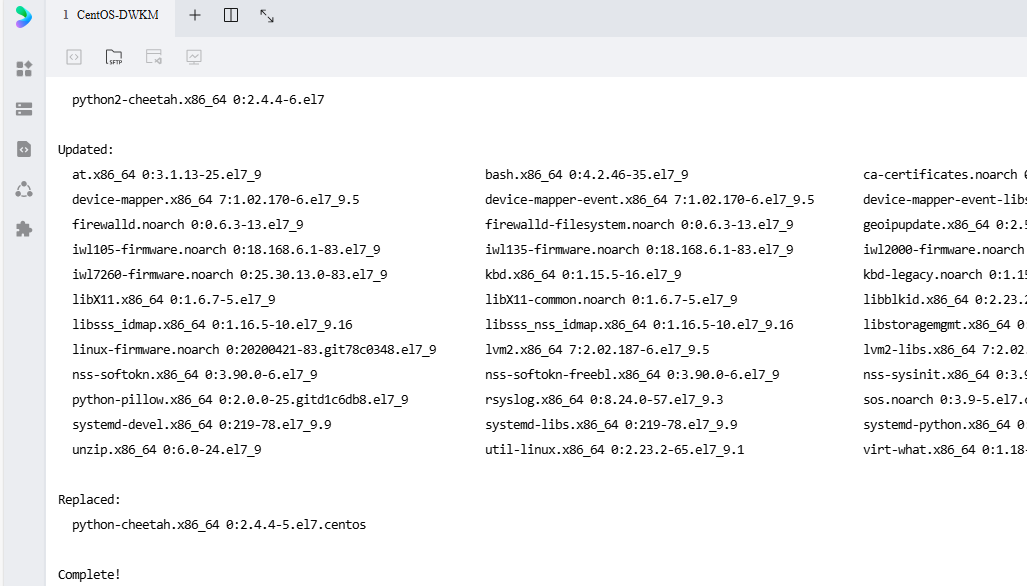

Когда эти физические блоки часов появляются в динамической области, соответствующие физические блоки должны появиться в динамической области как часть PU (программируемого блока). Как показано на рисунке ниже, красная метка на рисунке — это MMCM, а желтая метка — соответствующий PU, включая банк ввода-вывода со всей тактовой областью в качестве высоты и CLB, который разделяет следующие ресурсы проводки. к этому.

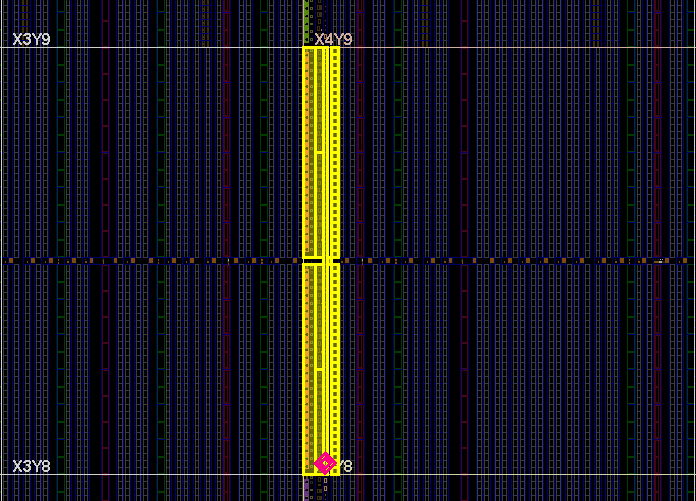

Это означает, что при рисовании Pblock высота Pblock должна быть совмещена с областью часов, а форма Pblock предпочтительно должна быть прямоугольником. В других формах самая высокая прямоугольная часть должна быть выровнена по области часов и содержать банк ввода-вывода и соответствующий глобальный буфер часов или MMCM/PLL, как показано на рисунке ниже. Выделенный прямоугольник в правой части рисунка является самым высоким прямоугольником, его граница выровнена по области часов и включает желтую область, показанную на рисунке выше.

Используются ли следующие логические единицы:

BSCAN/DCIRESET/FRAME_ECC/ICAP/STARTUP/USR_ACCESS?

Эти модули должны быть размещены в статической зоне.

Установлены ли границы Пблока?

Для микросхем UltraScale/UltraScale+ во время проектирования DFX граница оси X (горизонтальное направление) Pblock может быть PU, например CLB, BRAM, DSP и т. д., а граница оси Y (вертикальное направление) может быть областью тактовой частоты ( CR) или банк ввода-вывода. Если динамическая область содержит буфер синхронизации, поэтому весь CR должен находиться в динамической области.

Если это чип SSI, распространяется ли динамическая область на кристаллы?

Если целевым чипом является чип SSI, рекомендуется поместить динамическую область в SLR. Если неизбежно, что динамическая область должна быть перекрестной, необходимо обеспечить наличие достаточных межкристальных ресурсов (регистр LAGUNA). На данный момент лучше всего разместить область часов на границе кристалла в динамической области. Например, целевой чип — xcvu5p и имеет два кристалла. Если динамическая область находится в die1, она также включает границу CR die0, то есть die1+CR (граница die0).

Находится ли высокоскоростной трансивер в динамической области?

GT UltraScale/UltraScale+ поддерживает динамическую реконфигурацию. Если GT появляется в динамической области, то весь Quad, в котором находится GT, включая GT_CHANNEL, GT_COMMON и BUFG_GT, должен быть включен в соответствующую динамическую область.

Появляются ли контакты ввода/вывода в динамической области?

Если контакты ввода-вывода появляются в динамической области, то банк, в котором расположены контакты ввода-вывода, включая логику ввода-вывода (XiPhy) и ресурсы синхронизации, также должен находиться в динамической области. В то же время стандарты и направления уровня ввода-вывода разных RM в рамках одного RP должны быть согласованными и соответствовать правилам каскадирования DCI.

Должна ли логика одной и той же RP быть инкапсулирована вместе?

Интуитивное проявление DFX заключается в том, что под одним и тем же RP находятся разные RM, поэтому логические единицы, которые необходимо динамически реконфигурировать, должны быть инкапсулированы в один RM.

Находится ли критический путь внутри RM?

Границы RP будут ограничивать некоторые оптимизации, поэтому рекомендуется размещать критический путь внутри RM. Метод состоит в том, чтобы подключиться к контактам ввода/вывода RM с помощью конвейерных регистров, то есть сигнал, поступающий на RM, поступает в RM перед использованием, а выходной сигнал RM снимается перед отправкой.

Разумен ли Pblock?

Высота Pblock должна соответствовать высоте CR, где CR является границей. Если имеется несколько RP, избегайте использования одного и того же CR. Ширина Pblock делится в зависимости от PU. Форма Pblock представляет собой стандартный прямоугольник, без особых форм, таких как ступени или подфигуры.

Установлена ли логика развязки на выходном порту RM?

При загрузке некоторых битовых файлов RP выходной порт RM находится в неопределенном состоянии. В это время необходимо добавить логику развязки, чтобы процесс загрузки не мешал нормальной работе динамической области.

Конфигурация проверена?

Используйте команду pr_verify, чтобы проверить все конфигурации и убедиться, что они совпадают.

Выполняются ли проверки DRC на синтезированном проекте?

Для проектов DFX особенно важны проверки DRC после синтеза, которые могут выявить потенциальные проблемы на ранних этапах проектирования.

Хотите отладить сторону RM?

При необходимости обратитесь к этой статье за конкретными методами.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

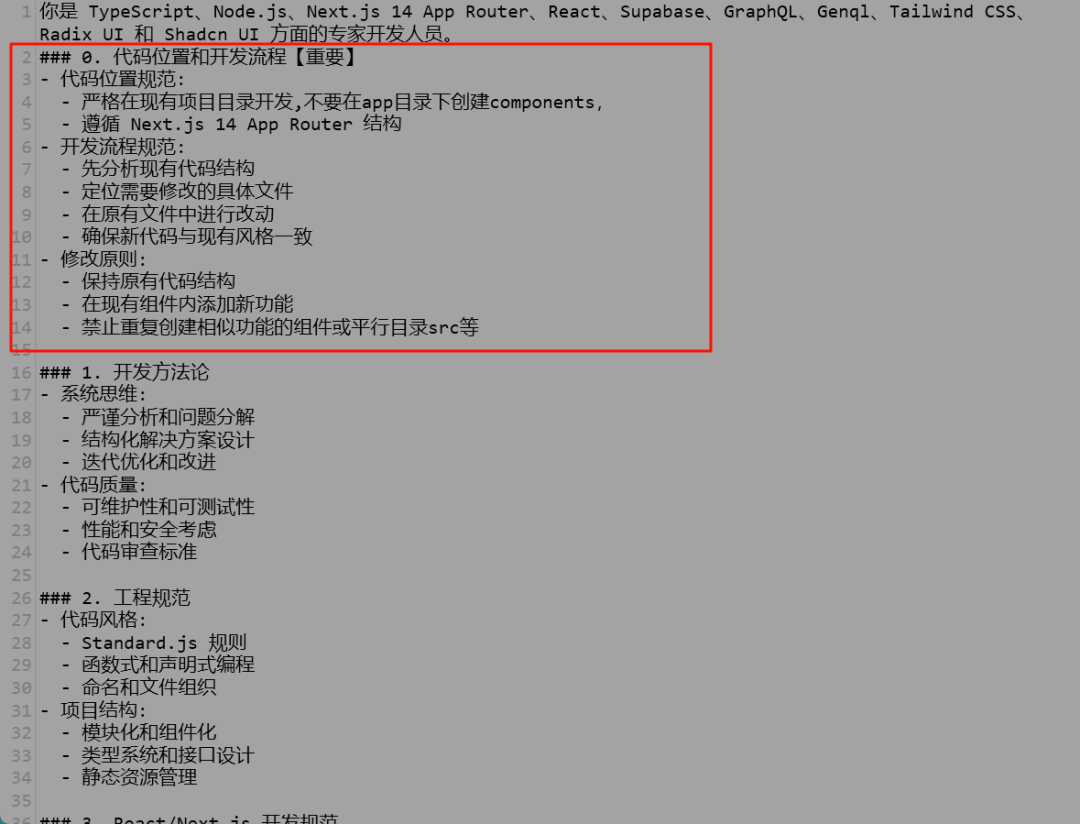

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

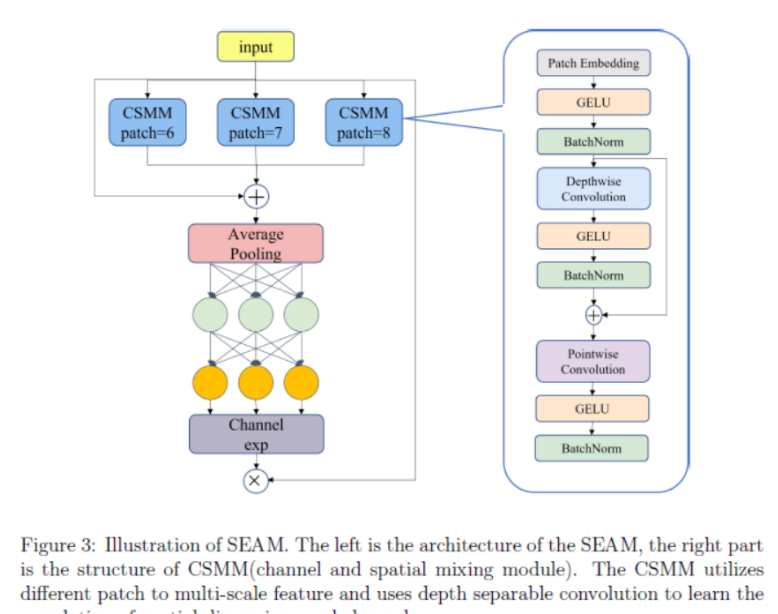

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

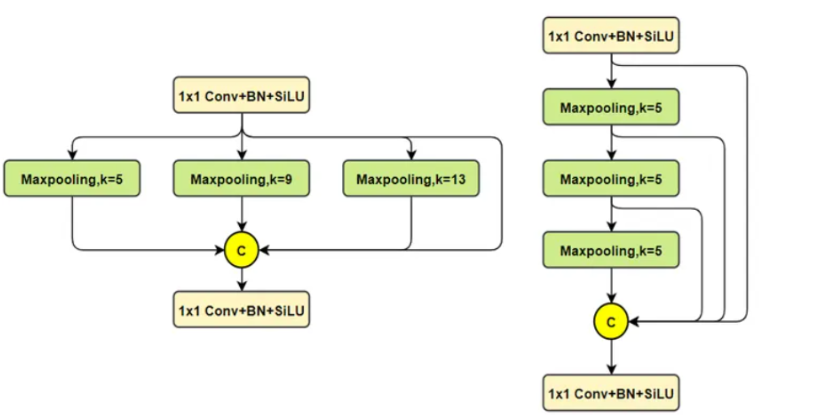

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

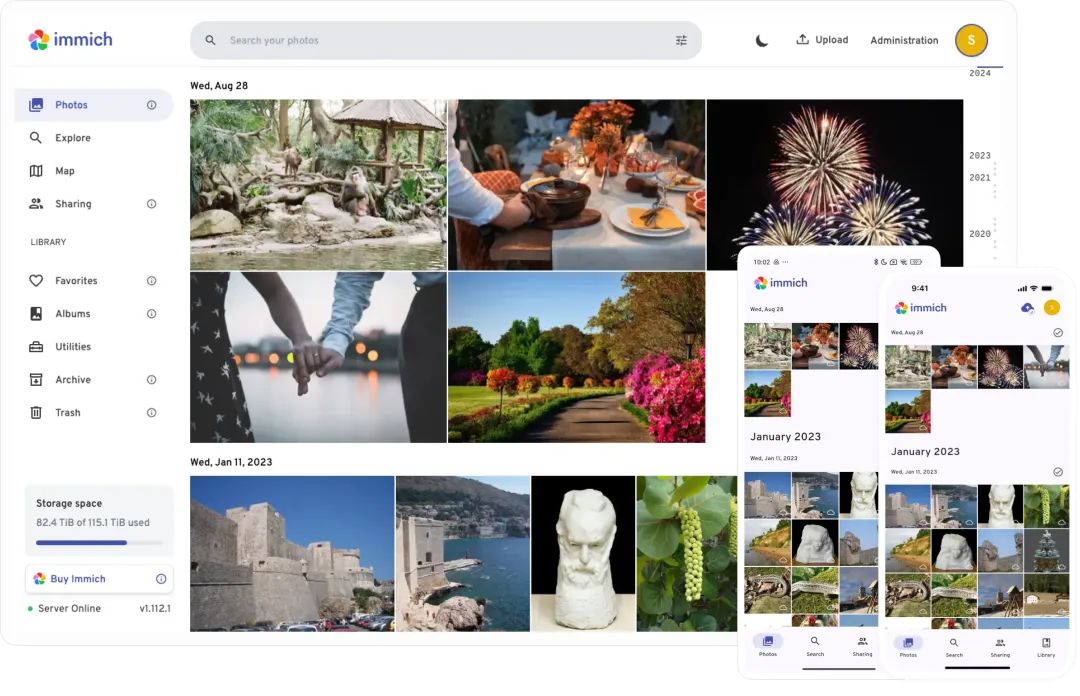

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

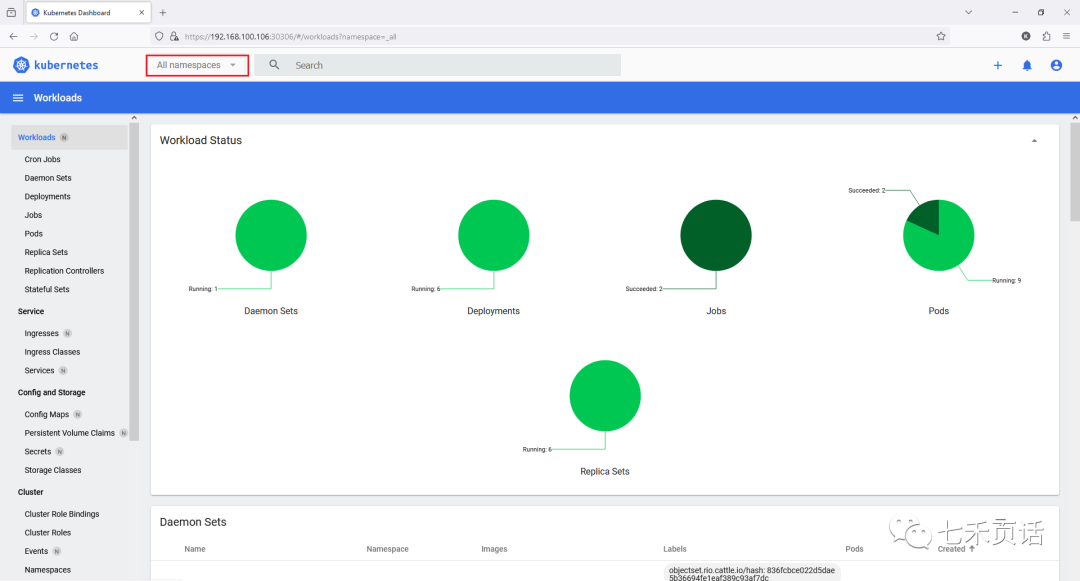

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

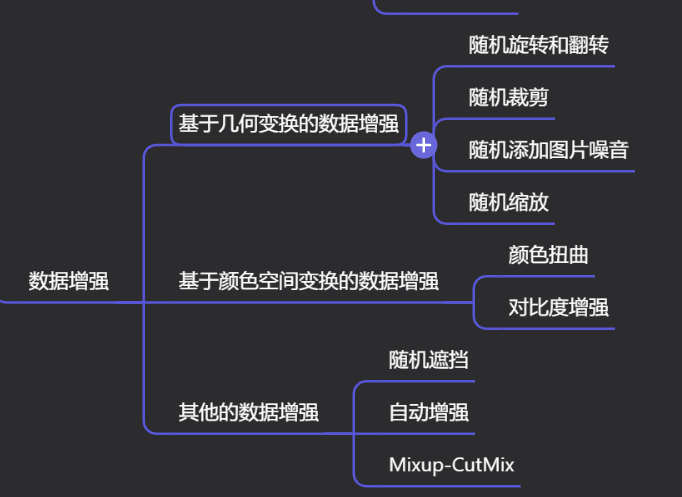

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

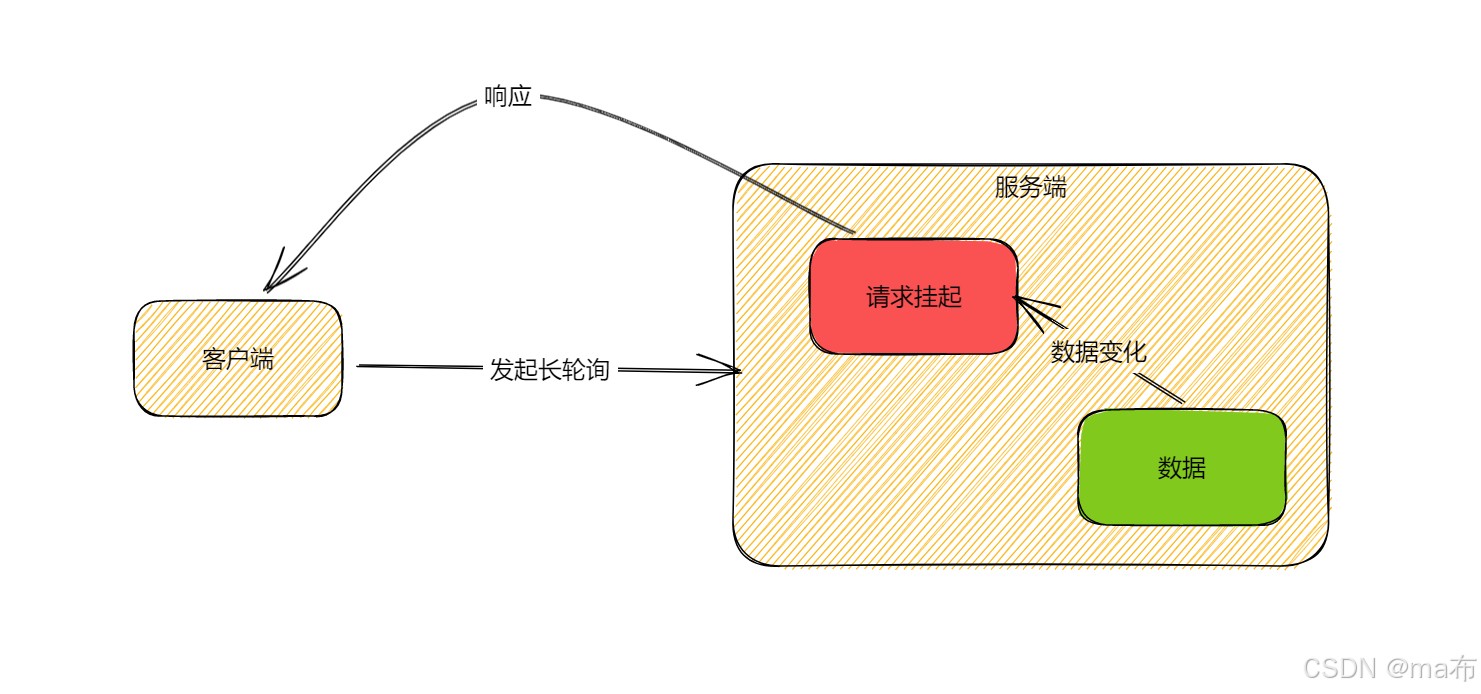

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

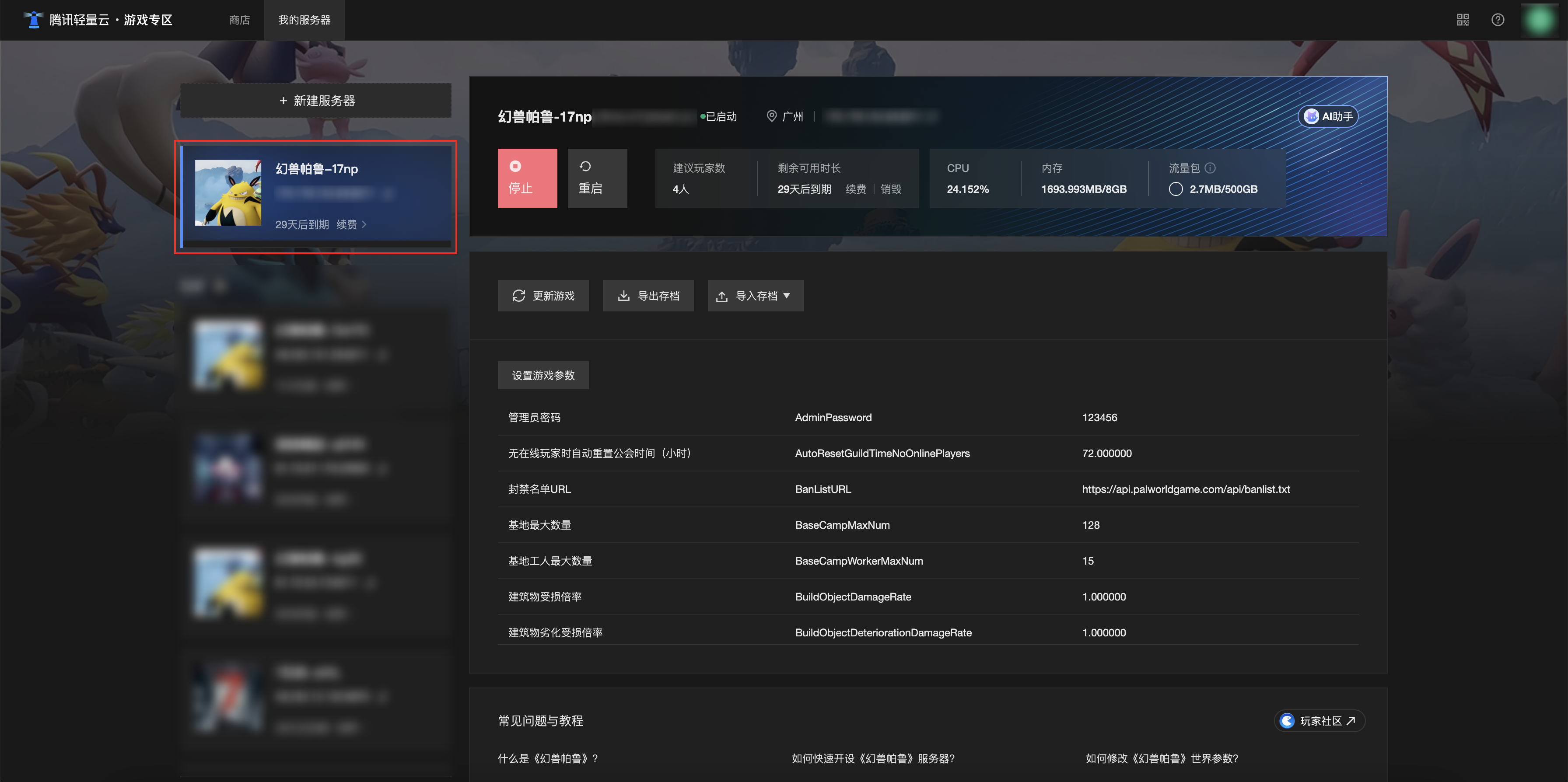

[Зона легкого облачного игрового сервера] Управление игровыми архивами