Каковы методы передачи данных между FPGA и CPU?

При проектировании ПЛИС, кроме некоторых алгоритмов\верификации и других приложений, взаимодействие данных (связь) между ПЛИС и контроллером требуется и в других случаях.

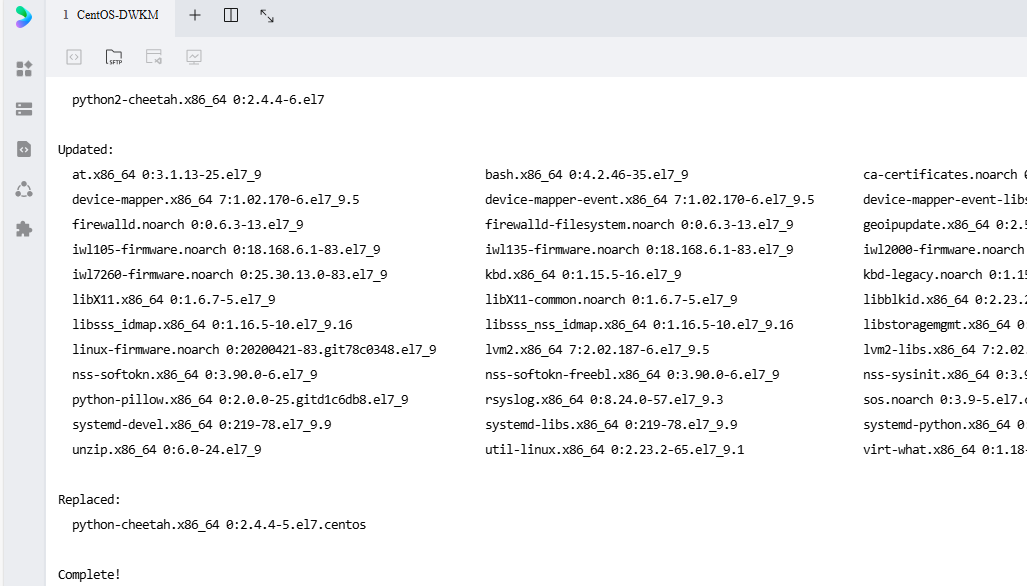

Вообще говоря, все цифровые коммуникационные интерфейсы ЦП могут взаимодействовать с FPGA. Здесь мы кратко классифицируем соответствующие интерфейсы. Интерфейсы здесь в основном относятся к межплатной связи, такие как 422, 485 и т.п. не будут описаны (протокол). слои — это все UART).

низкоскоростной интерфейс

Низкоскоростной интерфейс обычно используется в микроконтроллерах. При стыковке с FPGA он в основном осуществляет передачу небольших объемов данных.

Преимущество низкоскоростного интерфейса в том, что он прост.,Простота реализации, недостатки также очевидны;,Просто пропускная способность не высокая,Большие объемы данных не могут быть обработаны.

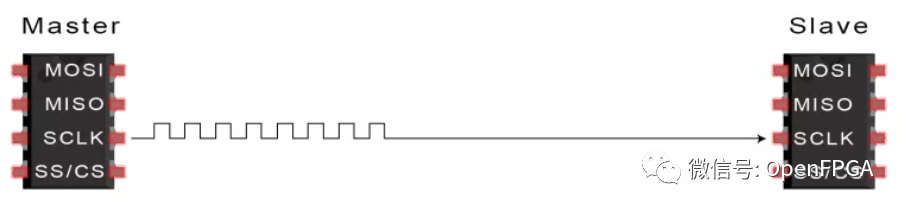

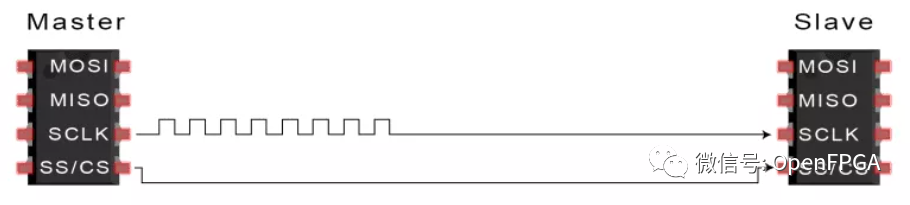

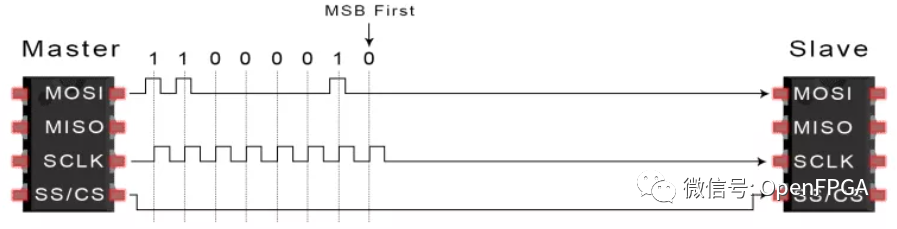

Здесь мы кратко поговорим о SPI и UART. SPI — это протокол синхронной связи, а UART — асинхронный протокол связи. Разница в том, существует ли общий тактовый сигнал.

Использование этих двух протоколов может относиться к следующему методу связи: Предположим, что связь осуществляется между FPGA и ЦП.,FPGA необходимо передавать напряжение и ток, собранные XADC, в ЦП для управления работоспособностью.,Здесь следует отметить два момента: во-первых, передача не обязательно должна осуществляться в режиме реального времени, во-вторых, объем данных невелик;,Так что целесообразнее выбирать низкоскоростной интерфейс.,Разница в передаче при выборе SPI и UART следующая:

SPI-интерфейс:

ЦП вызывает выстрелы и должен сначала отправить тактовый сигнал в FPGA:

Затем включите CS:

Затем MOSI процессора отправляет данные в FPGA:

Когда MISO FPGA необходимо вернуть данные, он синхронно передает данные обратно в ЦП. Если MOSI не отправляет данные, MISO не может активно отправлять данные.

UART-интерфейс

UART легче понять. ЦП и FPGA согласовывают хорошую скорость передачи данных. Когда FPGA хочет отправить данные, она просто отправляет данные в ЦП (ЦП необходимо использовать триггеры прерываний для получения данных).

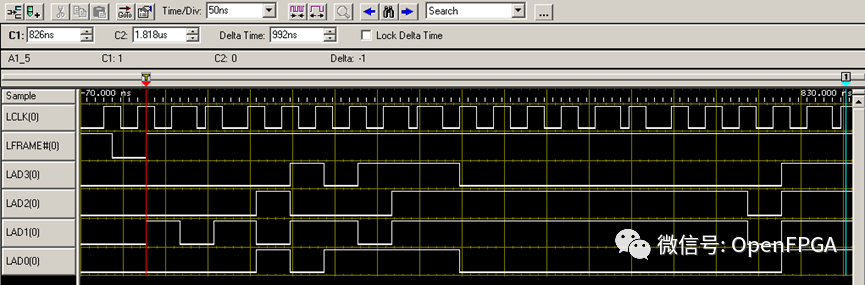

LPC

Наконец, давайте кратко поговорим о LPC (Low Pin Count). LPC — это общий интерфейс матричной клавиатуры и т. д., которые передаются на южный мост через LPC.

В настоящее время я в основном использую его для связи с FT CPU. В этом аспекте я использую его нечасто, поэтому не буду описывать его подробно.

низкоскоростной интерфейсвыполнить

Что касается реализации этих протоколов, вы можете прочитать следующую статью, в которой подробно рассматривается разница между RS232 и UART в UART.

Один пример дизайна в день — 30 000 слов, объясняющих UART и примеры.

Один пример разработки протокола Day-IIC и реализации FPGA.

Один пример проектирования: протокол Day-SPI и реализация FPGA.

Далеевысокоскоростной интерфейс

высокоскоростной интерфейс

Большая часть высокоскоростного интерфейса может быть реализована через Serdes в FPGA. Распространенными являются PCIe и SRIO, а AXI также очень часто используется в ZYNQ.

Для PowerPC можно использовать PLB; для новейшей FPGA Intel также обычно используется QPI.

Для передачи видео также очень распространены интерфейсы MIPI, BT.656, BT.1120.

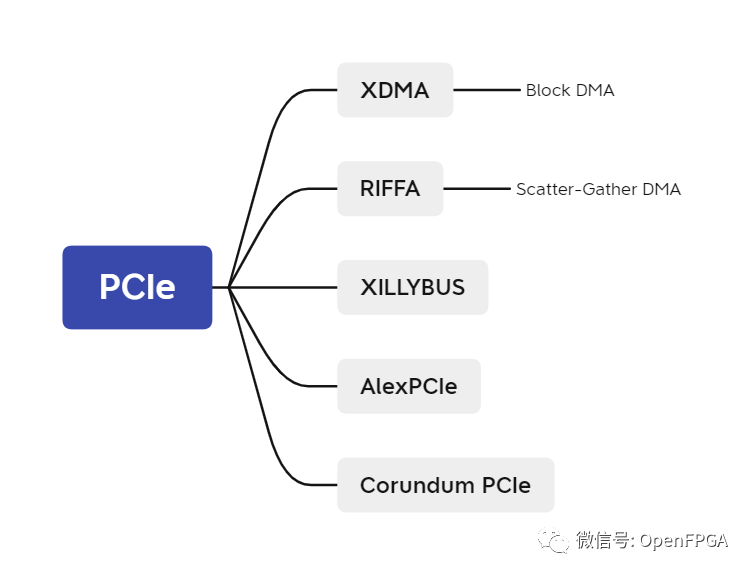

высокоскоростной интерфейс Мы представляем только PCIe,Это также очень распространенная передача данных.,В картах-ускорителях и дата-центрах,Это все ядро.

Сложность PCIe заключается в общей архитектуре и драйвере на стороне процессора. В настоящее время DMA обычно используется в архитектуре PCIe. Что касается причины, я не буду ее анализировать. В любом случае, преимущества очень очевидны.

Все до сих пор находятся в состоянии «паники» по поводу PCIe, но вам не о чем беспокоиться. Вот некоторые часто используемые архитектуры:

Все вышеперечисленные проекты на основе PCIe представляют собой очень зрелые архитектуры, и они также являются основной причиной популярности интерфейса PCIe в настоящее время в FPGA. Эти архитектуры применяются во многих проектах.

Что касается RIFFA и Алекса, вы можете ознакомиться со следующей вступительной статьей:

Отличный Введение в проекты Verilog/FPGA с открытым исходным кодом (1)-PCIe-коммуникация

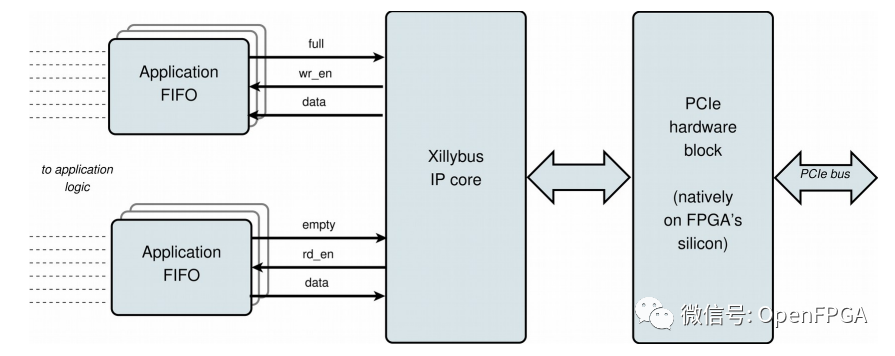

Ниже представлена архитектура XILLYBUS:

Официальный сайт:

http://xillybus.com/

Что касается Corundum, вы можете просмотреть следующую статью: Знакомство с Corundum, первым в отрасли сетевым адаптером 100 Гбит/с с открытым исходным кодом.

Подвести итог

Приведенное выше введение охватывает только некоторые распространенные интерфейсы, и существует множество других, менее часто используемых шин, таких как шина FSB, шина HT, шина DMI и т. д., которые также могут осуществлять связь между ЦП и FPGA.

На сегодня это все. Я убит горем Суй Суанси. С нетерпением жду встречи с вами в следующей статье.

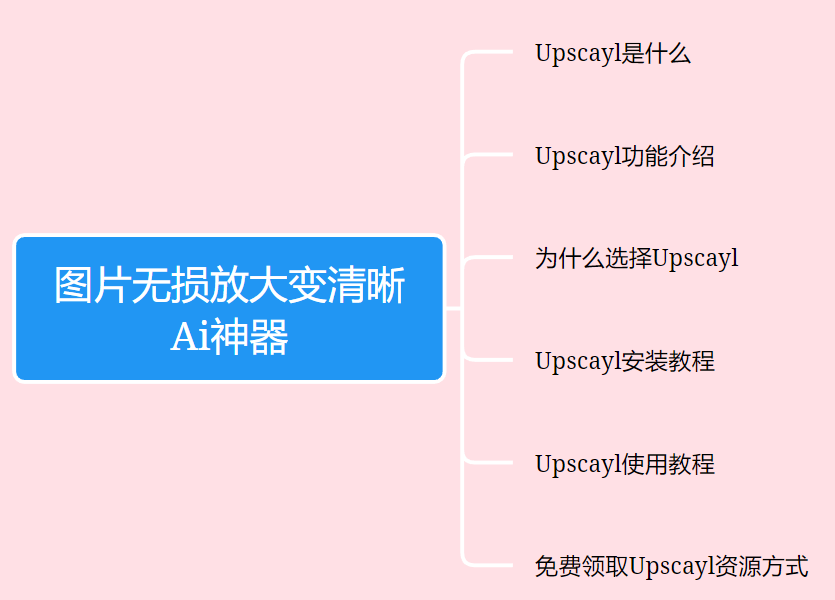

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

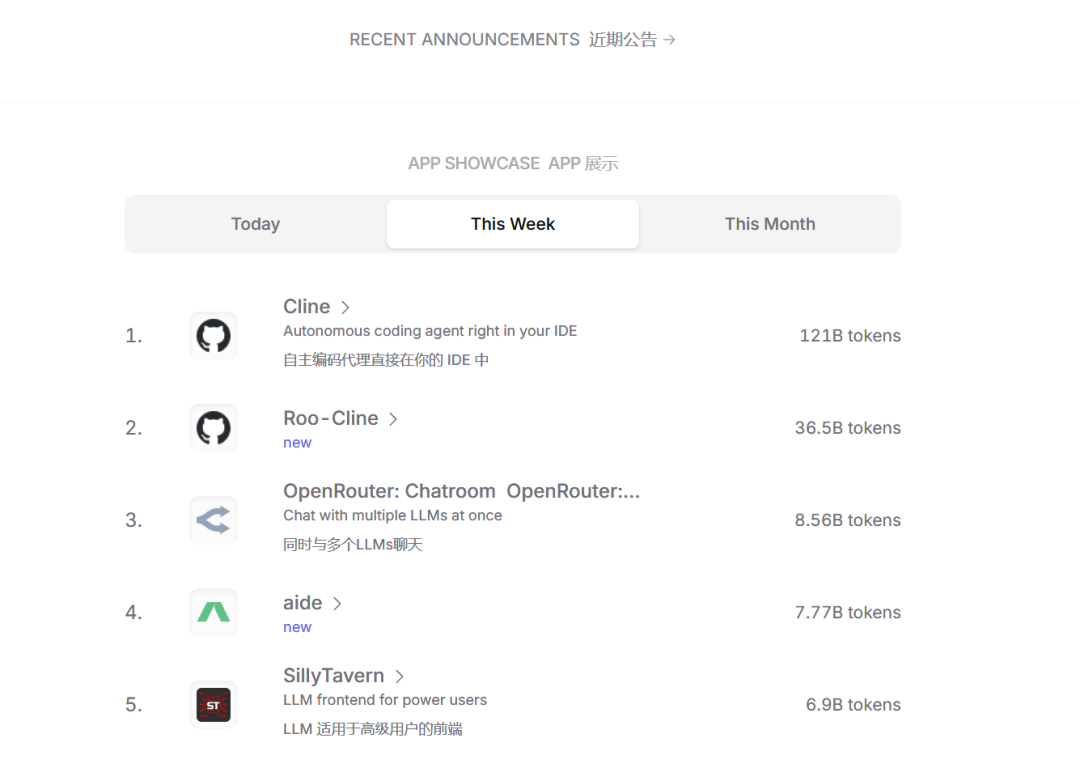

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

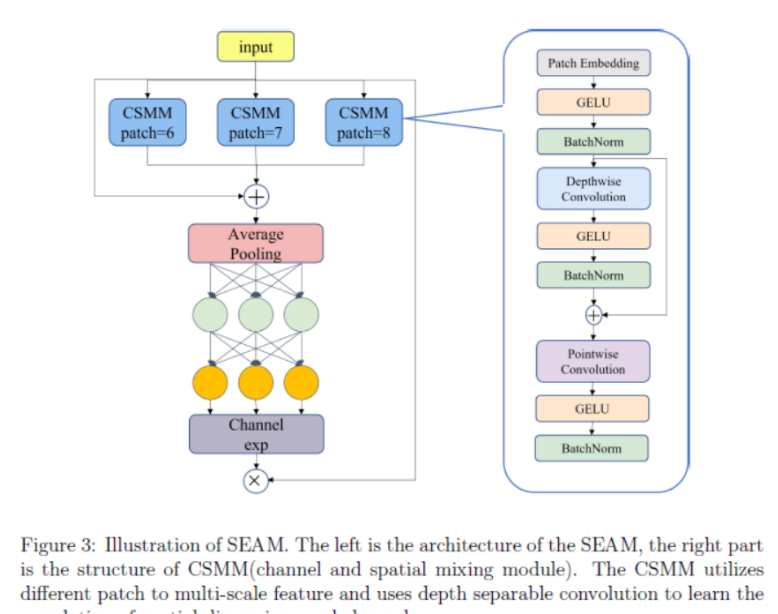

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

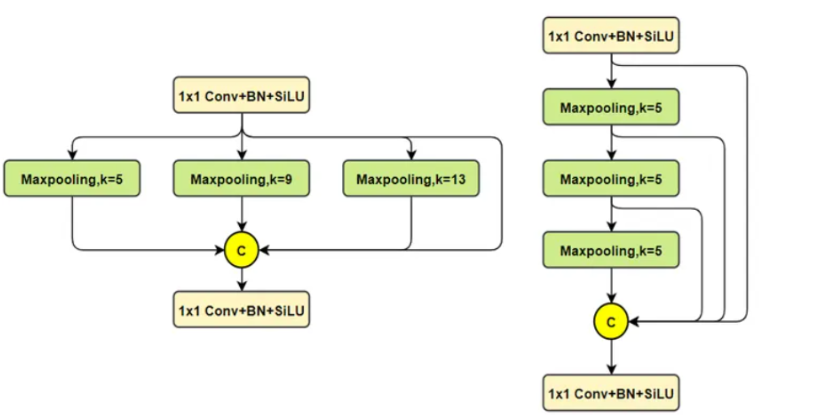

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

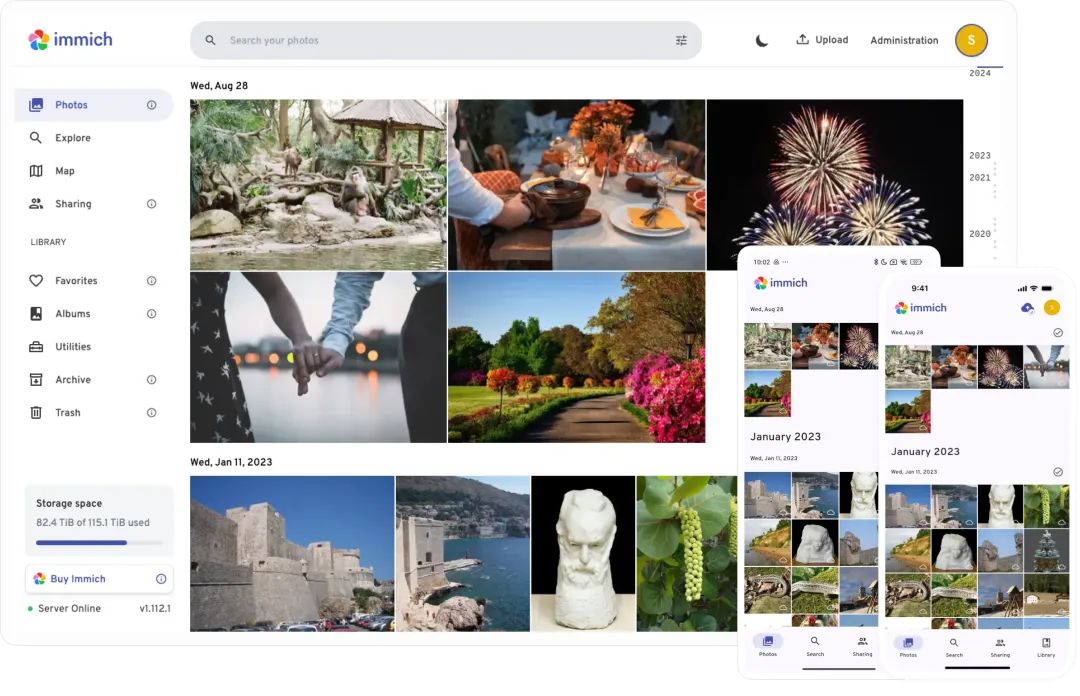

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

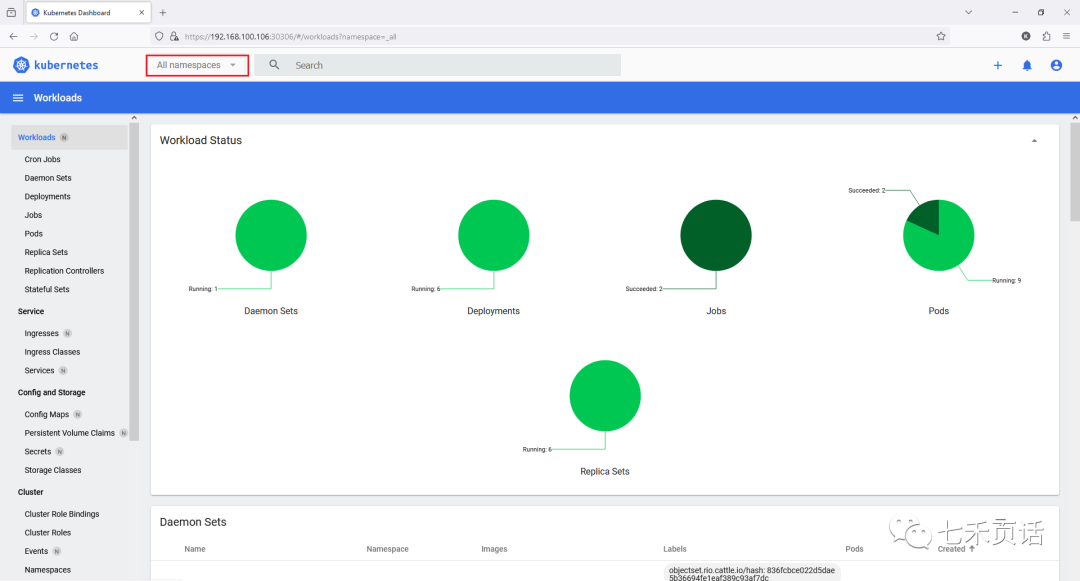

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

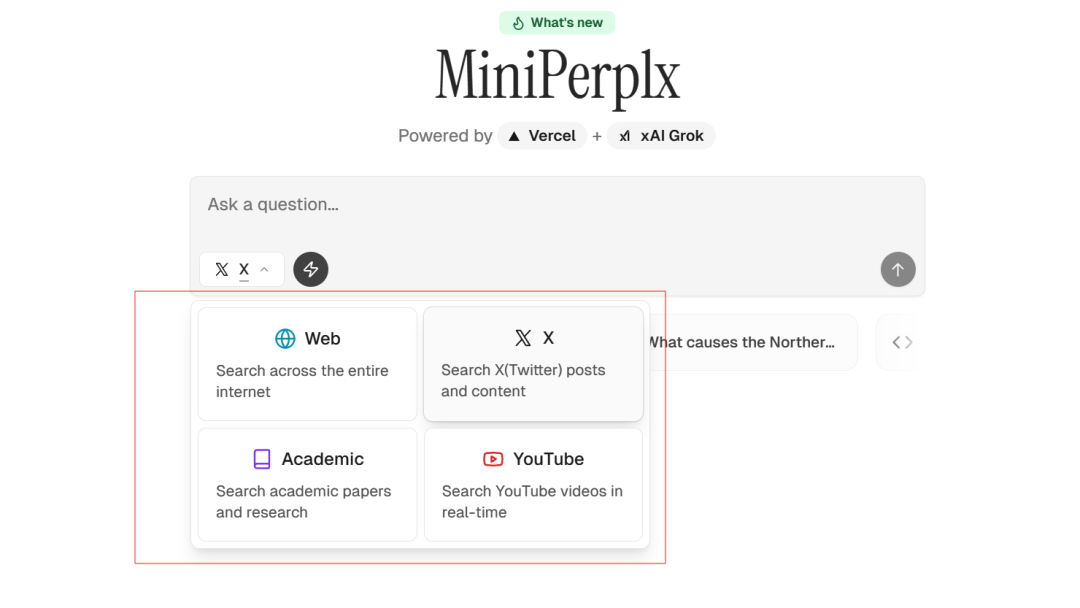

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

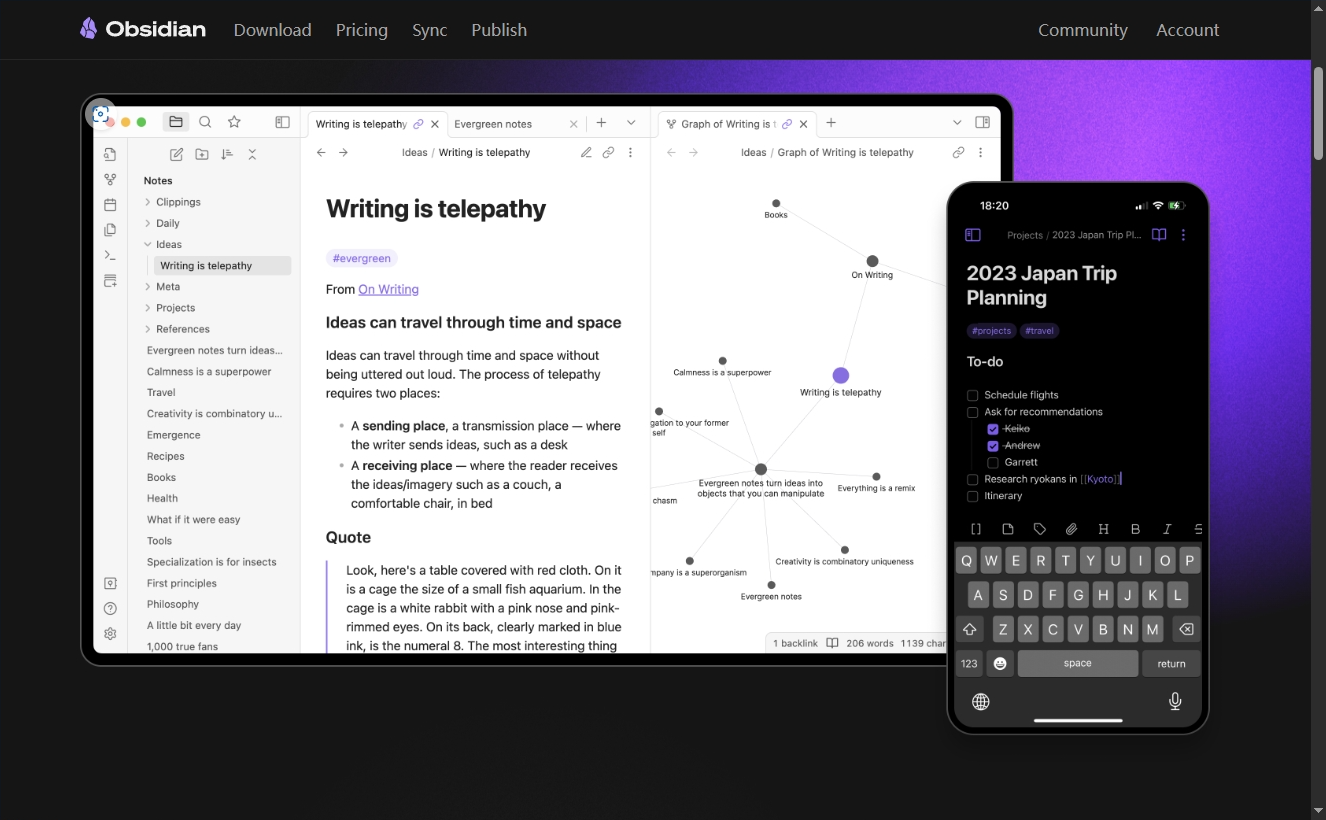

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

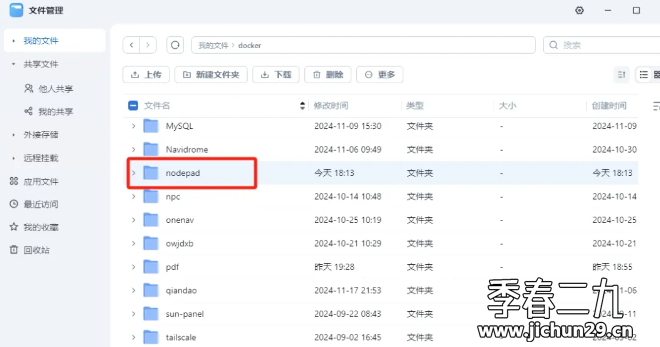

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

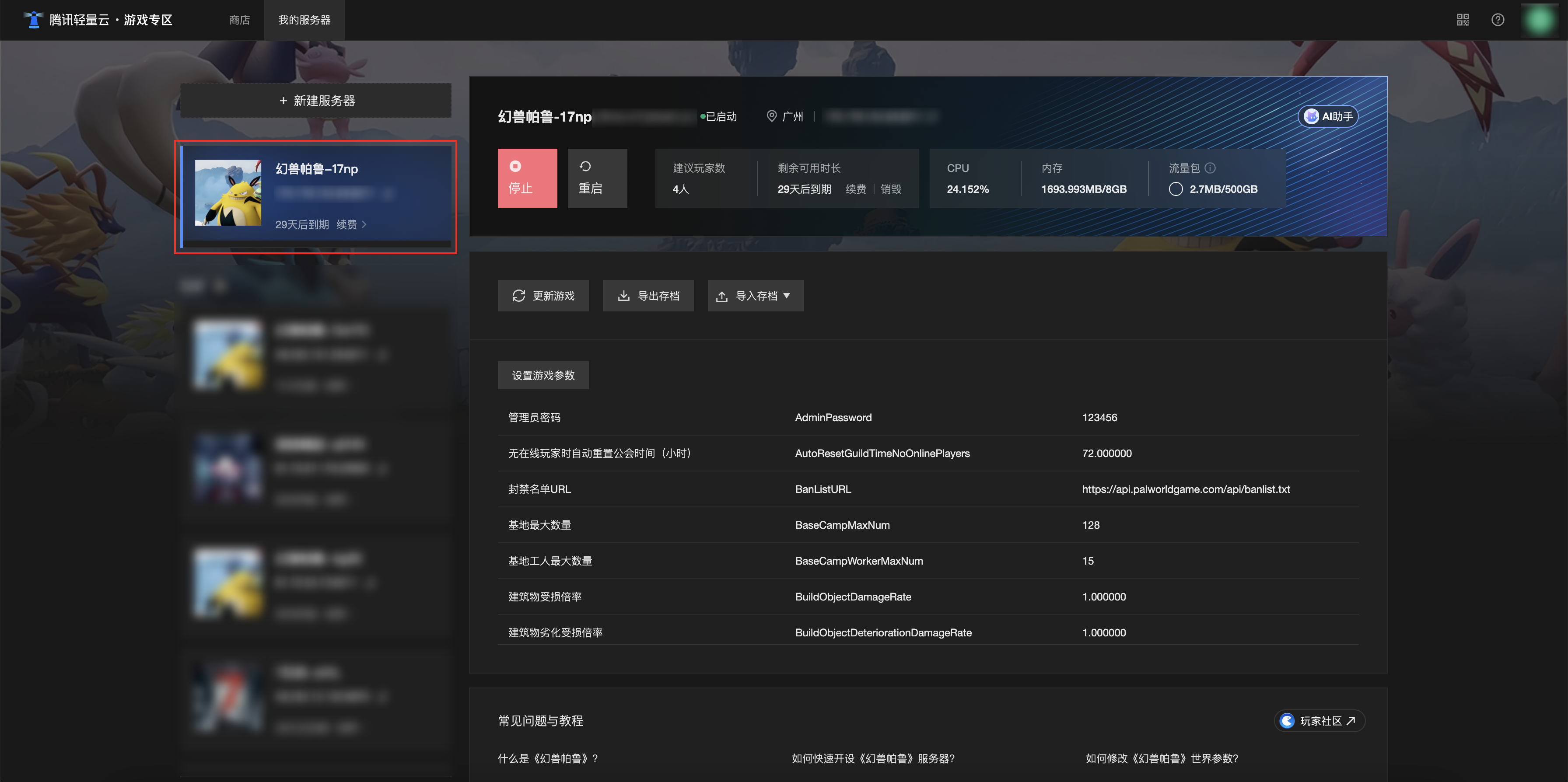

[Зона легкого облачного игрового сервера] Управление игровыми архивами