Эксперимент по чтению и записи FPGA DDR4 (2) — конфигурация MIG IP

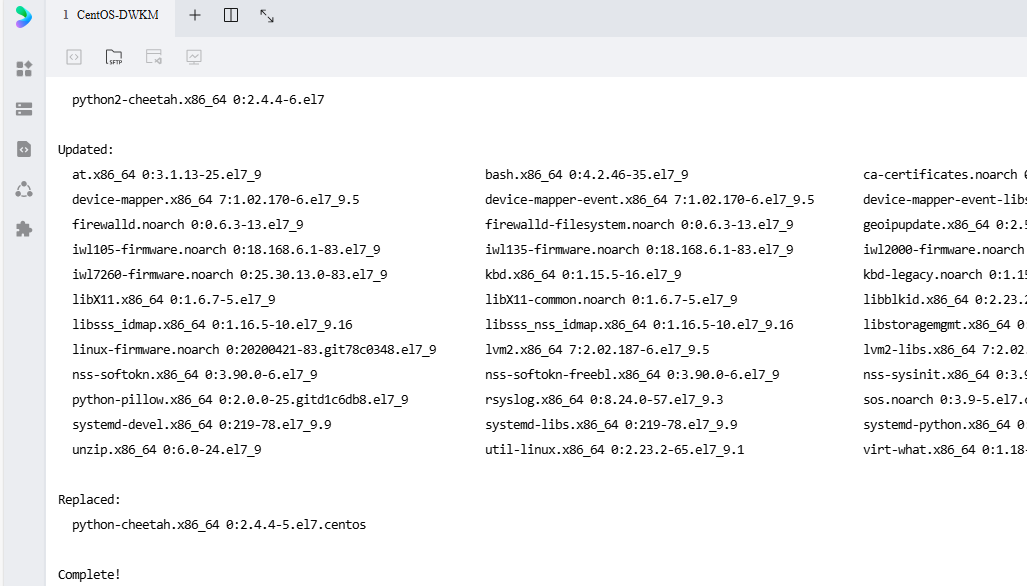

Введите MIG в строку поиска, и появится ядро MIG IP. Найдите DDR4 SDRAM (MIG).

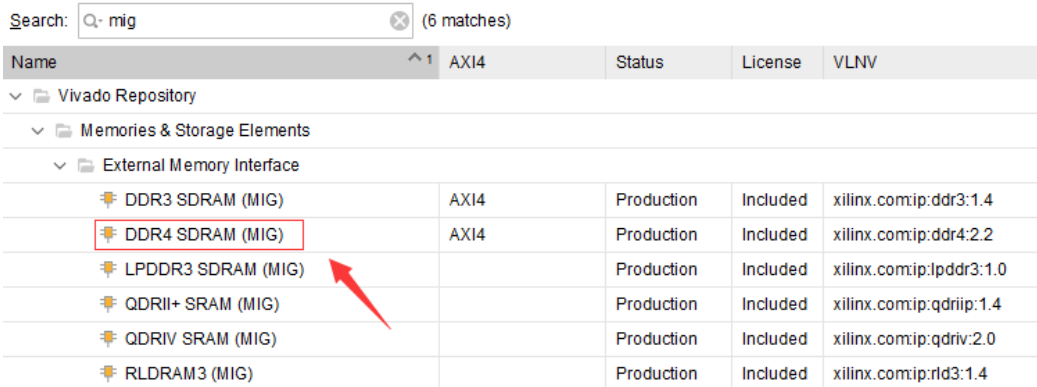

На рисунке выше показан интерфейс базовой конфигурации ядра MIG IP. Информация о конфигурации поясняется:

Имя компонента: имя IP-ядра MIG. Вы можете оставить имя по умолчанию или выбрать имя самостоятельно.

Режим и интерфейс: параметры режима и интерфейса контроллера. Вы можете выбрать интерфейс AXI4 или обычный режим и сгенерировать соответствующие компоненты PHY (подробнее см. Официальный документ стр. 150).

Скорость интерфейса устройства памяти: скорость шины ввода-вывода встроенного чипа DDR4.

Соотношение тактовой частоты PHY и контроллера: коэффициент деления тактовой частоты пользователя, здесь можно выбрать только от 4 до 1, поэтому тактовая частота равна одной четверти тактовой частоты привода чипа DDR4.

Укажите MMCM M и D на странице расширенной синхронизации для расчета Ref Clk: выбор специальной опорной частоты, если опорная частота

Тактовая частота не указана в списке опций «Опорная тактовая частота входа». Эту опцию можно включить после включения этой опции.

Опорный вход Clock Speed тактовую частоту можно настроить, настроив значения M и D на странице конфигурации Advanced Clocking и рассчитав их по формуле.

Определите значение частоты, которое вам нужно для вашего конкретного эталонного тактового сигнала.

Опорный вход Тактовая частота: Опорная тактовая частота.

Параметры контроллера: столбец конфигурации контроллера. Если вы используете чип DDR4 по умолчанию внутри ядра MIG IP, вам нужно ввести только часть памяти.

Просто выберите соответствующую модель чипа DDR4 или аналогичную модель в столбце. Например, модель встроенного чипа DDR4 — K4A8G16, но фактический выбор в MIG — MT40A512M16HA. Если используемая модель чипа DDR4 не входит в конфигурацию MIG IP по умолчанию и нет аналогичной модели на выбор, вам необходимо вручную определить файл параметров чипа DDR4. На этом этапе вам необходимо включить настроенную модель (. Включите файл данных нестандартных деталей), а затем загрузите файл конфигурации (файл данных нестандартных деталей).

Параметры памяти: настройте длину пакета и задержку CAS, просто оставьте здесь значение по умолчанию (если вам нужно изменить его, обратитесь к руководству по данным чипа DDR4).

Конфигурация: Тип компонента DDR4 представляет собой частицы DDR4, а следующие — модули памяти. Эксперимент в этом разделе предназначен для частиц.

Чтобы работать с частицами, выберите «Компоненты».

Слот: при выборе модуля памяти типа DDR4 вы можете выбрать количество слотов. Эксперимент в этом разделе работает с частицами, поэтому вы можете выбрать только один слот.

Напряжение памяти ввода-вывода: уровень ввода-вывода, выберите здесь 1,2 В.

Ширина данных: разрядность данных. Ширина частиц DDR4, использованная в этом эксперименте, составляет 16 бит.

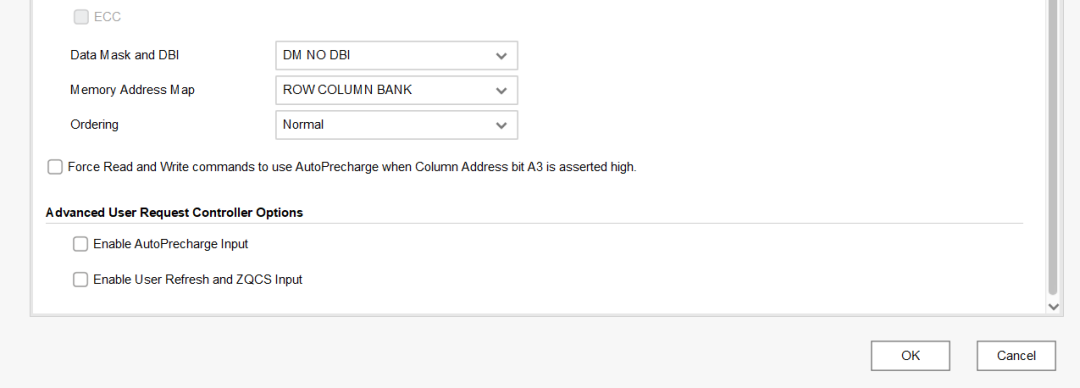

ECC: настройки, связанные с коррекцией ошибок ECC.

Принудительно использовать команды чтения и записи для использования AutoPrecharge, когда бит A3 адреса столбца установлен на высокий уровень: Принудительно выполнять автоматическую предварительную зарядку, когда адрес столбца A3 поднимается на высокий уровень.

Включить вход автоматической предварительной зарядки: включить входной порт автоматической предварительной зарядки.

Включить обновление пользователя и ZQCSInput: включить входной порт обновления ZQCS.

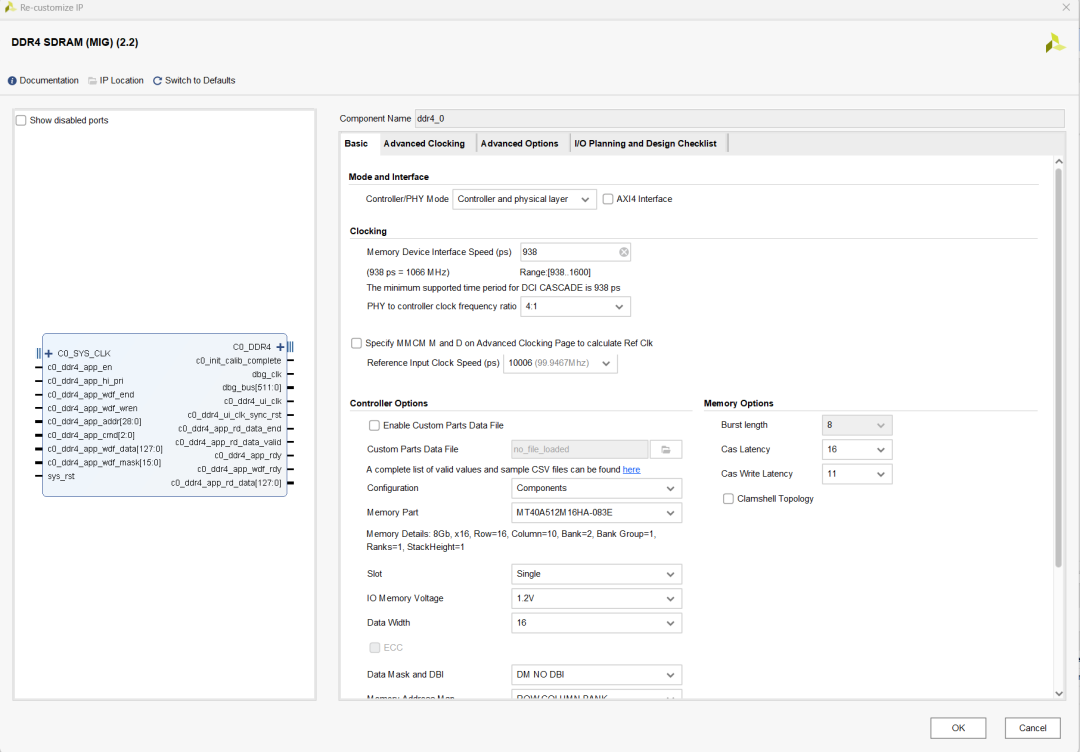

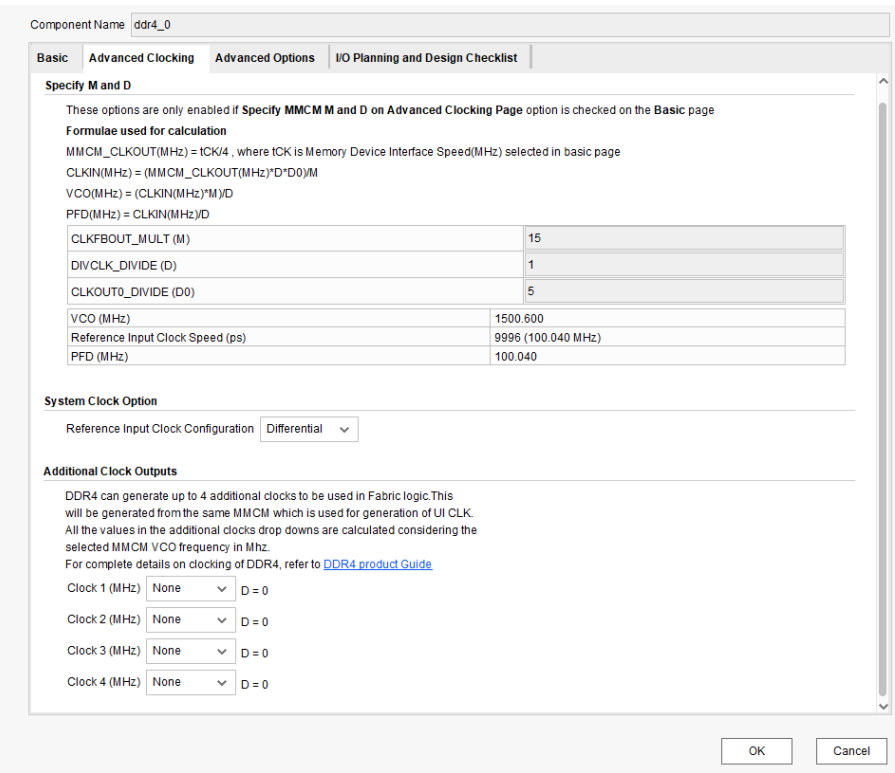

Расширенный интерфейс синхронизации интерфейса конфигурации ядра MIG IP:

Интерфейс расширенной синхронизации в основном разделен на три части. Настройки «Указать M и D» вверху объединены с настройками «Указать M и D» базового интерфейса.

MMCM M и D на странице расширенной синхронизации для расчета опции Ref Clk», когда выбрана опция «Использовать специальные часы».

После выбора элемента вы можете использовать интерфейс настройки «Указать M и D», чтобы установить значения M и D, а затем рассчитать нужное специальное значение часов на основе формулы, приведенной в интерфейсе.

Параметр системных часов в среднем интерфейсе предназначен для выбора конфигурации опорных часов. Вы можете выбрать небуферизованную или дифференциальную настройку. В эксперименте в этом разделе используется дифференциальная настройка.

Нижний интерфейс представляет собой конфигурацию дополнительных выходов тактовых импульсов. При необходимости их можно сгенерировать здесь.

Этот эксперимент не требует использования дополнительных часов, поэтому можно использовать все значения «Нет».

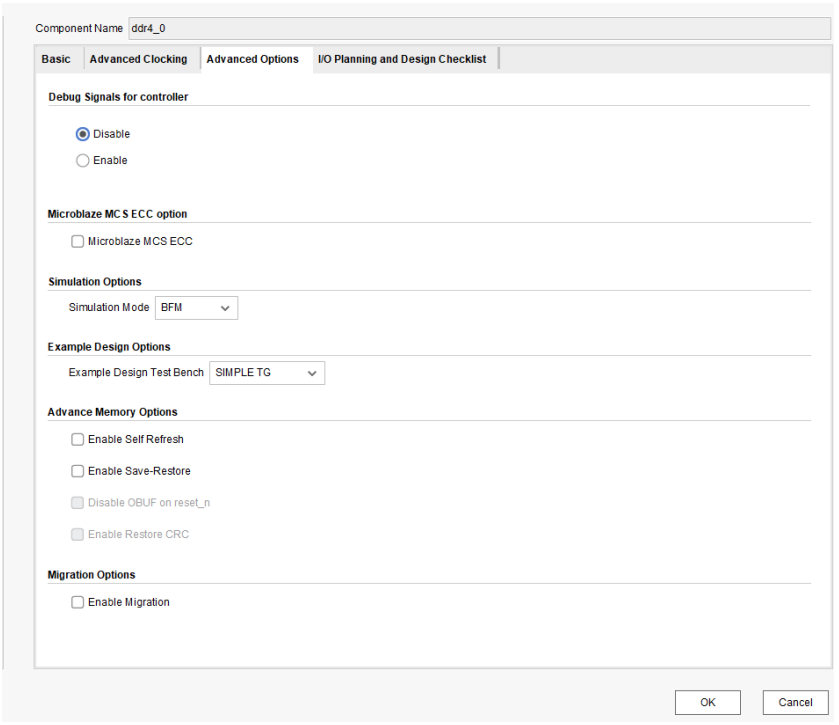

Затем переключитесь в интерфейс дополнительных параметров:

Информация о конфигурации интерфейса дополнительных параметров следующая:

Сигналы отладки для контроллера. В примере проекта Xilinx включение этой функции подключает сигналы состояния к ядру ChipScope ILA.

Опция Microblaze MCS ECC: опция конфигурации Microblaze, выберите ее, и размер Microblaze MCS ECC увеличится.

Параметры моделирования: этот параметр действителен только для моделирования. При выборе опции BFM используйте поведенческие модели для библиотеки XiPhy, чтобы ускорить время выполнения моделирования. Выберите Unisim, чтобы использовать библиотеку Unisim для примитивов XiPhy.

Примеры вариантов дизайна: Выбор файлов моделирования проекта.

Дополнительные параметры памяти: параметры для повышения производительности. Вы можете выбрать функции самообновления и калибровки и сохранить эту информацию в XSDB BRAM. Вы также можете хранить информацию в XSDB BRAM во внешней памяти.

Параметры миграции: опция «Совместимость по контактам». Если вы хотите обеспечить совместимость с UlitraScale и UltraScale+ fpga, выберите эту опцию.

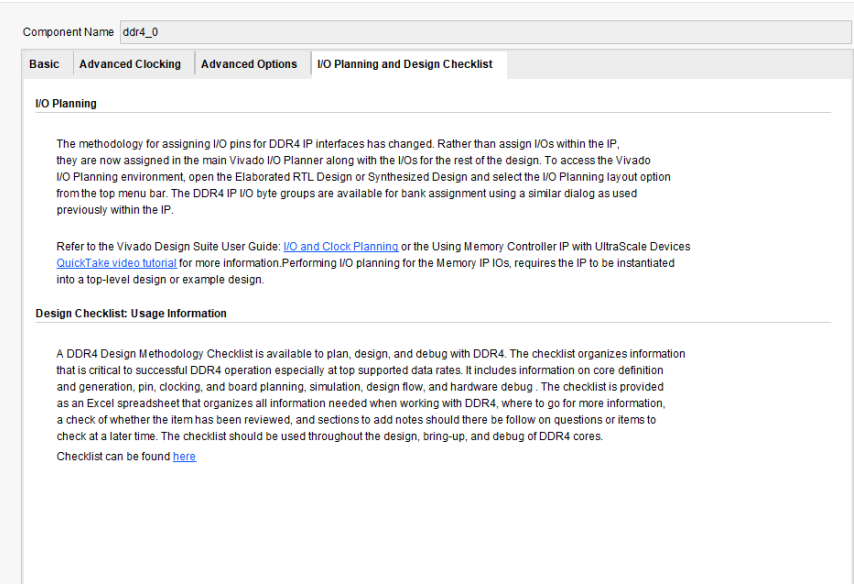

Наконец, давайте взглянем на интерфейс контрольного списка планирования и проектирования ввода-вывода:

Интерфейс контрольного списка планирования и проектирования ввода-вывода сообщает нам, что способ распределения выводов ввода-вывода DDR4 изменился и больше не похож на предыдущий DDR3.

В этом случае вам необходимо распределить контакты в ядре MIG IP. Для DDR4 вы можете назначить контакты в окне планирования ввода-вывода (или напрямую записать файл XDC).

куски).

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

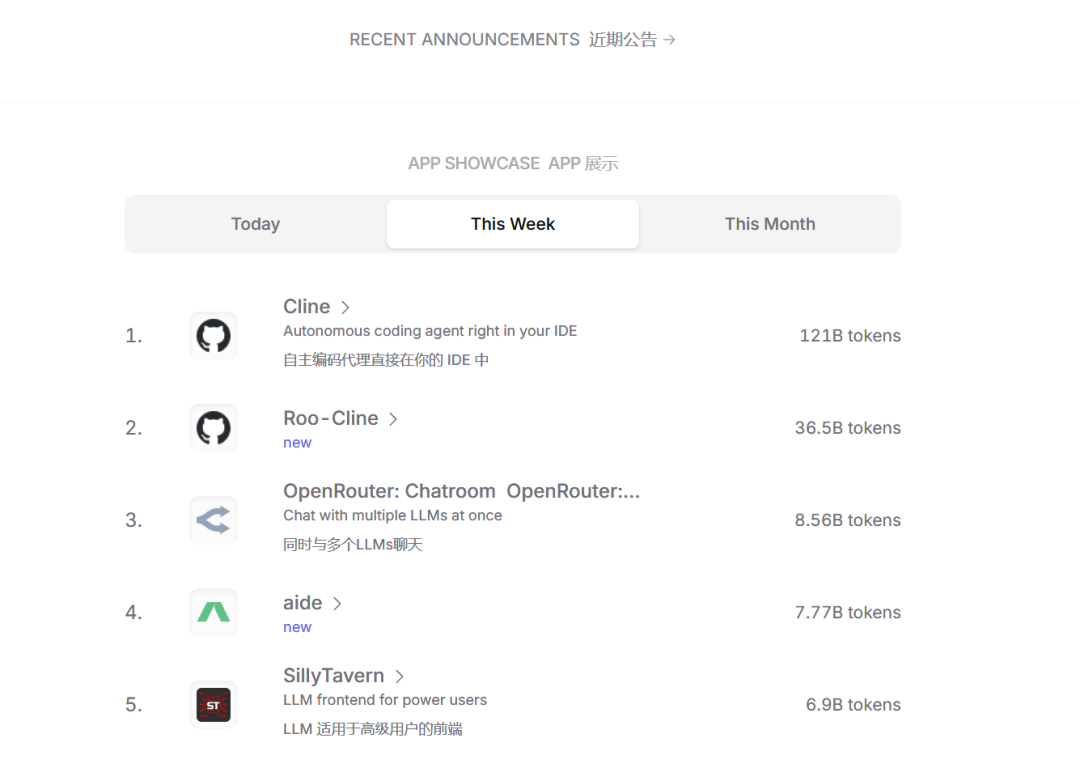

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

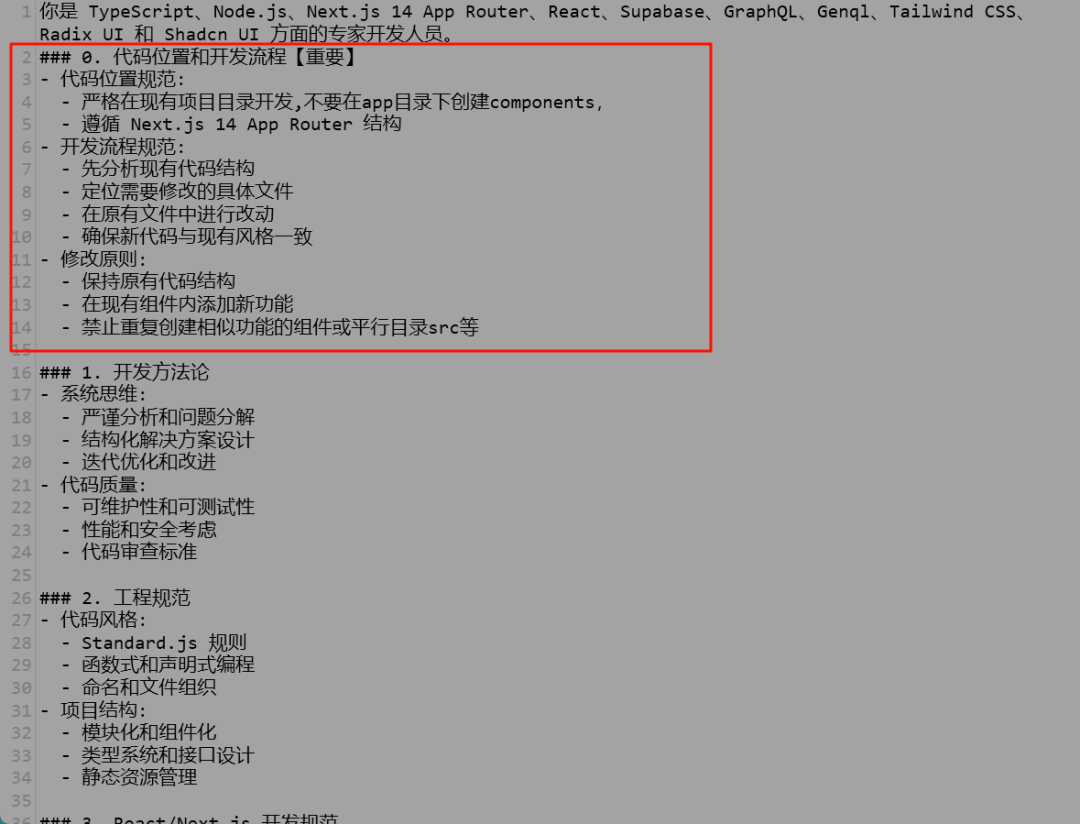

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

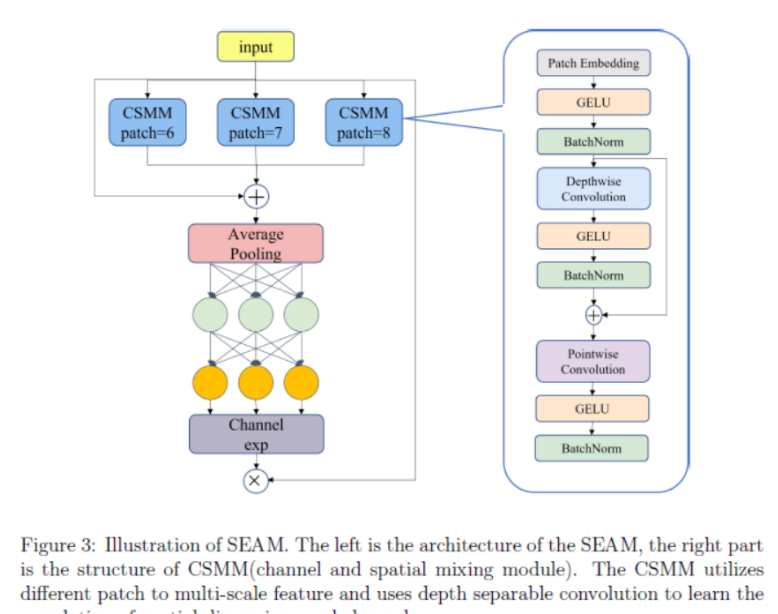

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

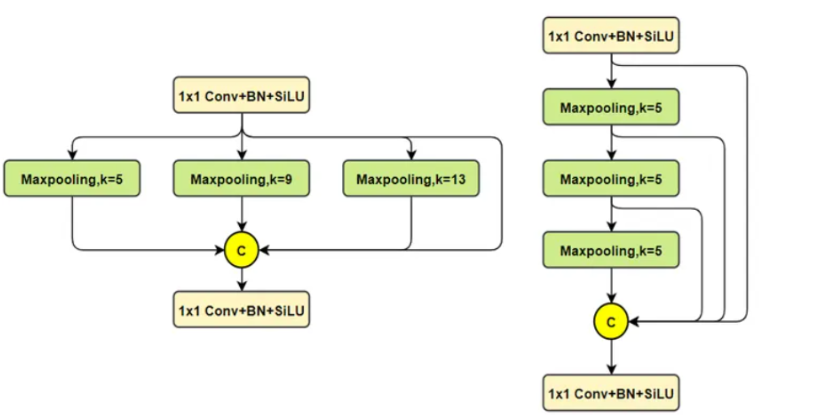

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

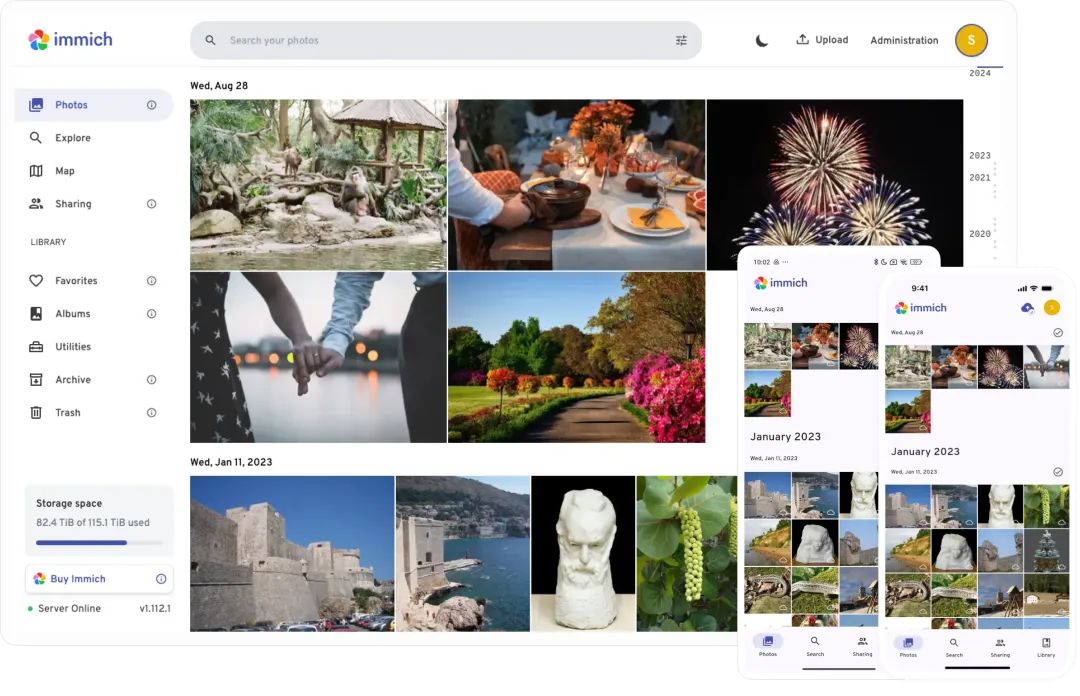

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

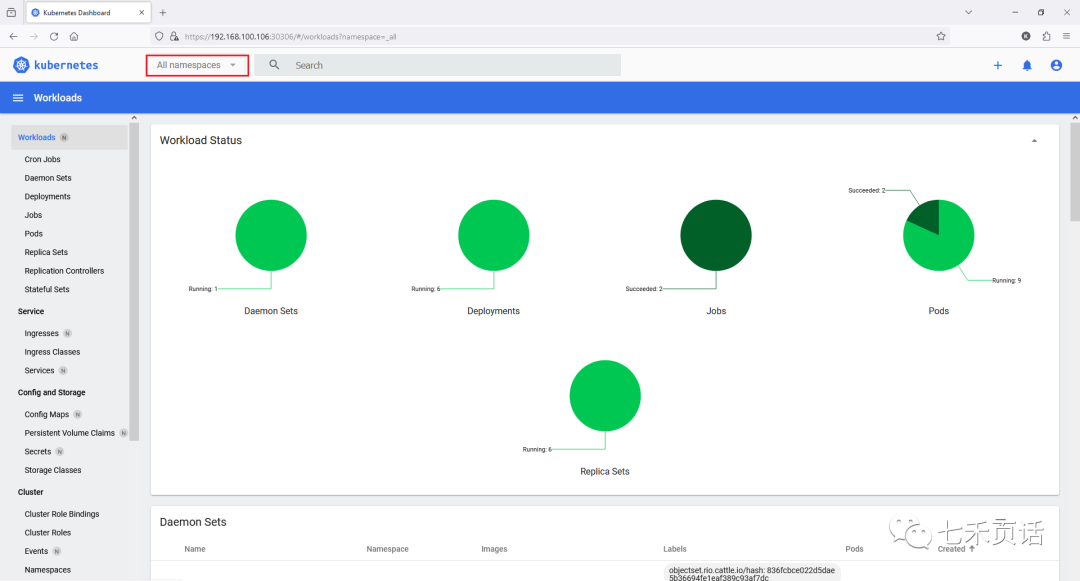

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

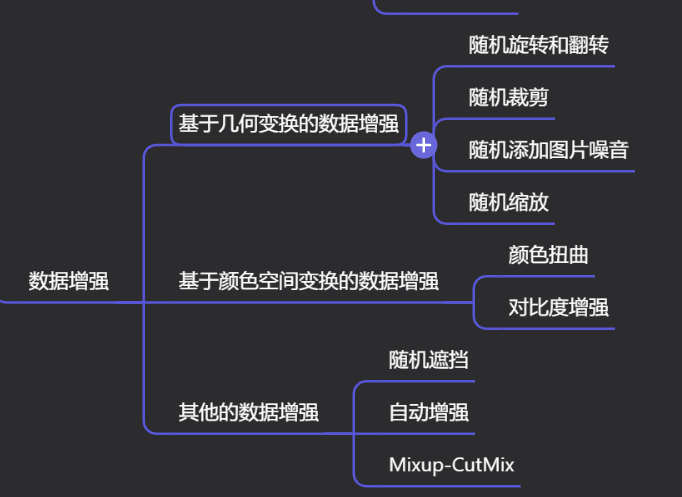

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

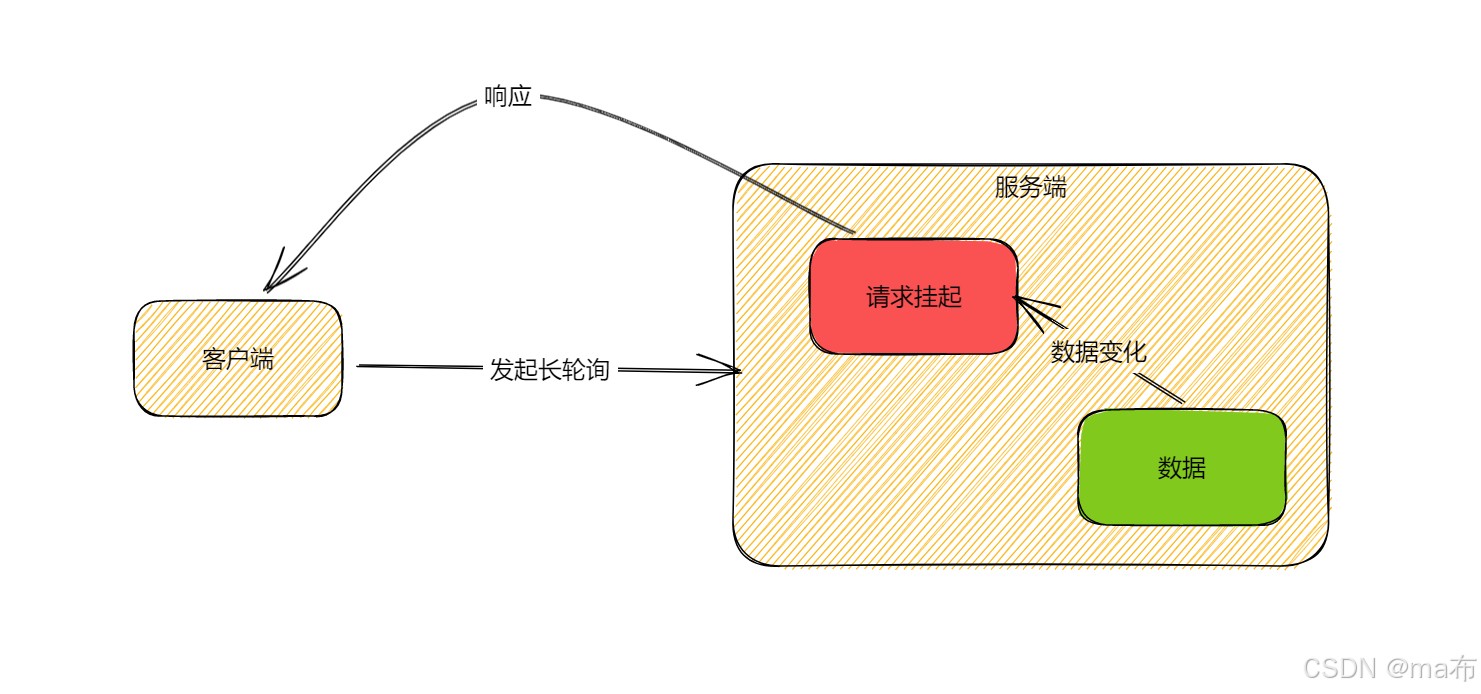

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

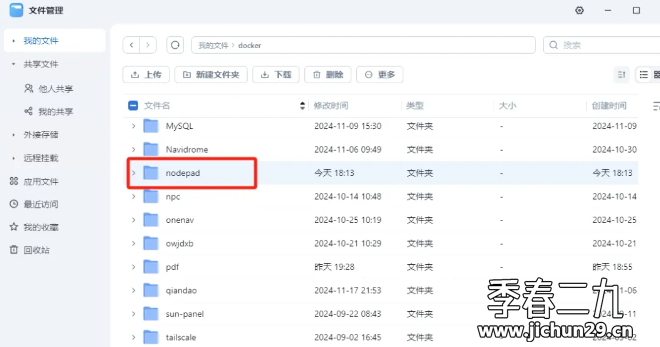

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

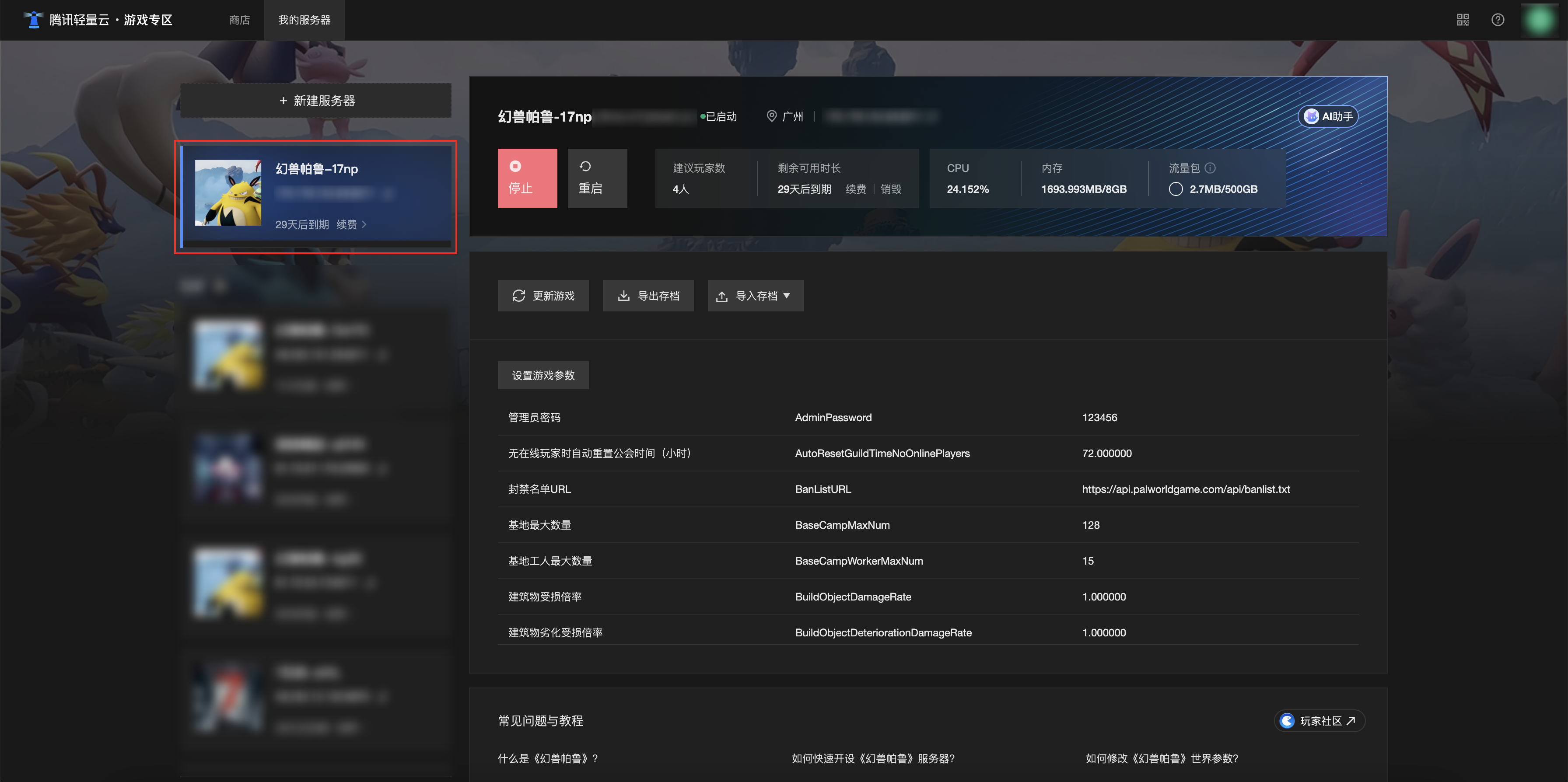

[Зона легкого облачного игрового сервера] Управление игровыми архивами