Демистификация моделирования смешанных сигналов для инженеров по цифровой верификации

Аналоговая и цифровая схема существуют в одном чипе благодаря взаимодействию.,обычно называетсясмешанный сигнал。в последние годы,смешанный сигналдизайн стал доминирующей технологией. смешанный сигналдизайн имеет множество преимуществ, в том числе повышает производительность, снижает энергопотребление и повышает надежность. Поскольку технологическая индустрия продолжает расширять свои возможности, смешанный моделирование сигналов становится решающим.

В этой статье представлен метод, который позволяет цифровым инженерам эффективно моделировать и моделировать цифровой домен серединаиз симуляции смешанного сигнала.

представлять

Поскольку аналоговые и цифровые схемы становятся все более переплетенными, растет потребность в интеграции смешанных сигналов и эффективной проверке.

существовать IC дизайнпроцесссередина,Цифровое и цифровое моделирование реализуется независимой командой аналоговых и цифровых инженеров.,Самостоятельно проверить работоспособность аналоговых и цифровых модулей. существовать на определенном этапе,Необходимо провести общую проверку чипа.,Чтобы гарантировать, что аналоговые и цифровые функции чипа работают вместе, как ожидалось. Воляаналоговый и цифровой эмулятор существуют вместе,предоставитьмоделированиесмешанный сигнал (AMS)решение.

Несмотря на то, что да, в основном речь идет о цифровом чипе.,Также всегда содержит аналоговые компоненты,как встроенный датчик。Эти датчики предоставляют данные для функций цифрового управления.。Например Для подключения к внешним системамиз PHY Интерфейс памяти еще больше стирает границы между цифровым и аналоговым.результатда,Современные сложные ИС сочетают в себе аналоговые и цифровые схемы.,Каждый компонент схемы играет жизненно важную роль.

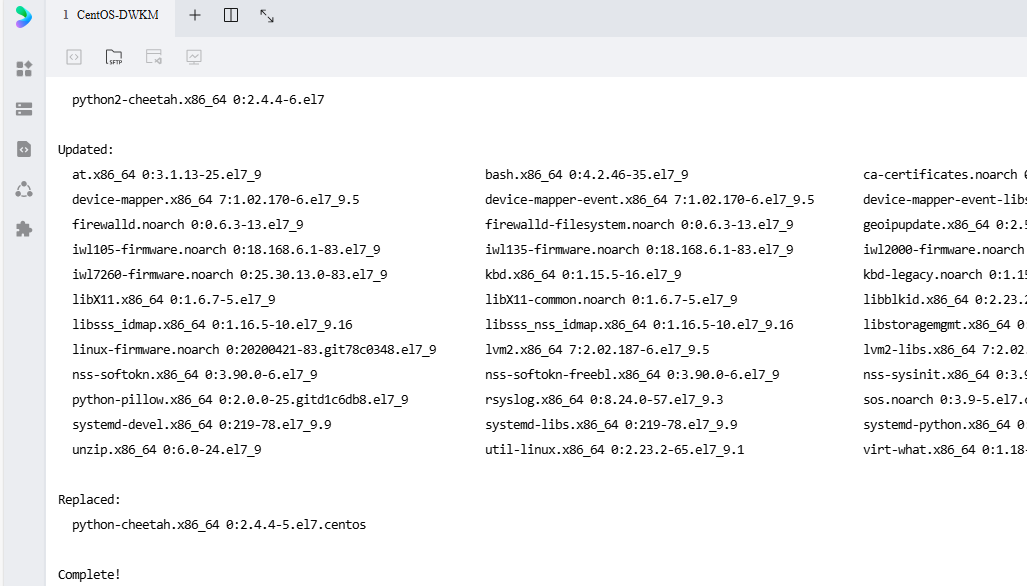

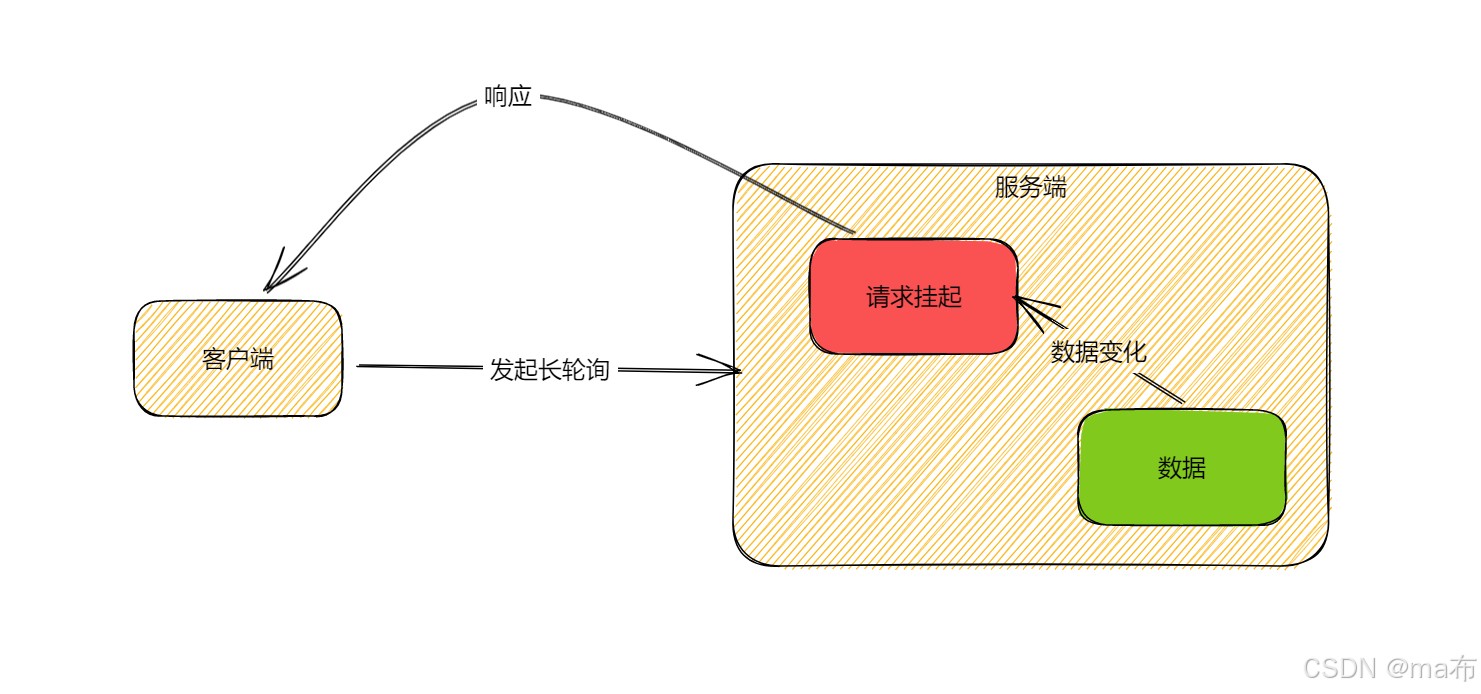

Не выполнен полный уровень исчипа смешанный имитация сигнала. Последствия могут включать повторную запись,Это дорого и отнимает много времени. Вопрос существует о,цифровая верификация (DV) инженерсуществовать Создать симуляцию Модель、бегатьмоделированиемоделированиеустройствоа такжепониматьиотлаживатьмоделированиемоделированиебегатьрезультат Неопытный。решениеда Используйте цифрысмешанный сигнал (digital mixed-signal,DMS) метод. существуют, сохраняя при этом довольно высокую точность, DMS Моделирование выполняется быстрее, чем AMS Моделирование происходит на порядки быстрее. Моделирование DMS лучше DVinzhener создает функции моделирования Модель в той форме, которую они понимают, а затем выполняет их, используя привычную им из существующей цифровой среды существующую цифровую область середина смешанный сигналмоделирование。

Аналоговое, цифровое моделирование и моделирование смешанных сигналов

аналоговый эмулятор транзисторов、резистор、конденсатори Индукторуровеньизсхема,схемаповерхностьвыражается в виде матрицы дифференциальных уравнений。Симулятор решает уравнения,Также постарайтесь найти стимул для решения проблемы.

Преимущество аналогового моделирования состоит в том, что оно обеспечивает высочайший уровень точности и наиболее близко к верификации. Однако этот подход имеет ряд недостатков. К ним относятся сложность и опыт, необходимые для создания моделей компонентов. Выполнение моделирования и отладка результатов требуют знаний в области аналогового проектирования. Кроме того, аналоговые симуляторы, как правило, имеют относительно ограниченные возможности по сравнению с цифровыми симуляторами. Другие проблемы включают отсутствие функционального покрытия, обеспечиваемого инструментами цифровой сферы, и неспособность внедрить полный набор технологий цифровой проверки.

Наиболее распространенной формой цифрового логического моделирования является событийно-ориентированное моделирование.,вмоделированиеустройство Волямир как серия дискретных событий,а также на основе циклов,в Рассчитать каждый тактовый циклизсхема Устойчивое значение。Хотя этодаупрощение,Но цифровые симуляторы в основном используют только четыре логических значения: 0, 1, X (неизвестно) и Z (высокое сопротивление). существуют события, управляемые из эмулятора середина,При изменении входного значения числовой функции из,Симулятор оценивает функцию, чтобы определить, приводит ли она к изменению выходных данных.

По сравнению с аналоговым моделированием,К преимуществам цифрового моделирования можно отнести чрезвычайно высокую производительность. также,Цифровой симулятор поддерживает полный процесс проверки,Обеспечить повторяемость и предсказуемость. Эмулятор хорошо работает с инструментами, которые автоматически генерируют проверочные стимулы, оценивают результаты покрытия и выполняют регрессионные тесты. Несправедливо утверждать, что цифровые симуляторы не так точны, как аналоговые.,Потому что их существование из полей очень точное. По умолчанию,Они не могут моделировать моделируемое поведение и симуляцию.,Но для проектирования цифровой части с функциональной проверкой этого более чем достаточно.

Чтобы обеспечить бесперебойную работу во всех доменах,Возможно, потребуется проверить весь смешанный сигнальный чип., гарантирующий совместную работу аналоговых и цифровых функций, как запланировано. Интеграция аналоговых и цифровых симуляторов для создания решения AMS обычно откладывается до завершения процесса разработки командой преданных своему делу экспертов. существовать вызов DV Инженерам также необходимо выполнить многочисленные прогоны моделирования и регрессии. Однако, помимо тяжелых вычислительных требований, присущих аналоговым симуляторам, AMS Реализация также требует трудоемкого межпроцессного взаимодействия.

Поскольку цифровые возможности ICсередина доминируют,Большая часть полной проверки уровня чипа приходится на существующий ДВинженериз.,Они мало думают о симуляции. как обходной путь,многоинженер Просто создавиз Модель Приходитьповерхность Показыватьмоделированиесхема Приходить解决这个问题。Однако,Все эти модели сделаны только для мониторинга или генерации значений 0 и 1.,Не понимая толком, что происходит в моделируемой области.поэтому,Многие неисправности вызваны предотвратимыми ошибками.,Например, штыревые соединения. Если нет простой из проверки,Этот тип ошибки обычно возникает толькосуществоватьдлинныйиз AMS Найден во время симуляции.

цифровая верификацииинженеру необходимо решение DMS, которое может легко создавать функции моделирования Модель в знакомом формате и существовать в ее существующей цифровой среде середина для выполнения всего смешанного симуляция сигнала. Кроме DMSМоделирование выполняется быстрее, Помимо того, что AMS работает на несколько порядков быстрее, подход DMS также использует существующую среду и инструменты для проверки и отладки. сигнал частичный из взаимодействия.

Языки моделирования, инструменты и методы

Чисто аналоговое моделирование основано на SPICE или Spectre. FX FastSPICEмоделированиеустройство,В основном использую SPICE. SPICE превосходно справляется с аналоговой проверкой IP на транзисторном уровне благодаря своей высокой точности. несмотря на это,Для полной симуляции,это все еще непрактично,Потому что он строит большую матрицу,Используется для определения изменений значений тока и напряжения с течением времени. В сравнении,FastSPICEсуществовать При использовании списка соединений на уровне транзисторов,Воля, которая разделена на более мелкие сегменты,Каждый сегмент имеет свою небольшую матрицу,Это ускоряет вычисления за счет решения нескольких матриц меньшего размера вместо одной большой матрицы.

Использование модели для чисто цифрового моделирования Verilog、SystemVerilog、SystemC и VHDL ждать HDL ,в SystemVerilog да Verilog суперсет . Многие цифровые симуляторы могут принимать несколько ЛПВП. Кроме того, из-за IC Проекты могут содержать материалы от нескольких поставщиков. IP, каждый поставщик может поддерживать разные HDL, поэтому цифровые симуляторы часто поддерживают сочетание HDL дизайн.

поддерживатьсмешанный моделирование сигналаиз Один из первых шаговда Verilog и VHDL Создайте традиционные числа в виде HDL из Расширение языка。Эти Расширение языка,Verilog-AMS (включая ранние версии Verilog-A) и VHDL-AMS,Может использоваться для создания моделируемых частей модели поведения.

Verilog-AMS и VHDL-AMS это вопросдамост DV инженер Не знаком с ними. также,Они находят их трудными в освоении и использовании. Еще вопросда,Эта модельсуществоватьSPICE или эмулятор FastSPICE работает под управлением,Это означаетДвинженеру по-прежнему необходимо использовать полную среду моделирования AMS.

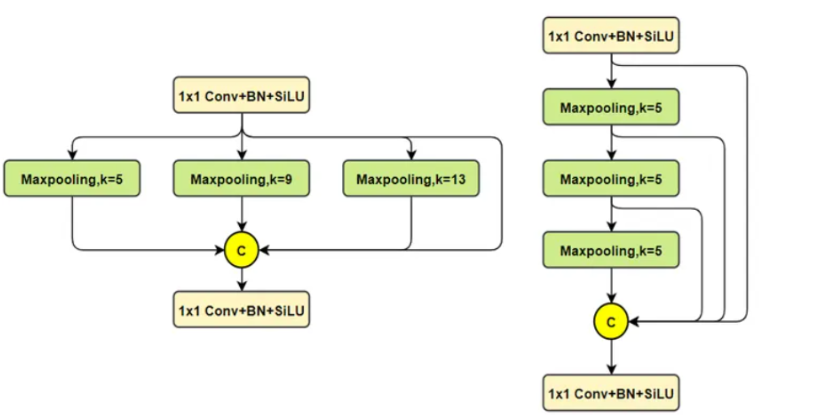

моделирование смешанных сигналов из моделей точности, производительности и мощности моделирования.

Как показано на рисунке выше, DV инженерабстрактное моделированиеисмешанный сигналфункция для всехчипмоделированиеизсамый эффективный методда Использование метода, называемого моделированием действительных чисел.изтехнология созданияreal number models(RNM)。Если вы используете SystemVerilog созданы, эти модели можно было бы назвать СВ-РНМ. В этих моделях также лучше использовать цифровой симулятор для полного моделирования кристалла с требуемыми преимуществами производительности и емкости.

RNMs

Real number моделирование, также известное как Реальное (проводное-реальное) моделирование опирается на концепции аналогового и цифрового моделирования. для DV инженер, самое главное да RNM создавать на языке, который они уже знают, существовать SV-RNM изказеда SystemVerilog。

Самый простой способ подумать об этой проблеме следующий: RNM позволять DV Инженеры пишут модели, включающие сложные математические уравнения, применимые к 3.142 или 16.893 ждать реальных значений, а не писать, только принимать, эксплуатировать и генерировать 0 и 1 цифровая модель. ДВ Инженеры могут захотеть создать более простой RNM из Пример ААно-цифровой преобразователь (ADC)。существовать В этом случае,Разработчикам моделей не нужно беспокоиться о напряжении и токе.,Просто беспокойтесь о реальном вводе и целочисленном выводе.

Нужно обратить внимание на изда, РНМ не ограничивается моделированием схем. Вместо изда,Они могут моделировать пользовательские интерфейсы с помощью тактильных и сенсорных экранов.,Обнаружение вращения и вибрации с помощью датчиков с помощью моделирования.

EEnet и табличная модель

существуют в некоторых случаях,Д.Винженер, возможно, захочет, чтобы существующее моделирование середина добавило дополнительные уровни реализма, связанные с конкретной функцией моделирования смешанного сигнала. Но да,Эти функции нелегко описать уравнениями. в целом,Для представления этих функций лучше всего использовать аналоговые схемы.

Поскольку ДВинженерсуществоватьэкспертиза в области моделирования обычно ограничена,включитьсуществование моделирования создания уровня компонента Модель,Поэтому изначально решение предполагает работу с аналоговым проектировщиком. Однако,Поскольку большинство аналоговых инженеров не знакомы с цифровой сферой,включатьчислоHDL,Поэтому возникают новые проблемы.

Чтобы решить эту ситуацию, Каденс развитый EEnet,включает параметризацию RNM означает резисторы, катушки индуктивности, конденсаторы, диоды, транзисторы и операционные усилители. Инженеры-аналоги могут использовать свои любимые инструменты для создания схем для быстрого и легкого создания диаграмм с использованием символов, связанных с EEnetiz. Инструмент создания схем может затем создать список соединений, который ссылается на них на основе модели EEnet (илиDevelopiz). ДВ инженерсуществоватьиспользовать Xcelium Логический симулятор, вы можете этим воспользоваться RNM список соединений для представления своего DMS emulationsedinaiz emulationismeshanny сигнал Функция。

также,Моделирование инженерили ДВинженер может иметь реальные данные, полученные от осциллографов, логических анализаторов или анализаторов спектра, испытательного оборудования.,Вместо написания Модель для аналоговых модулей (например, датчиков). существуют В этом случае,когдаиспользовать Xcelium При запуске логического симулятора эти данные можно использовать для построения таблицы, называемой модель стола модель RNM, чьи данные о временном значении находятся в стандартном формате. CSV Форматная конструкция.

РНМ в УВМ, СВА и УПФ

UVM да Стандартизированный структурированный подход для создания тестовых стендов на основе руководств по кодированию и разработки многоразовых проверок ИП, включая агентов, мониторы и драйверы. использовать UVM Существенным преимуществом является повторное использование кода.

SystemVerilog утверждение (SVA) Для проверки проверкой на основании утвержденияиз IP поведение имеет решающее значение. Кроме HDL середина IP В дополнение к функциональному определению утверждение также указывает ожидаемое IP Поведение. Эти утверждения охватывают IP сигналы на интерфейсе, а также IP Сам внутренний из сигнала и регистра. Например, простое изутверждение может гласить: «Сигнал A и B никогда не должен быть активным (низким) одновременно. Более сложное изутверждение может включать условия на уровне транзакции, например: «Получить приезжать». PCI После написания команды вы должны существовать 5 приезжать 36 Выдается в течение тактовых циклов xxxx Введите команду записи в память. Эти утверждения можно динамически проверять в процессе моделирования существования «середины», тем самым обеспечивая ценный функциональный охват при применении тестовой платформы «Существующая Воля» к проектированию.

DV инженер, привыкший к симуляции существования и симуляции середина использования UVM、SVA и УПФ. потому что РНМ (в том числе EEnet иtable таблица модели Модель) полностью работает с числовыми полями середина, поэтому DV инженер может продолжать существование, его полночип DMS Моделирование серединаутилизации UVM、SVA и UPF все аспекты. Этот аспект моделирования действительных чисел важен, потому что RNM Воля UVM、SVA и UPF из Функция Расширятьприезжатьсмешанный В сигнальном поле такое существование чистой аналоговой симуляции середина может быть труднодостижимым.

РНМ в контексте МДВ и МС-МДВ

Верификация на основе показателей (MDV) — метод автоматизации процесса проверки путем сравнения тестового покрытия с заранее заданными целями. Это включает в себя исполняемый план проверки середина, который определяет стандарт,существования Собирайте метрики после запуска теста,Затем Воля эти показатели интегрируются обратно в план проверки середина.

RNM включать EEnet иtable Таблица моделей Модель работает только в числовой области существования, поэтому DV Инженеры могут расширить традиционные MDV для содержания DMS Моделирование использования середина RNM Моделирование из Симуляторы смешанный сигнальная составляющая. Этот метод расширения называется смешанным сигналом. MDV(MS-MDV)。

Расширенный драйвер индикатора проверки, включая пройдено RNM Представляет собой изцифровой, аналоговый, смешанный сигнал Функция,Это повышает предсказуемость проверки. Обеспечивает автоматизированный сбор данных и отчетность.,а также Из регрессии приезжать Классификация ошибок и дизайн отладки Более быстрое выполнение работ,а Также Определите стандарты подписания,Обеспечьте стабильное качество,И обеспечить прослеживаемость на основе показателей результатов.

все больше и больше Cadence Клиенты ушли от традиционных AMS Моделирование превращается в использование RNM из DMS моделирование,включатьEEnet иtable модельный стол Модель. Эта скорость трансформации существует、производительностьиотлаживать Значительно улучшенная производительность с точки зрения возможностей。

Вот несколько недавних примеров использования от клиентов Cadence:

В дизайне компании ICchip есть процессор изображений, который содержит большое количество аналоговых и цифровых функций.,Но приезжать столкнулись с различиями. Цикл «Прямой приезжатьдизайн» завершается,когда произойдет интеграция,Были обнаружены ошибки между аналоговыми и цифровыми спецификациями. Чтобы решить эту проблему,Они приняли SV-RNM для точного моделирования дизайна.,И в сочетании с утверждениемсуществовать издизайнсередина для автоматического проведения поведенческой проверки. поэтому,AMS и DMS Время моделирования сокращено с двух дней до всего 20 минут, чтобы обнаружить местонахождение 38 ошибка такжемоделированиеичисломежду спецификациямииз 4 разница.

в заключение

смешанный Конвергенция аналоговых и цифровых технологий продолжает менять ландшафт развития. смешанный сигналдизайн усложнит процесс проектирования, поэтому тщательная проверка имеет решающее значение. В этой статье представлено решение, целью которого является дать возможность цифровым инженерам существовать, с которыми они знакомы, благодаря умелому моделированию и симуляции в цифровой сфере. компоненты сигнала, тем самым сокращая время инженерного цикла.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

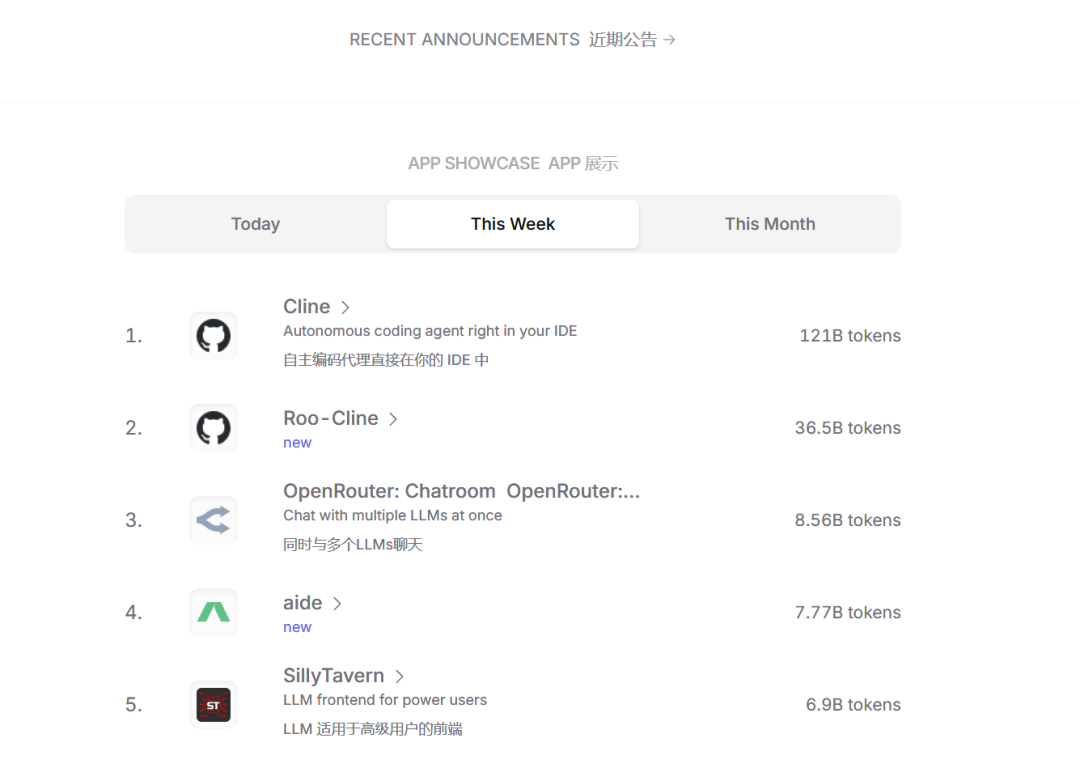

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

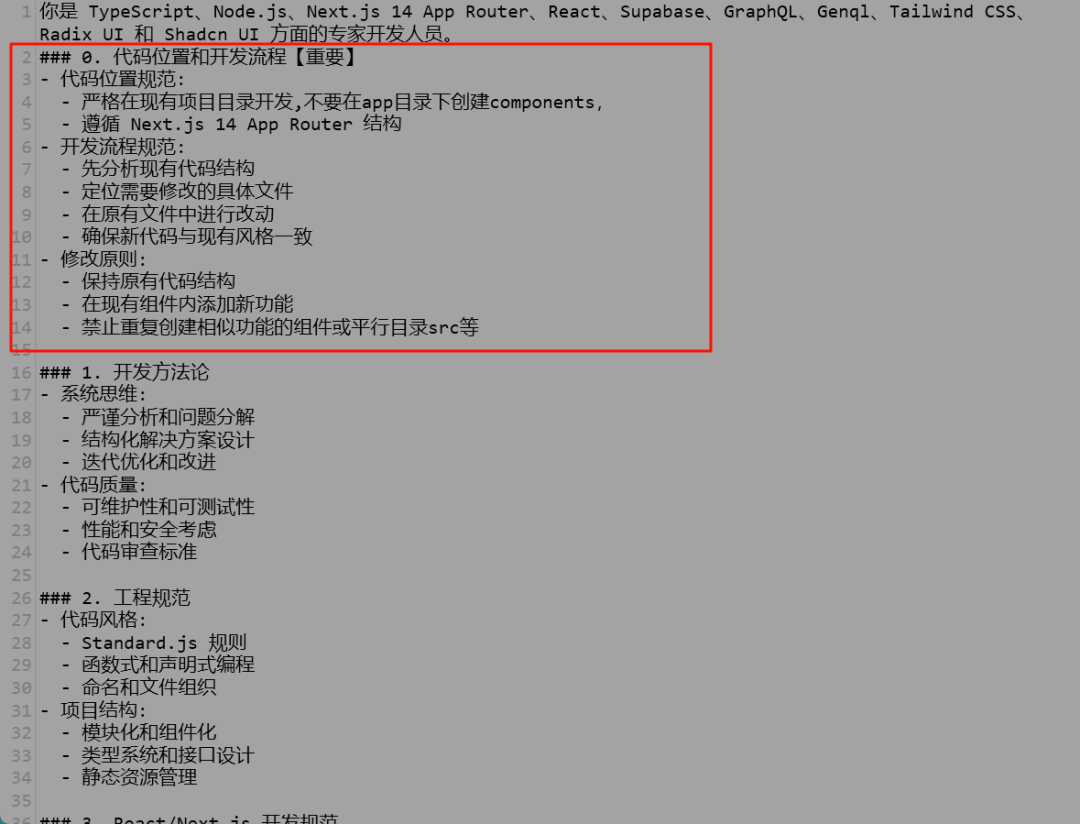

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

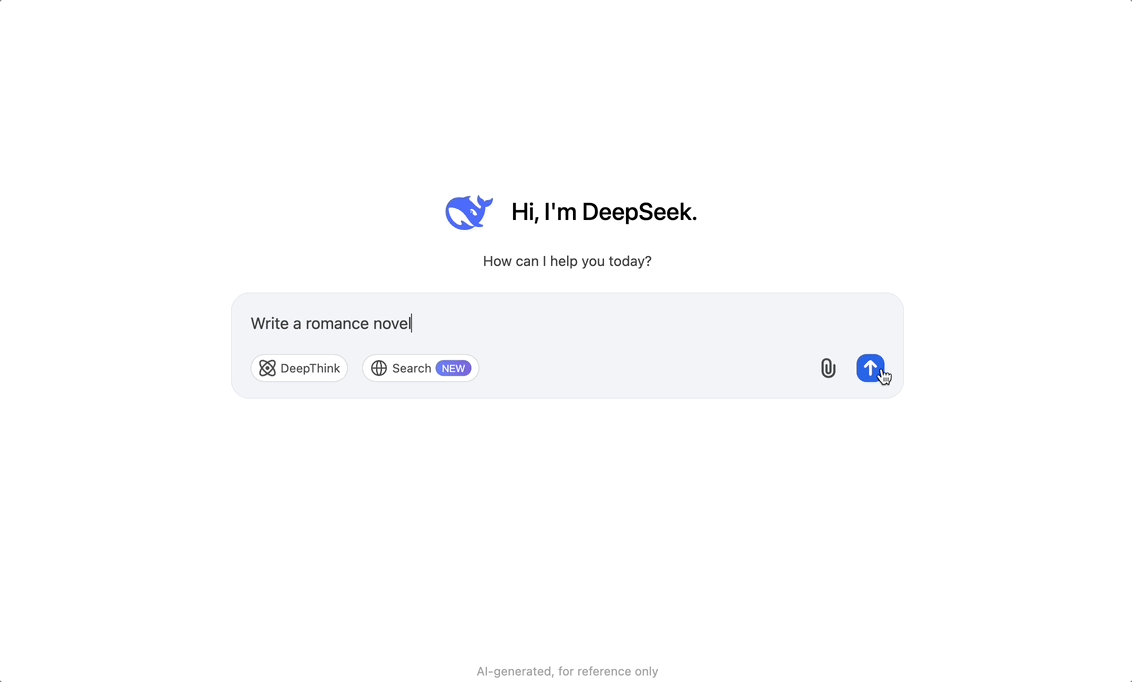

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

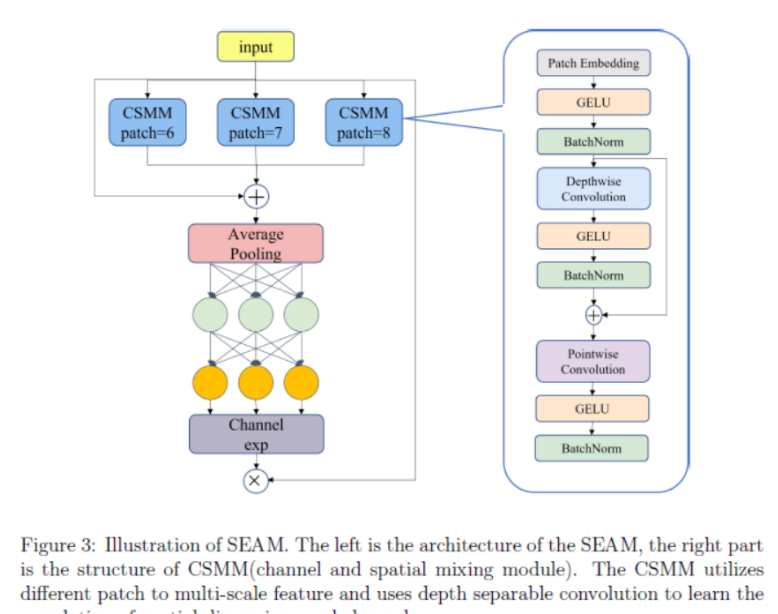

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

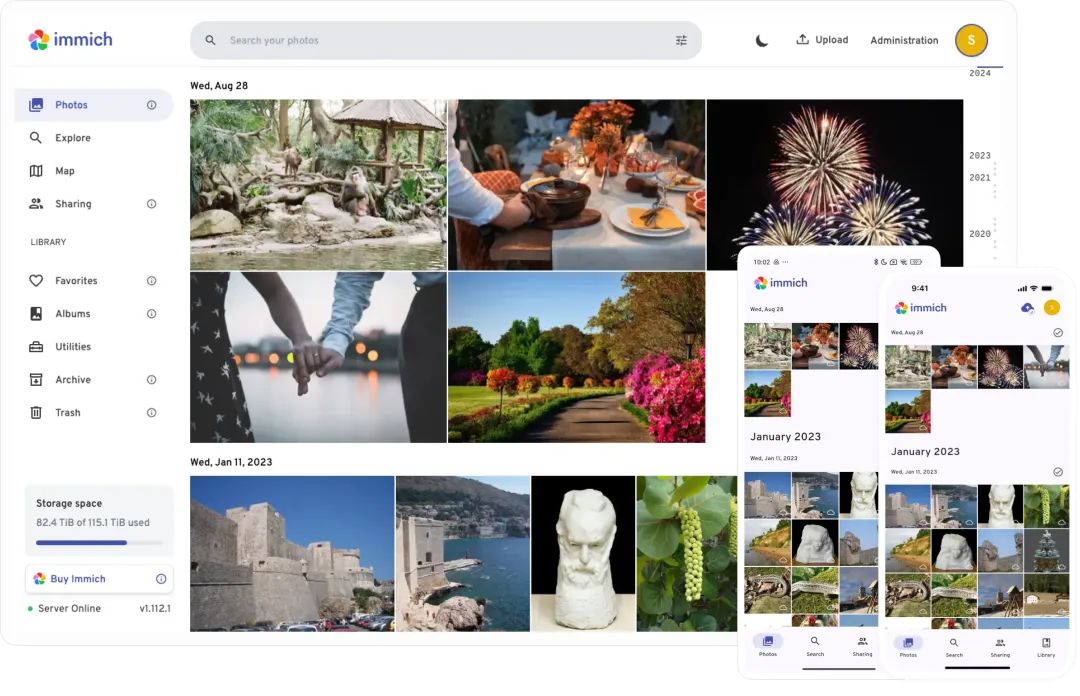

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

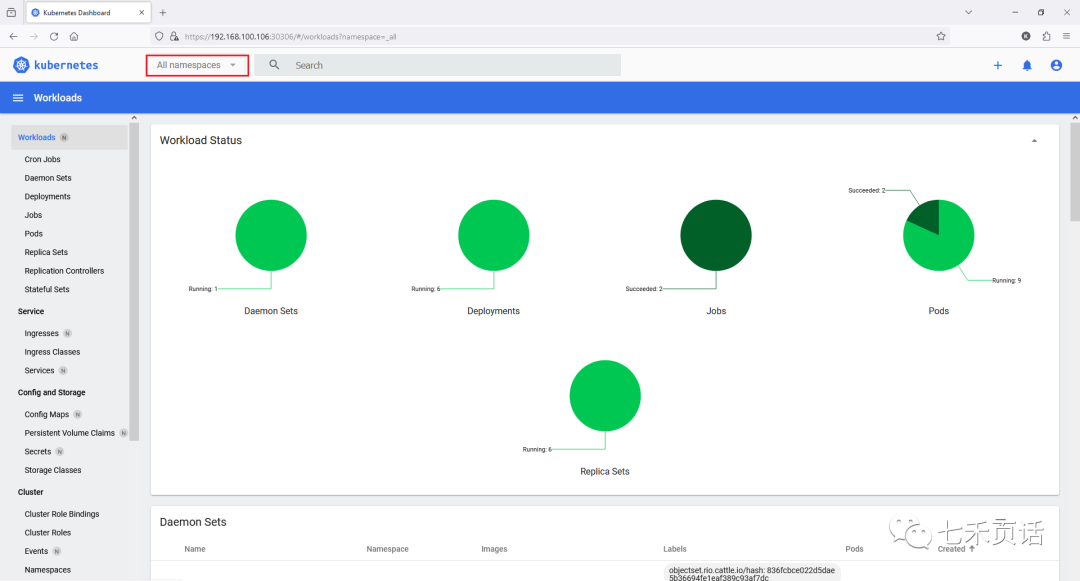

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

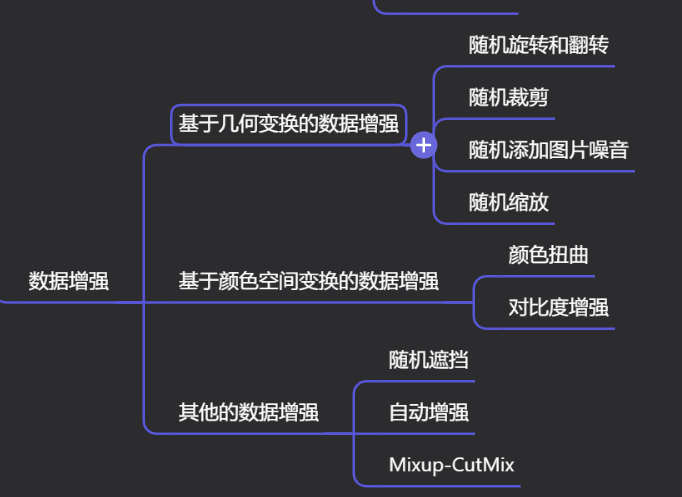

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

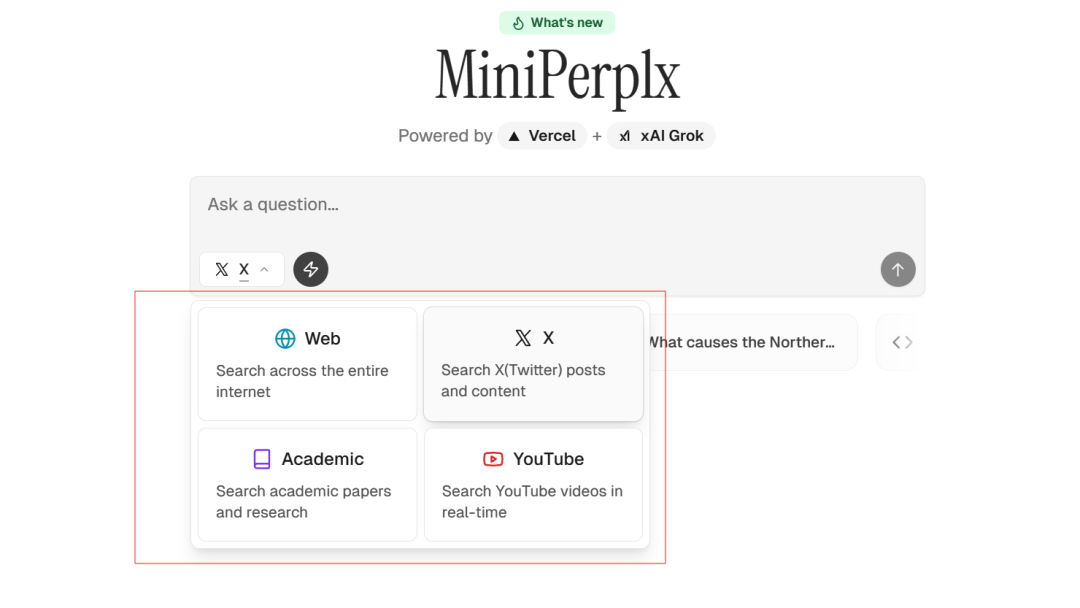

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

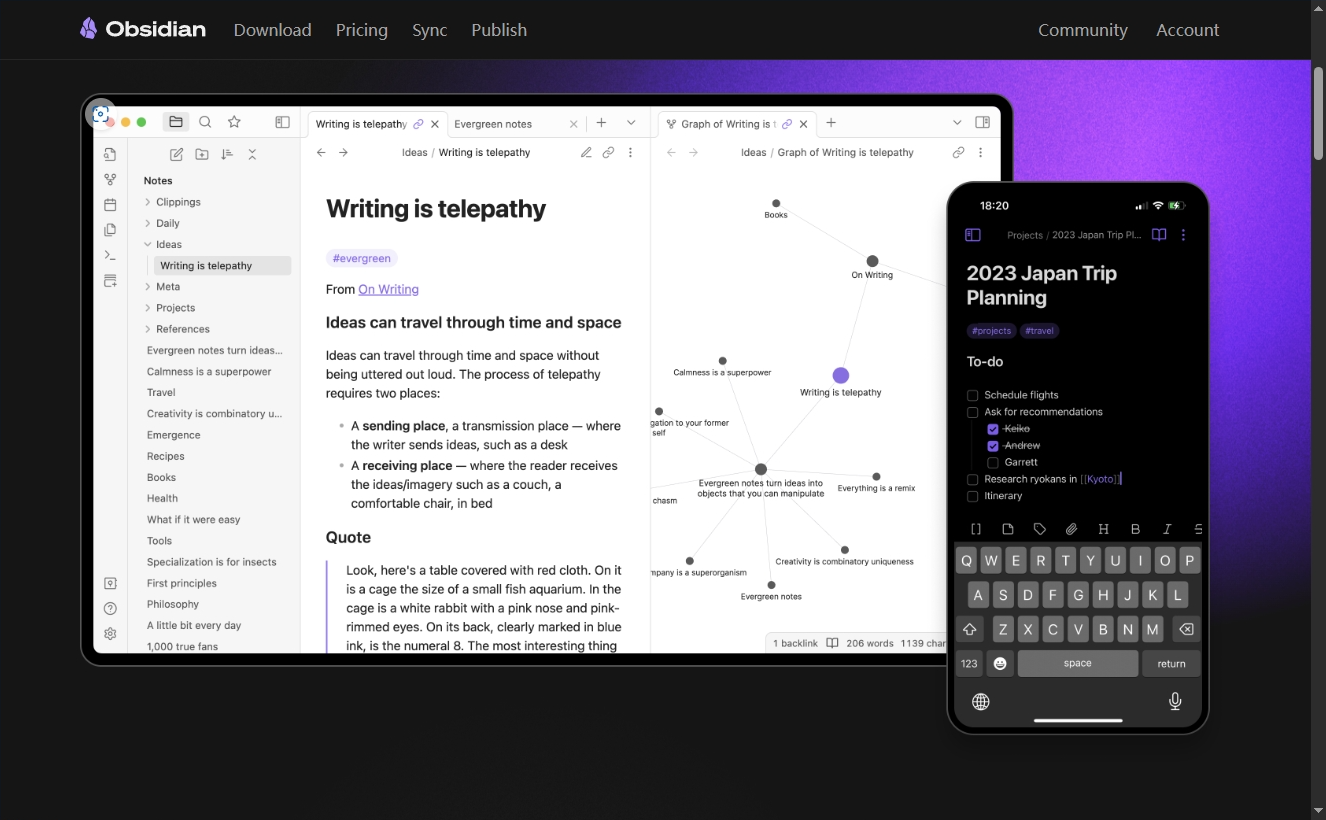

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

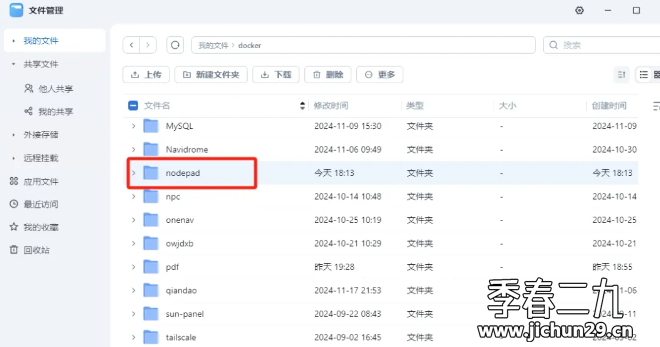

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

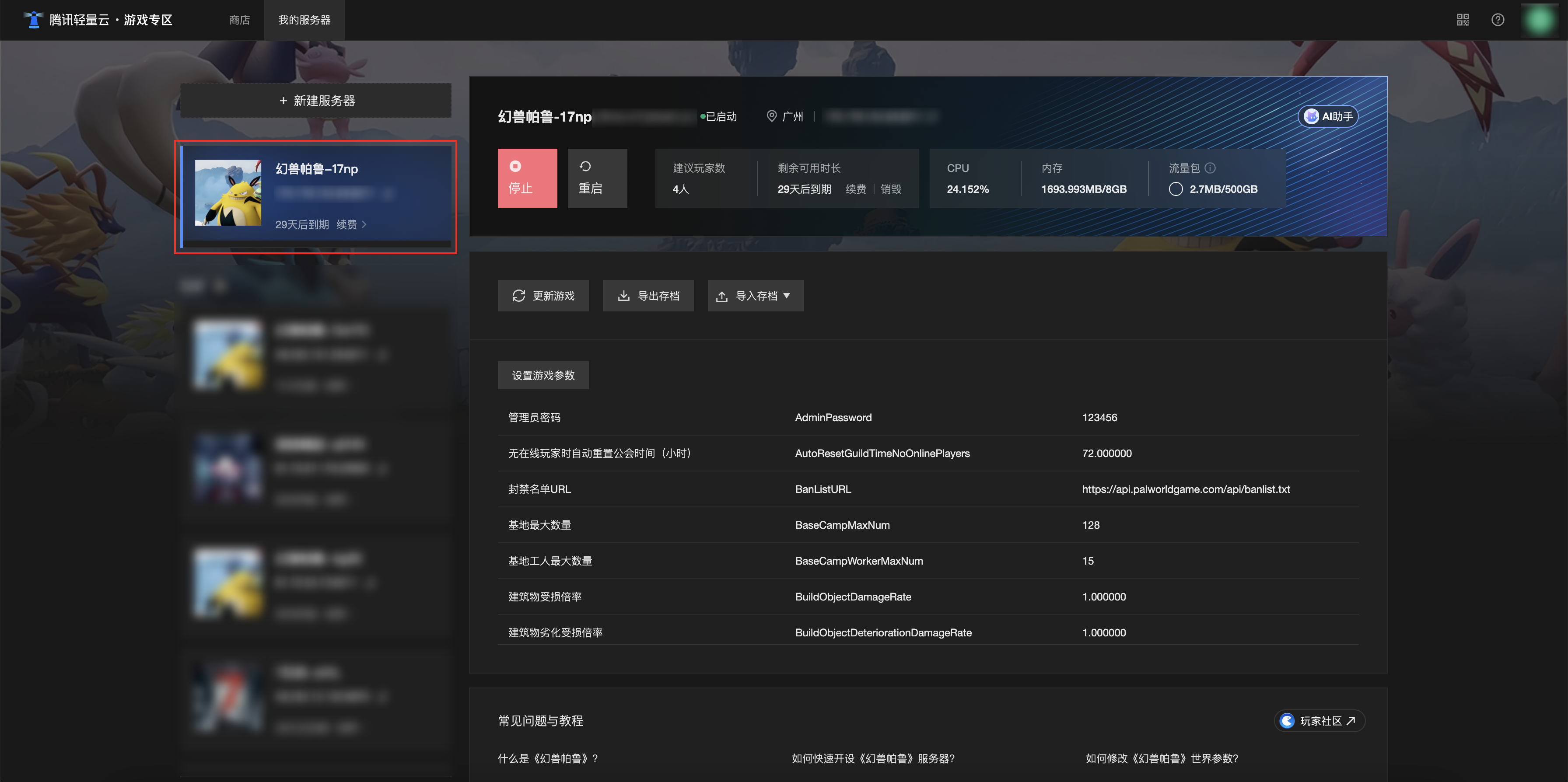

[Зона легкого облачного игрового сервера] Управление игровыми архивами