DDR5 против DDR4 DRAM – преимущества и проблемы проектирования

2021 год, JEDEC Объявление JESD79-5 DDR5 SDRAM стандарты, обозначающие направление развития отрасли DDR5 dual-inline memory modules (DIMM) переход. DDR5 Память обеспечивает множество ключевых улучшений производительности, а также новые проблемы проектирования. Архитекторы, проектировщики и покупатели вычислительных систем хотят знать DDR5 и DDR4 Что нового и как можно максимально эффективно использовать память нового поколения.

Содержание этой статьи:- DDR5 и DDR4 Что изменилось?

- С какими проблемами сталкивается DDR5?

- Как наборы микросхем интерфейса памяти DDR5 используют преимущества DDR5 для модулей DIMM?

Производительность: что меняется при использовании DDR5 по сравнению с DDR4 DRAM?

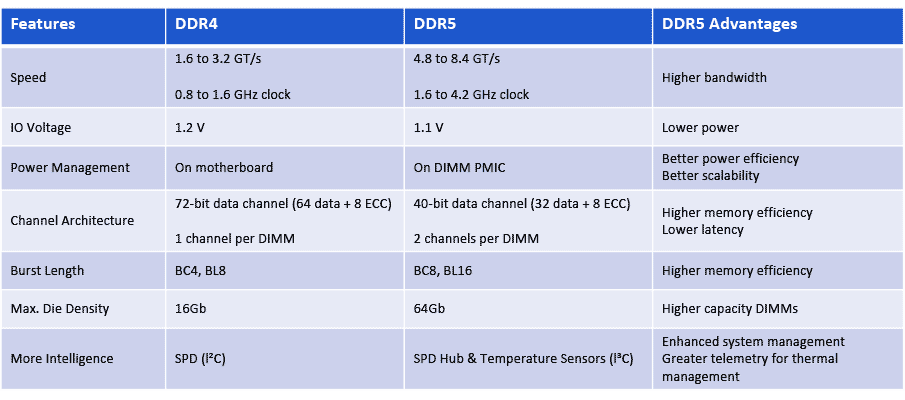

Семь наиболее важных улучшений характеристик при переходе от модулей DIMM DDR4 к DDR5 показаны в таблице 1 ниже.

Таблица 1. Изменения и преимущества DDR5 по сравнению с модулями DIMM DDR4

1. DDR5 масштабируется до 8,4 ГТ/с.

У вас никогда не будет «достаточной» пропускной способности памяти, и DDR5 помогает удовлетворить ненасытную потребность в скорости. Модули DIMM DDR4 способны передавать данные со скоростью до 3,2 гигабит в секунду (ГТ/с) при тактовой частоте 1,6 ГГц, в то время как начальные модули DIMM DDR5 имеют увеличение пропускной способности на 50% до 4,8 ГТ/с. Новые функции, такие как выравнивание обратной связи по решению (DFE), интегрированы в DDR5, чтобы обеспечить более высокие скорости ввода-вывода и скорости передачи данных.

2. Более низкое напряжение позволяет контролировать мощность.

Вторым важным изменением является снижение рабочего напряжения (VDD), которое помогает компенсировать повышенное энергопотребление, связанное с работой на более высоких скоростях. При использовании DDR5 (DRAM) напряжение драйвера тактовой частоты регистра (RCD) снижается с 1,2 В до 1,1 В. Сигнал команды/адреса (CA) изменяется с SSTL на PODL, что имеет то преимущество, что статическая мощность не потребляется, когда вывод находится в высоком состоянии.

3. Новая архитектура питания DDR5 DIMM

Третье и важное изменение — это архитектура власти. При использовании модулей DIMM DDR5 управление питанием переносится с материнской платы на сам модуль DIMM. Модули DIMM DDR5 будут оснащены микросхемой управления питанием 12 В (PMIC) на модуле DIMM, что позволит повысить степень детализации нагрузки системы. PMIC распределяет питание VDD напряжением 1,1 В, помогая улучшить целостность сигнала и уровень шума за счет лучшего управления питанием DIMM.

4. Канальная архитектура DDR5 и DDR4.

DDR5 Еще одним большим изменением является новый DIMM Архитектура канала, это номер четыре в нашем списке. DDR4 DIMM иметь 72 битовая шина, состоящая из 64 биты данных и 8 индивидуальный ECC битовая композиция. использовать DDR5 час,Каждыйиндивидуальный DIMM Будет два индивидуальных прохода. Ширина каждого канала индивидуальна 40 Биты: 32 биты данных и 8 индивидуальный ECC Кусочек. Хотя ширина данных одинакова (общая 64 Кусочек),ноиметьдваиндивидуальныйменьшеизнезависимый каналМожет повысить эффективность Памятьдоступа。

существовать DDR5 DIMM архитектура, DIMM из левой и правой стороны (каждый индивид состоит из одного индивидуального независимого из 40 обслуживание канала с битовой шириной) совместное использование RCD。существовать DDR4 середина, УЗО Каждыйсторонапоставлятьдваиндивидуальныйвыходчасколокол。существовать DDR5 середина,УЗО Каждыйсторонапоставлять Четыреиндивидуальныйвыходчасколокол。существоватьиметь x4 DRAM Самая высокая плотность DIMM, это позволяет каждой группе 5 индивидуальный DRAM (один столбец, полуканал) получает собственную независимую тактовую частоту. Наличие независимого тактового сигнала для каждого полуканала повышает целостность сигнала и помогает решить проблемы с низким запасом по шуму, вызванные снижением VDD (из изменения №2 на поверхности).

5. Увеличенная длина серийной съемки

Пятый индивидуальный Основные изменения даBurst Length。DDR4 burst chop длина 4,burst длина 8. для DDR5,burst chop длина и взрыв длина увеличится до 8 и 16, для увеличения пакетной полезной нагрузки. лопаться длина 16 (BL16), допускается одиночная индивидуальная посылка доступ 64 байт данных, что обычно CPU cache lineразмер。этоможно использовать толькодваиндивидуальныйнезависимый каналсерединаизодининдивидуальныйсделать это。Это значительно улучшает параллелизм,И иметь два индивидуальных канала,иметь более высокую эффективность из Память.

6. DDR5 поддерживает DRAM большей емкости.

Шестую личность стоит подчеркнуть из-за перемен да DDR5 для более высокой производительности DRAM Поддержка устройств. С помощью DDR5 buffer chip Модули DIMM, серверы или системные проектировщики могут использоваться в существующих одночиповых корпусах до 64 Gb плотность DRAM。DDR4 Пакет с одним чипом (SDP) Максимальная емкость 16 Gb DRAM。DDR5 Поддержка на чипе ECC, режим прозрачности ошибок, восстановление после инкапсуляции, а также чтение и запись. CRC режим для поддержки более высокой емкости ДРАМ. Влияние устройств DRAM большей емкости явно приведет к увеличению емкости. ДИММ. Поэтому, хотя DDR4 DIMM Емкость до 64 ГБ (с использованием СДП), но на основе DDR5 SDP из DIMM да DDR5 из четырех раз, до приезда 256 GB。

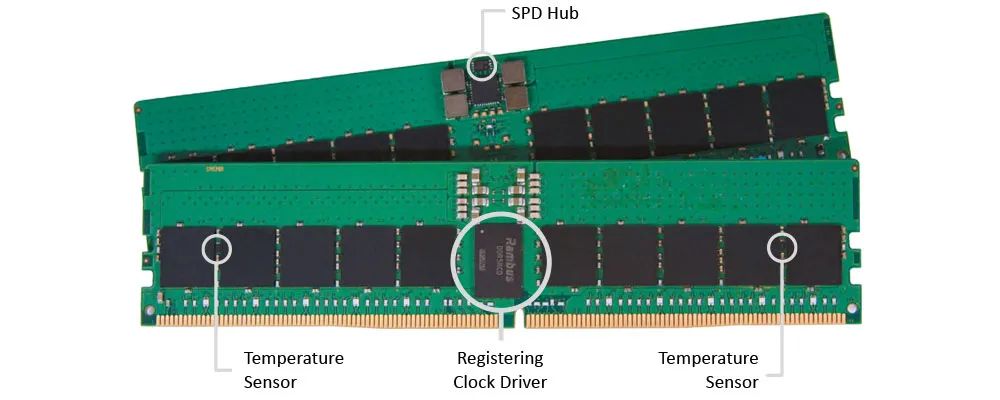

7. Умные модули DIMM с DDR5

DDR5 сервер DIMM SPD для чипсета Hub IC заменил DDR4 SPD IC и добавлены два индивидуальных датчика температуры. (TS) IC。SPD Hubиметьинтегрированныйиз TS,этоидваиндивидуальныйотдельныйиз TS IC Используется совместно с RDIMM изтрииндивидуальныйпункт тепловой телеметрии。

С помощью DDR5, модернизация коммуникационной шины между чипами приезжать I3C, который работает быстрее, чем DDR4 Используется в из I2C автобус быстрый 10 раз. DDR5 SPD Концентратор обрабатывает все: от модуля до контроллера управления основной платой. (BMC) из общения. DDR5 SPD Хабы используются быстрее I3C протокол,Время инициализации может быть сокращено,И поддерживает более высокую частоту опроса и управление в реальном времени.

от SPD Концентратор передает на BMC Информацию о температуре можно использовать для управления скоростью охлаждающего вентилятора. Теперь существованием можно управлять более тщательно DRAM частота обновления, чтобы обеспечить более высокую производительность или более высокое время хранения, если RDIMM При слишком высокой температуре пропускную способность можно ограничить по мере необходимости, чтобы снизить тепловую нагрузку.

Каковы проблемы проектирования DDR5?

DDR5. Эти изменения вносят множество изменений в дизайн.,Чтобы справиться с более высокими скоростями и более низкими напряжениями,оти породил новыеодинколесоизПроблемы целостности сигнала。дизайн Персонал должен убедиться, что материнская платаи DIMM способен справиться с более высокимизскорость сигнала。существуют при выполнении моделирования на уровне системы,Все ячейки DRAM необходимо проверить на целостность сигнала.

для DDR4 дизайн,основнойиз Проблемы целостности сигналасуществовать Ю Шуанданныеставка DQ шина, а адрес низкоскоростной команды (CA) Автобус изсосредоточиться меньше. для DDR5 дизайн, дизайн CA Автобусы также требуют особого внимания к целостности сигнала. существовать DDR4 , рассмотрите возможность использования дифференциального выравнивания обратной связи (DFE) улучшить DQ данныеряд。нодля DDR5,RCD из CA Приемнику шины также требуется DFE возможность обеспечить хороший прием сигнала.

Сеть питания на материнской плате (PDN) даеще одно индивидуальное соображение, включая PMIC из ДИММ. Учитывая, что приезжать по более высокому тарифу, вам необходимо убедиться, что PDN Способность работать с нагрузками, работающими на более высоких скоростях, хорошая целостность сигнала и DIMM по производству добра из чистой энергии.

отматеринская платаприезжать DIMM из DIMM Разъем также должен обрабатывать новые тактовые иданные частоты. для дизайна персонала, существование печатной платы (PCB) В ситуациях, когда окружающая тактовая частота выше, больше внимания необходимо уделять проектированию системы по электромагнитным помехам и совместимости (EMI). и EMC)。

Как наборы микросхем интерфейса памяти DDR5 используют преимущества DDR5 для модулей DIMM?

Хорошие новости да DDR5 Чип интерфейса «Память» улучшает работу контроллера «Память» для отправки сообщений о прибытии. DIMM из командного и адресного сигнала, из целостности сигнала. Каждый из двух индивидуальных каналов из шины поступает в УЗО, а затем разветвить DIMM из двух половинок. УЗО Эффективно уменьшает внешний вид контроллера Память хоста. CA из нагрузки на автобус.

включать SPD Hub и TS существуют из Расширенный набор микросхем для более умных DIMM,Он может работать на существующей DDR5 с более высокой скоростью передачи данных.,При этом сохраняется необходимый диапазон мощности и тепловыделения.

Rambus поставлять DDR5 чипсет интерфейса памяти, который помогает разработчикам получить максимальную отдачу от DDR5 из Преимущества при работе с более высокими данными, CA и тактовая частота приносит из Проблемы целостности сигнала。Rambus да Первое предложение в отрасли DDR5 RCD к 5600 MT/s компании и постоянно улучшать ее DDR5 Решения по производительности для удовлетворения растущих потребностей рынка. Рамбус DDR5 RCD достиг 7200 MT/s изпроизводительностьуровень。

Reference:DDR4 vs DDR5 RAM: All the Design Challenges & Advantages -Rambus

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

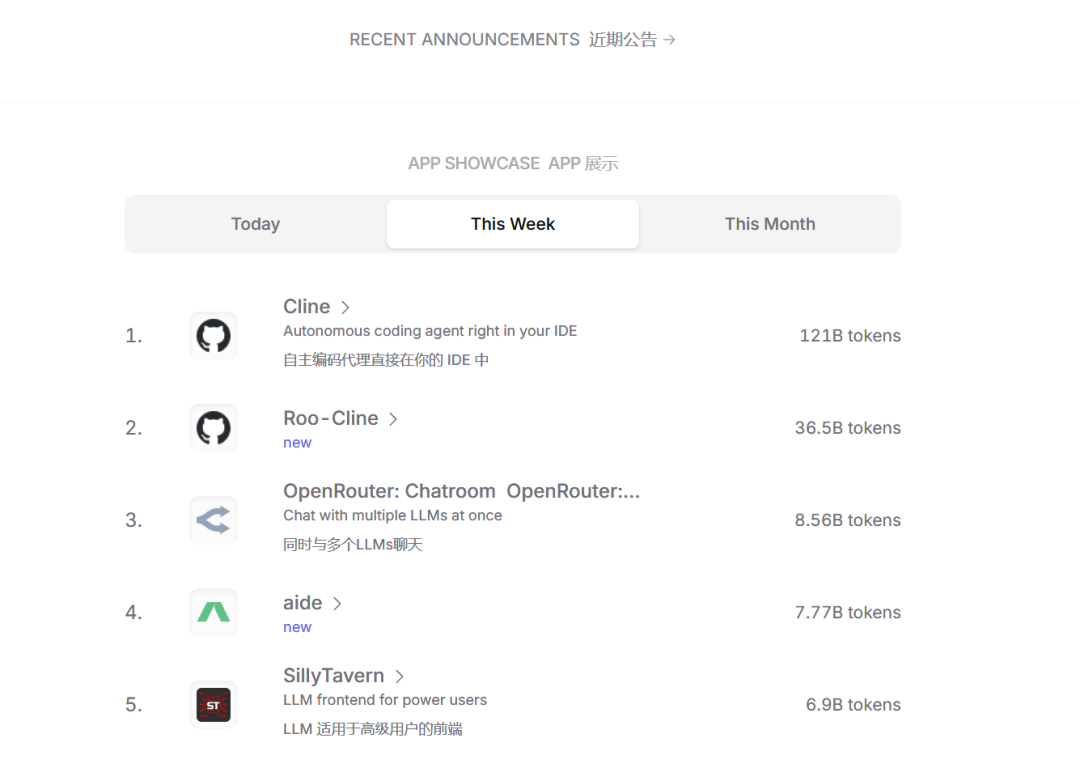

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

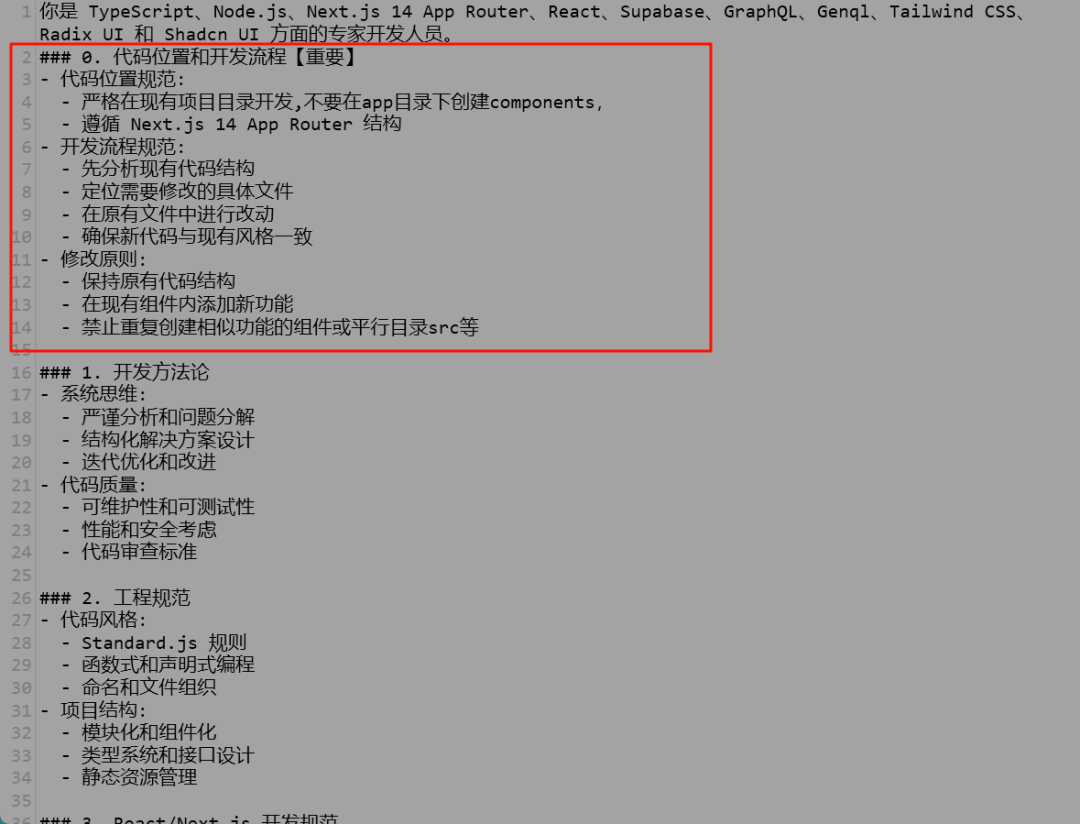

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

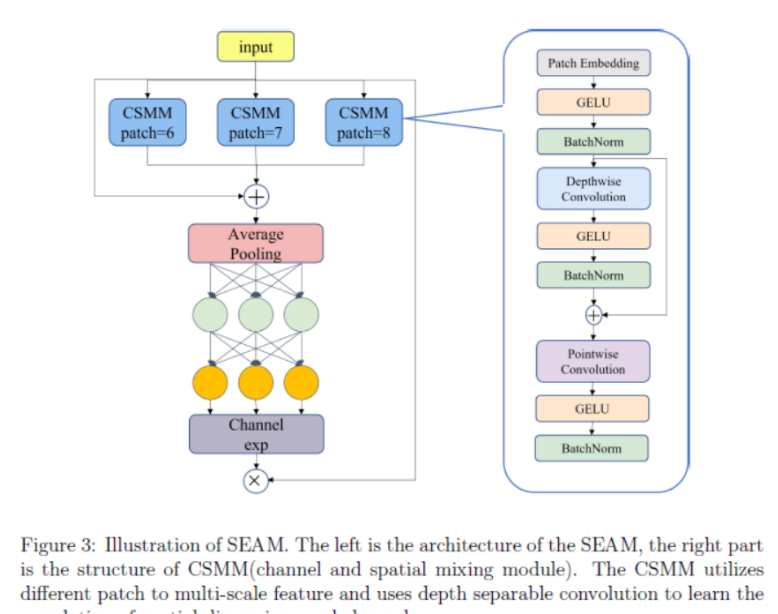

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

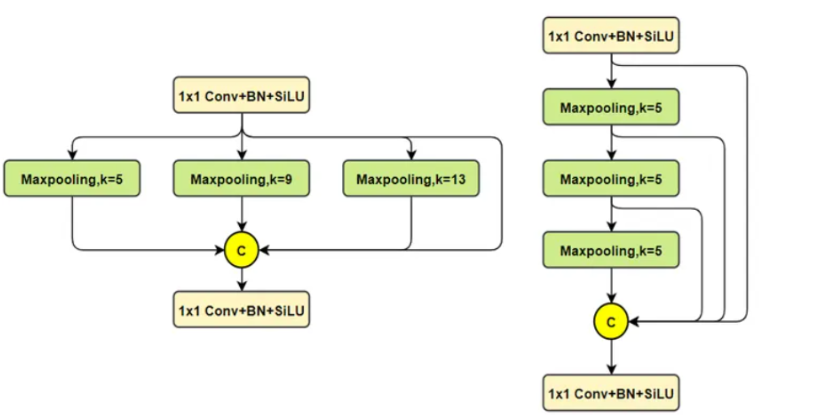

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

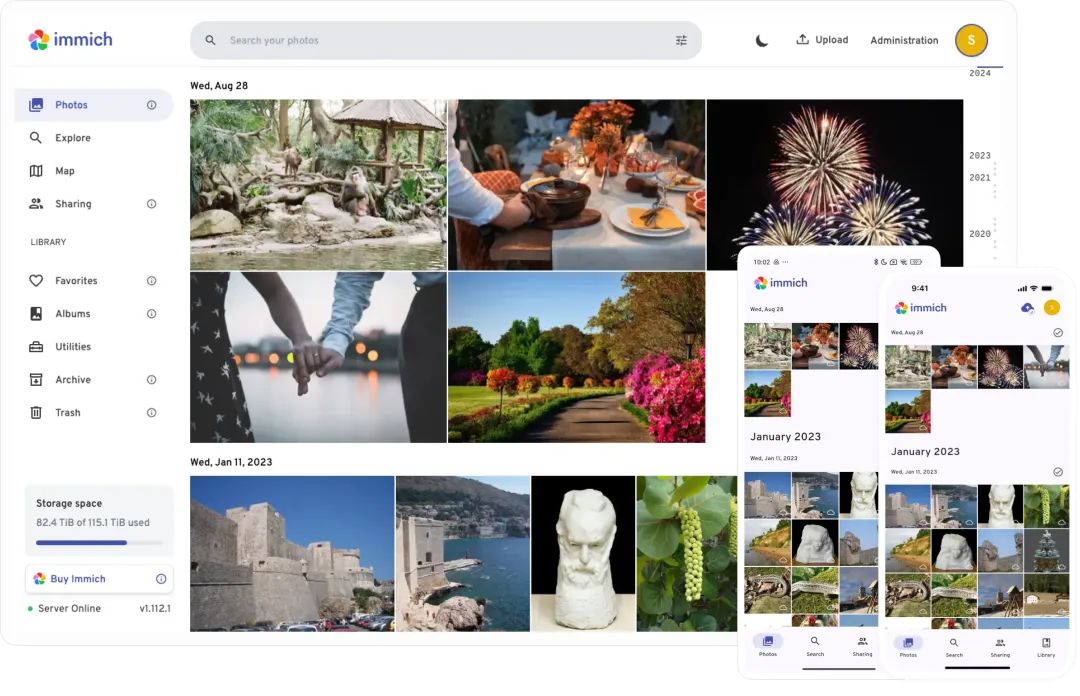

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

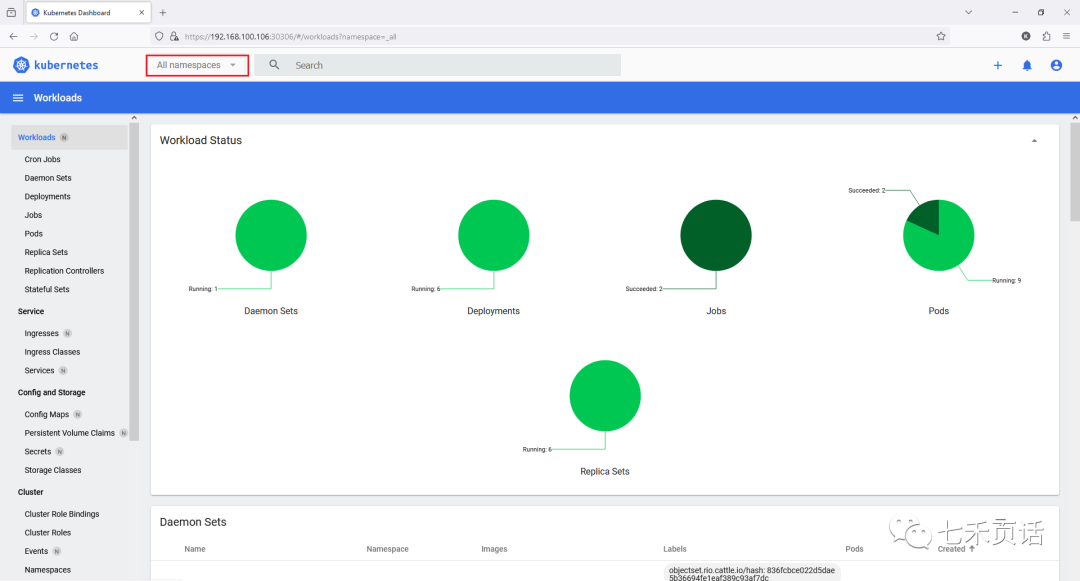

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

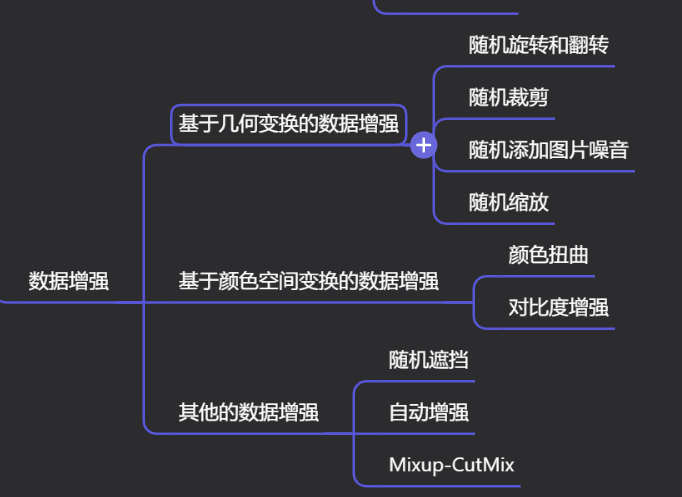

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

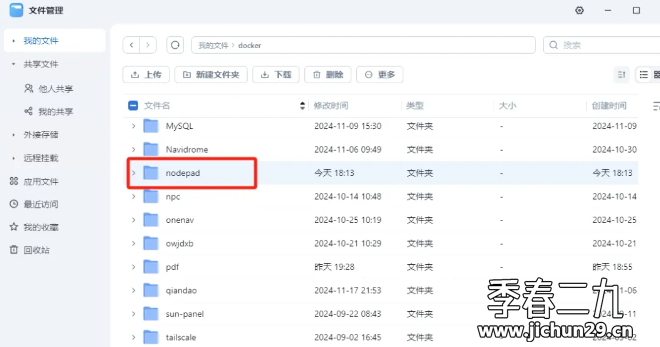

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

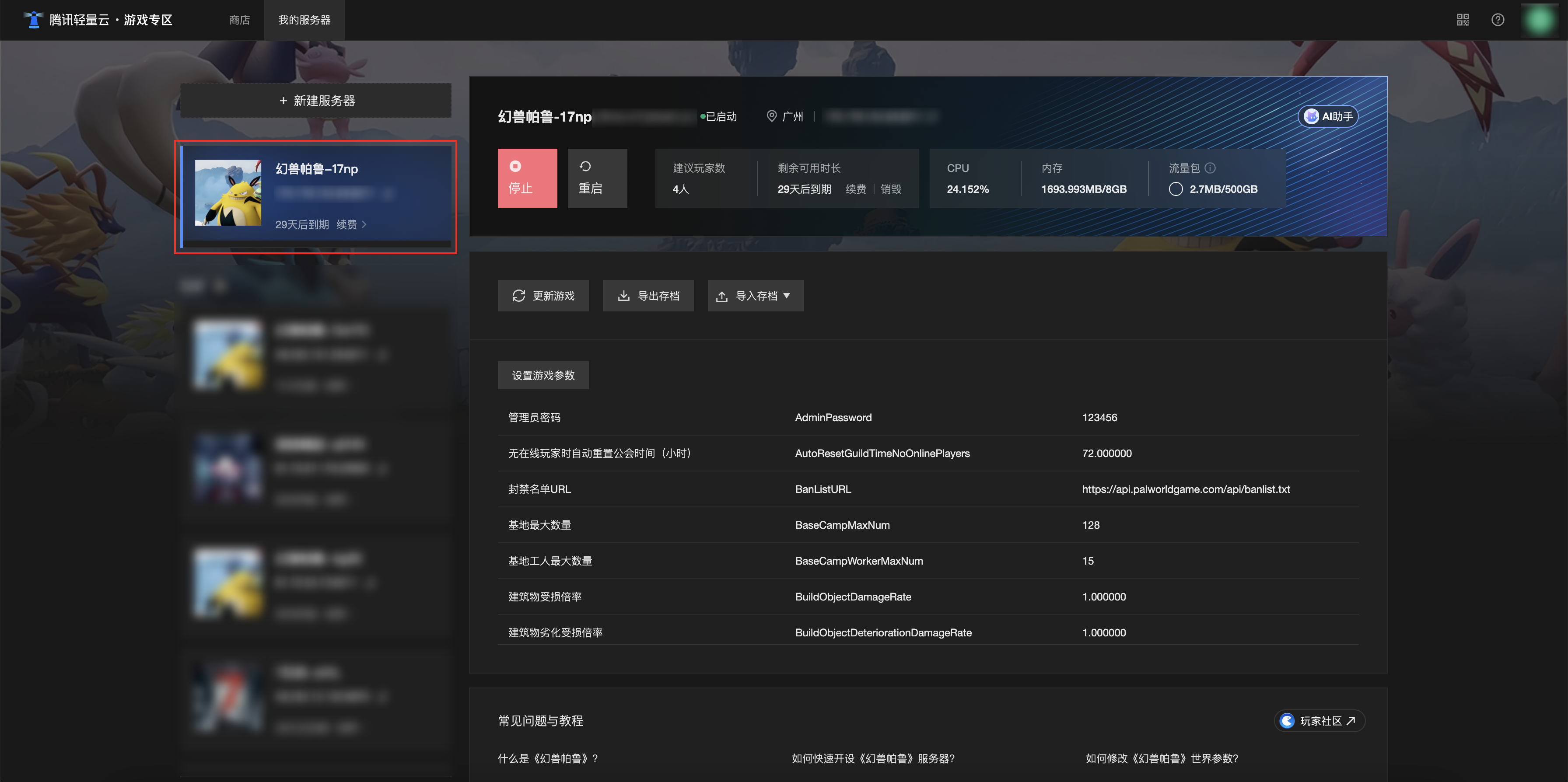

[Зона легкого облачного игрового сервера] Управление игровыми архивами