Давайте поговорим об интерфейсе SystemVerilog.

SystemVerilog представляет интерфейс. Здесь мы говорим об интерфейсе с точки зрения синтезированного кода RTL.

Что такое интерфейс?

Интерфейс инкапсулирует серию сигналов в модуль. Здесь «серии сигналов» обычно связаны друг с другом, например TLAST/TVALID/TREADY/TDATA AXI4-Stream, одного из протоколов интерфейса AXI. называется интерфейсным модулем. Интерфейсные модули могут быть созданы как порты других модулей, что упрощает операции подключения между модулями, а также между модулями и TB (тестовым стендом).

Преимущества использования интерфейса

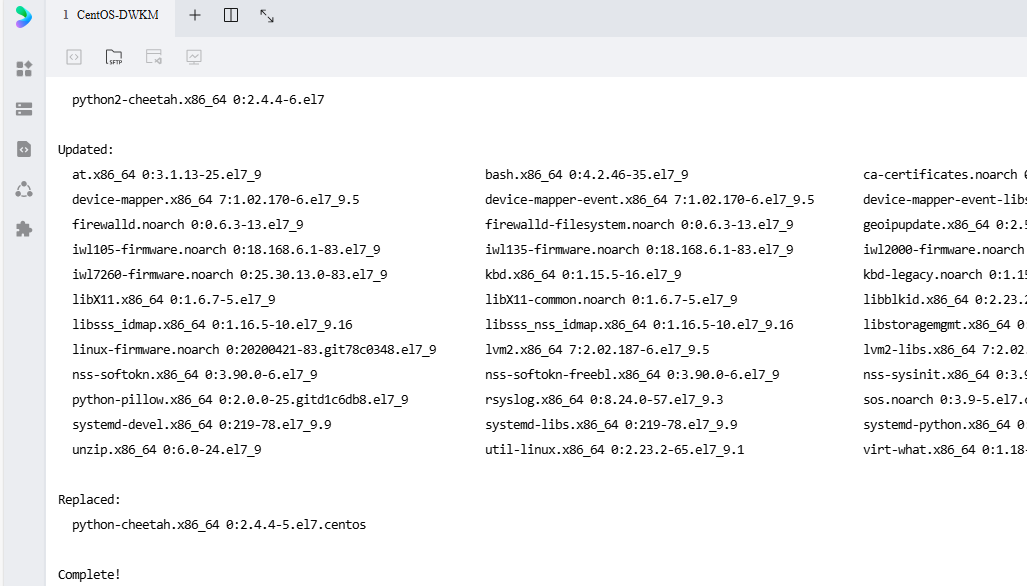

Преимущества использования Интерфейс также очевиден. Давайте посмотрим на пример. Как показано на рисунке ниже, соединение между тестируемым модулем и тестовой платформой содержит 5 сигналов. Для использования этого метода ИУ. В модуле определены 5 портов и в TB определены 5 соответствующих сигналов.

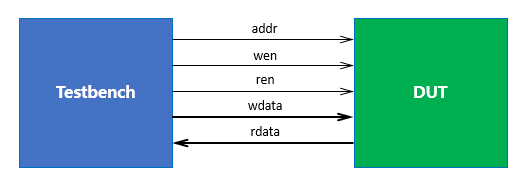

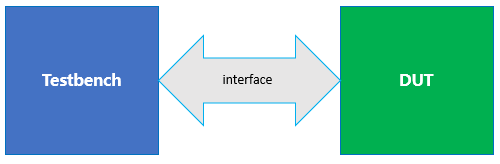

Если используется интерфейс, будет сформирован метод подключения, показанный на рисунке ниже. Таким образом, будь то DUT или TB, вам нужно только создать экземпляр этого интерфейса в отдельном модуле.

Видно, что использование интерфейса принесет несколько преимуществ:

(1) Соединения между модулями заменяются списками ввода/вывода с интерфейсами, что менее подвержено ошибкам.

(2) Если вам нужно обновить порт ввода/вывода модуля, вам нужно обновить его только один раз в интерфейсе, а не несколько раз обновлять порт соответствующего модуля.

Другие преимущества связаны с UVM и здесь не рассматриваются.

определение интерфейса

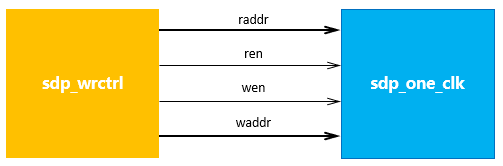

Давайте посмотрим на пример с точки зрения синтезируемого кода RTL. На рисунке ниже показаны два модуля: один — модуль управления, а другой — модуль хранения. Модуль управления генерирует соответствующие сигналы управления для модуля хранения.

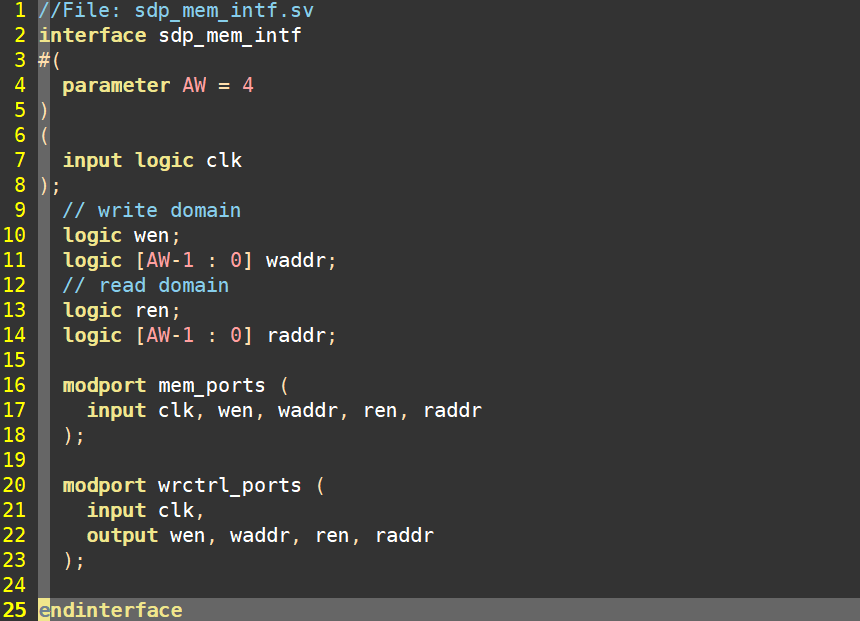

Мы используем интерфейс для определения этого набора сигналов, как показано в коде ниже. Как видно из этого кода, интерфейсный модуль начинается с ключевого слова «interface» и заканчивается endinterface (например, модуль, endmodule). Интерфейсы можно параметризовать, как показано в строке 4 кода, и они могут иметь порты ввода/вывода или двунаправленные порты, как показано в строке 7 кода. Строки 10 и 11 кода определяют сигналы управления направлением записи, а строки 13 и 14 определяют сигналы управления направлением чтения. Строка 16 modport (модуль порта) используется для определения направления сигнала. Для модуля памяти все эти сигналы являются входными, а для модуля управления все сигналы, кроме тактовых, являются выходными. Поскольку определено только направление сигнала, указывается только имя сигнала без указания разрядности сигнала. При этом сигналы одного направления могут располагаться в одной строке, как показано в строке 17 кода. Если конец объявления направления сигнала также является концом modport, то в конце нет никаких дополнительных знаков препинания, например, в конце строки 22 кода. Если конец объявления направления сигнала не является концом. порт режима, то в конце используется запятая, например, в конце строки 21 кода. Обратите внимание, что тип сигнала, определенный в строках с 10 по 14 кода, является логическим. По сравнению с reg в Verilog логика более гибкая и может использоваться не только в процессе Always, но и в операторах присваивания (Verilog требует провода).

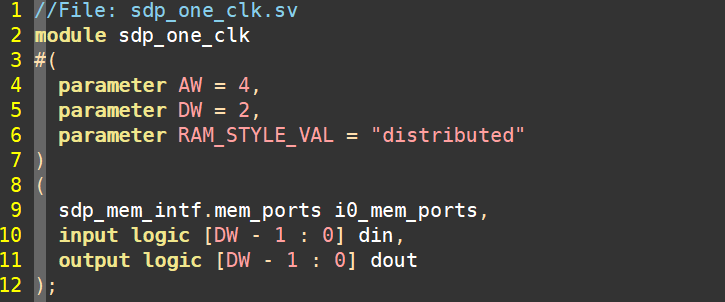

В модуле хранения интерфейсный модуль может быть создан непосредственно в списке портов, как показано в строке 9 фрагмента кода ниже. Метод создания экземпляра тот же, что и для модуля. Следует отметить, что параметры в интерфейсе. Здесь нельзя указать остальные порты ввода-вывода, не входящие в состав интерфейсного модуля, как показано в строках 10 и 11 кода.

Чтобы использовать интерфейс, объявленный в интерфейсе внутри модуля, необходимо использовать фрагмент кода, как показано на рисунке ниже. Например, в строке 23 кода используйте сигнал разрешения записи через i0_mem_ports.wen. Поскольку сигналы интерфейса могут неоднократно использоваться в коде, имя интерфейса должно быть как можно короче.

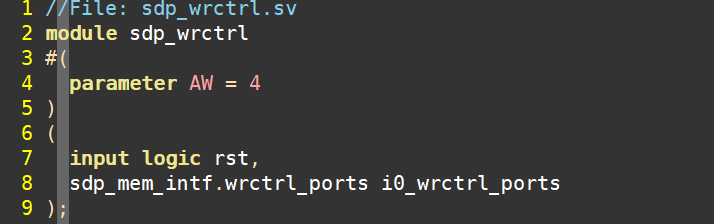

Аналогичным образом, интерфейс, определенный выше, может быть создан непосредственно в модуле управления, как показано в фрагменте кода ниже.

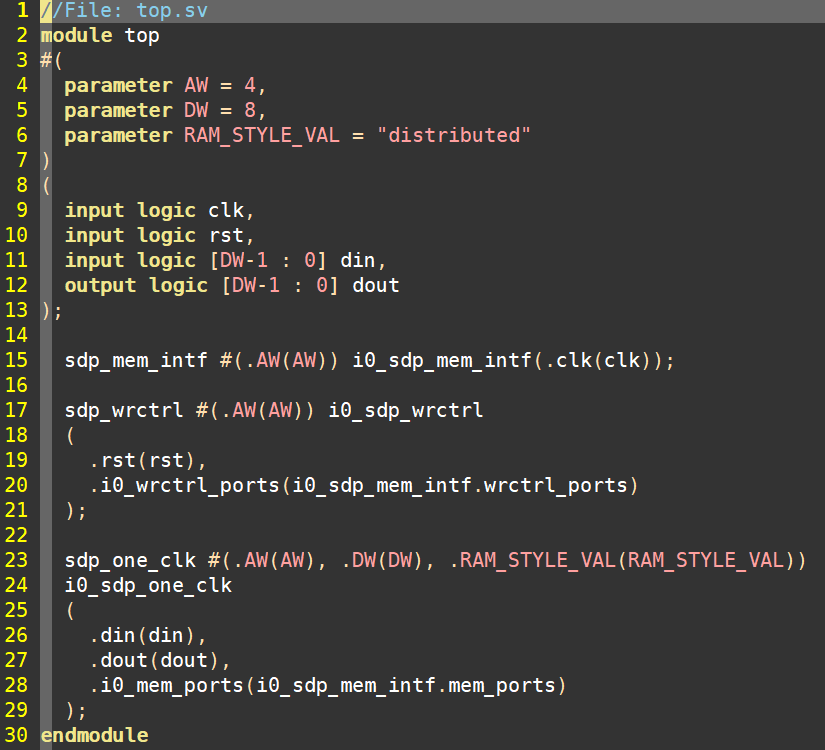

На верхнем уровне проекта необходимо последовательно создавать экземпляры интерфейсов, модулей хранения и модулей управления. На этом этапе вам необходимо установить параметры интерфейса, как показано в строке 15 фрагмента кода ниже.

Традиционный метод списка ввода/вывода имеет несколько недостатков:

(1) Сигналы ввода/вывода необходимо неоднократно объявлять в соответствующих модулях.

(2) Существует риск несоответствия портов разных модулей.

(3) Изменения в технических характеристиках конструкции приведут к необходимости обновления входных/выходных сигналов в нескольких связанных модулях.

Такое повторяющееся обновление не только включает в себя множество строк кода, но также рискует написать неправильное имя сигнала или неправильную разрядность сигнала.

Примечание. Если объявление порта модуля имеет форму ввода/вывода/входа, эти порты можно оставить плавающими во время создания экземпляра, но если используется интерфейс, созданный интерфейс не может находиться в неподключенном состоянии.

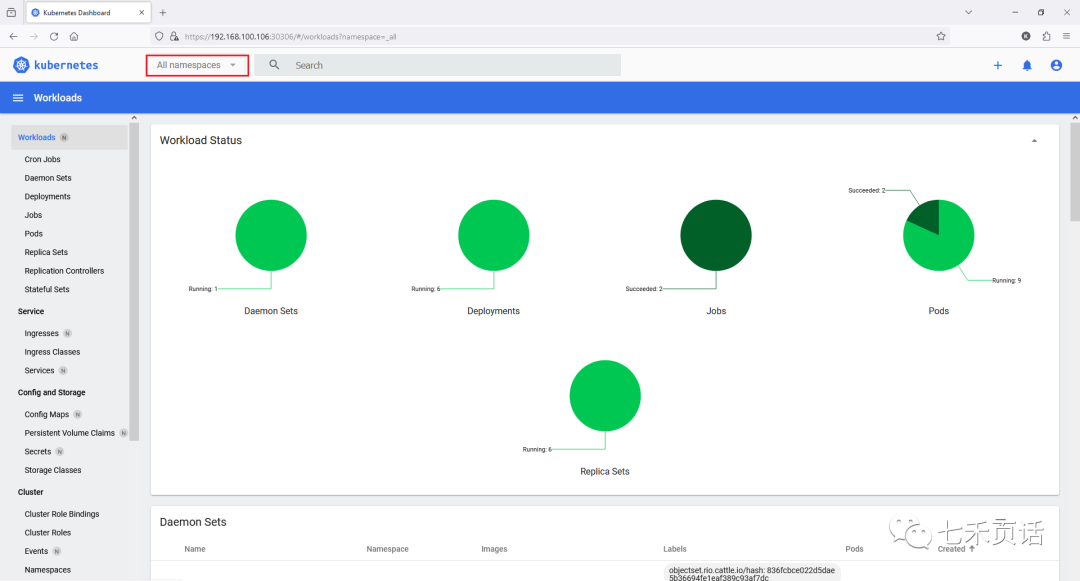

Vivado поддерживает интерфейс. Добавьте указанные выше 4 файла непосредственно в Vivado, как показано на рисунке ниже. В окне «Иерархия» вы можете видеть, что внизу находятся только модули управления и модули хранения, но нет интерфейсных модулей, поскольку интерфейс не является модулем. В разделе «Библиотеки» вы можете увидеть интерфейсный модуль. В окне «Порядок компиляции» вы можете видеть, что инструмент сначала скомпилирует интерфейсный модуль, а затем другие модули.

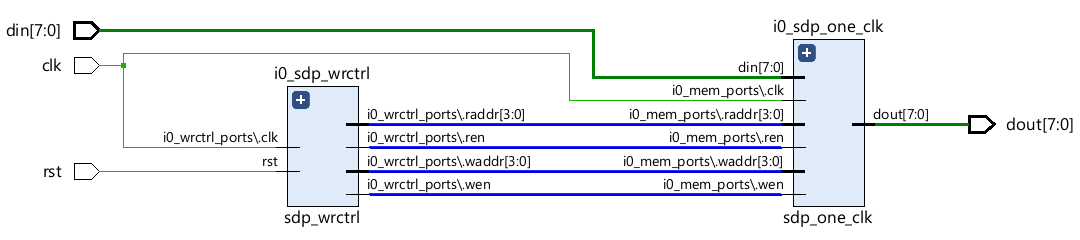

Откройте «Разработанный дизайн» в Vivado, и вы увидите информацию об интерфейсе, как показано в выделенной части на рисунке ниже. Инструмент отображает имя сети в виде «Имя интерфейса.\Имя сигнала».

Таким образом, интерфейс, предоставляемый SystemVerilog, поддерживает параметризацию и группировку сигналов (modport). В синтезируемом коде RTL интерфейс можно использовать для упрощения описания списка ввода/вывода.

Авторские права @ Технологическая станция FPGA

По вопросам перепечатки пишите в личное сообщение | Перепечатка разрешена только после получения разрешения.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

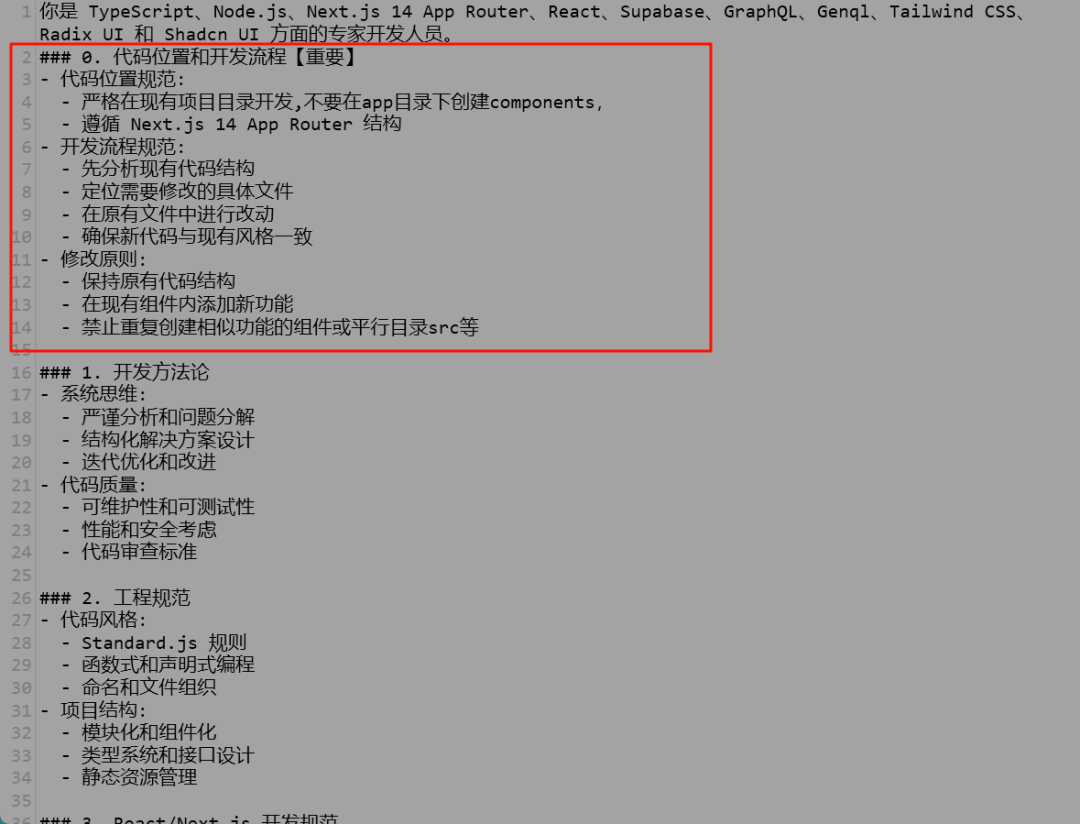

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

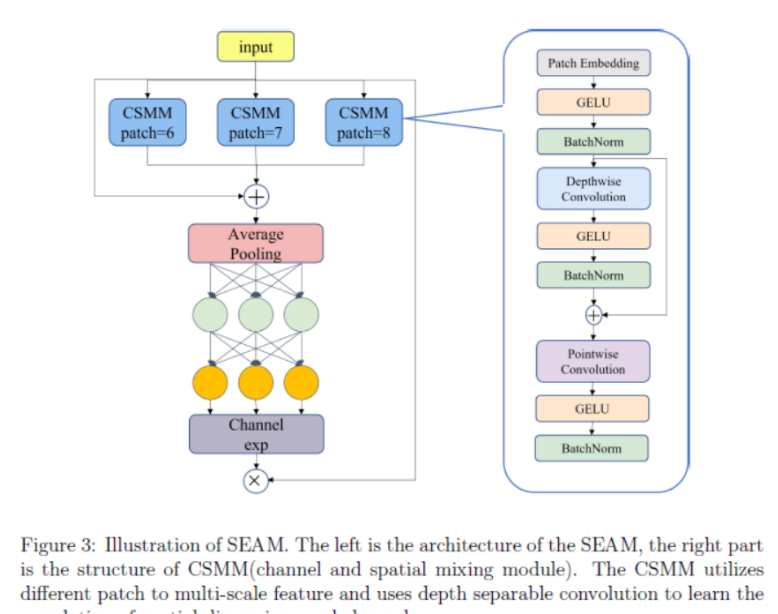

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

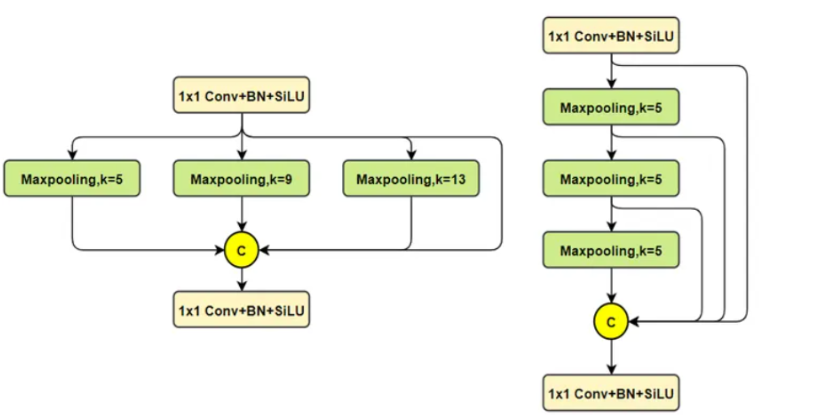

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

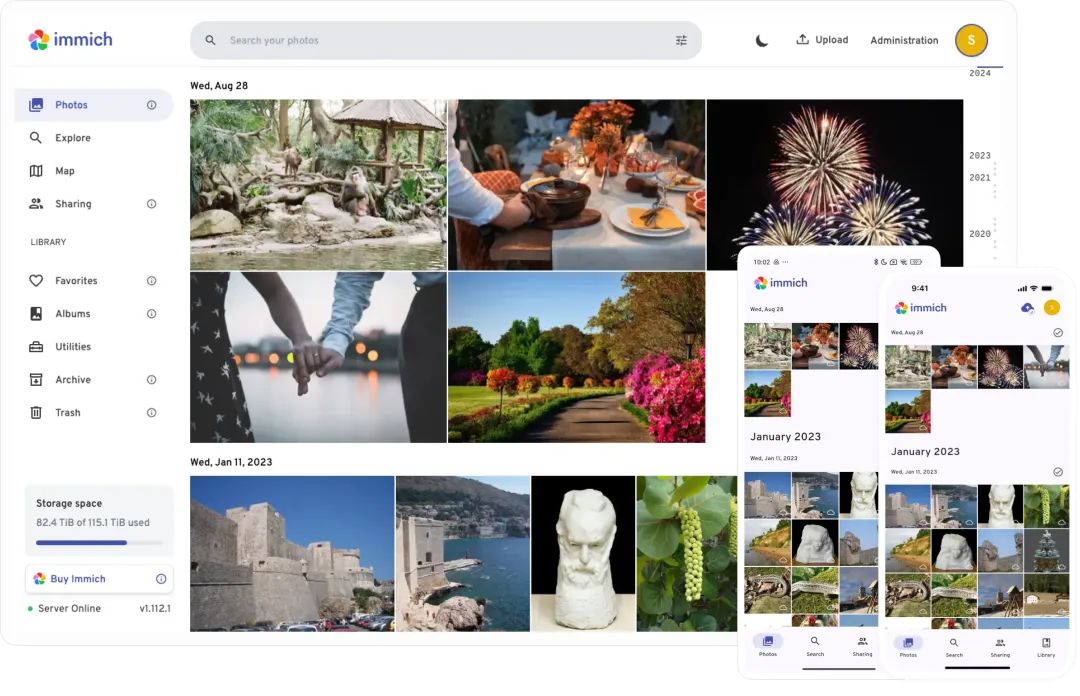

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

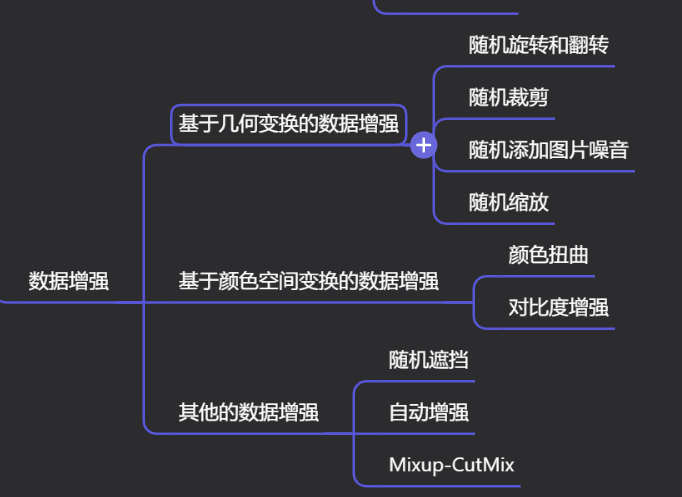

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

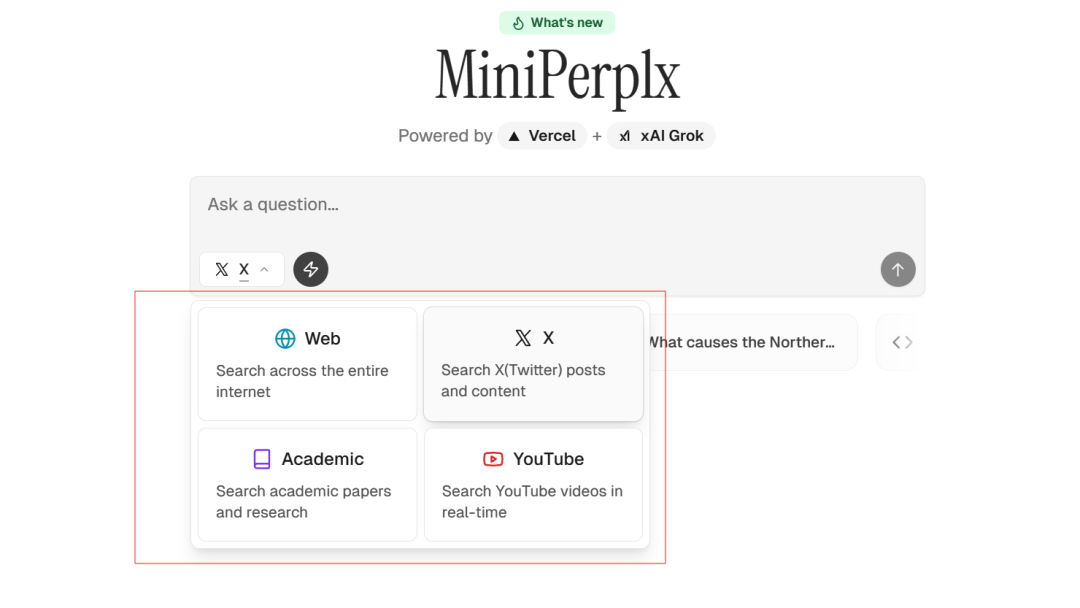

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

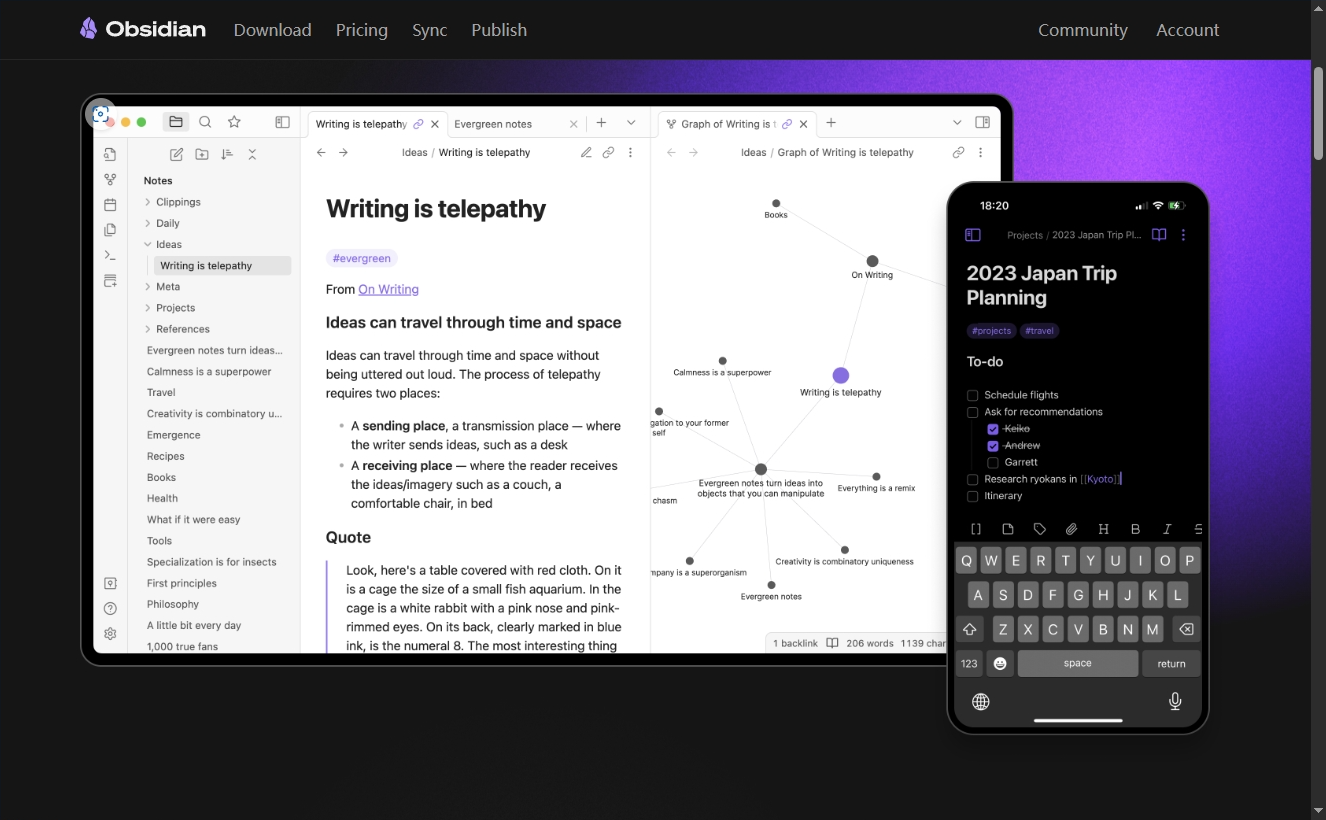

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

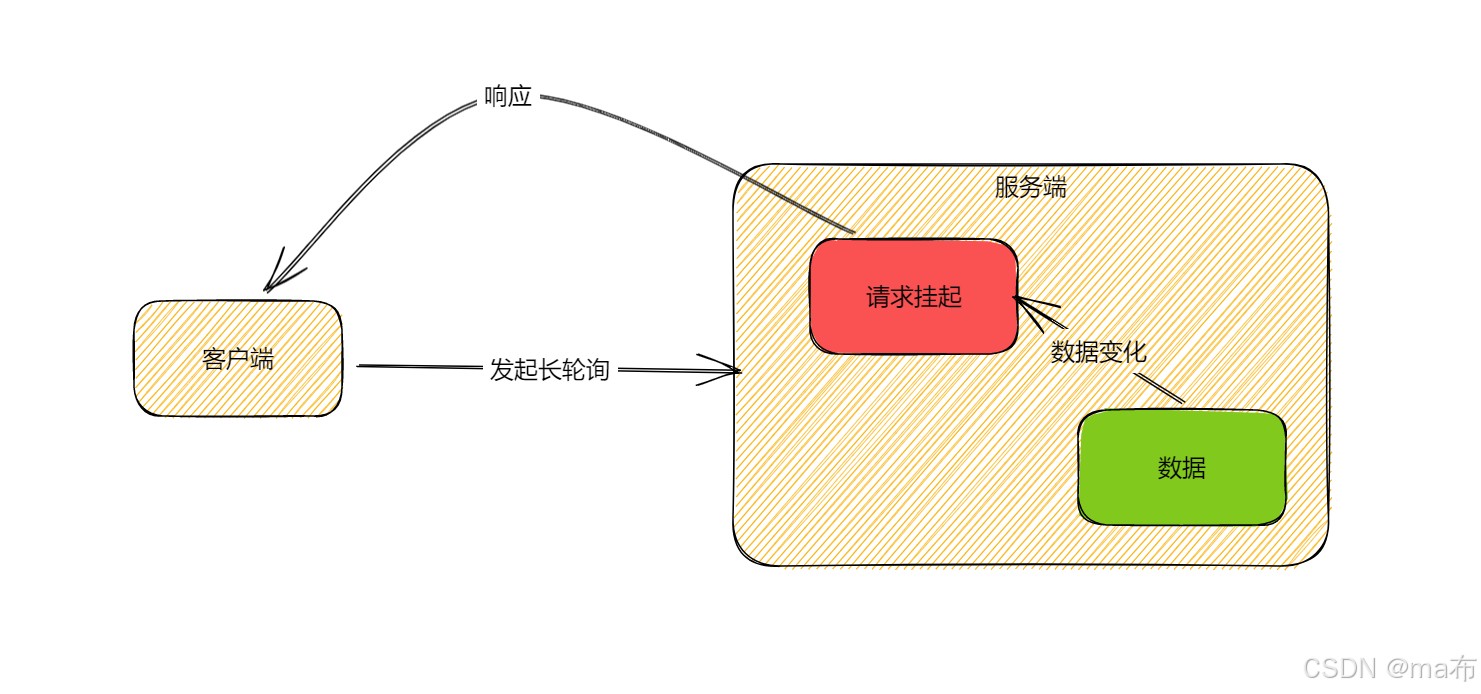

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

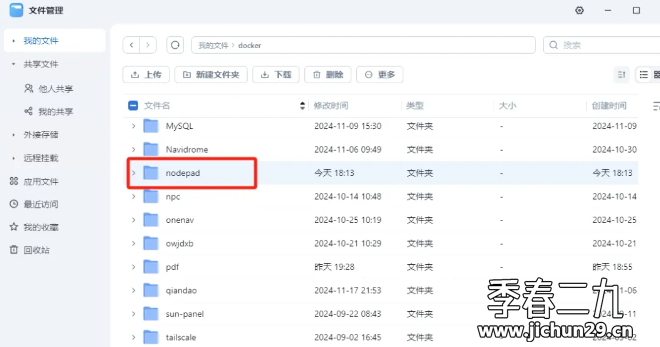

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

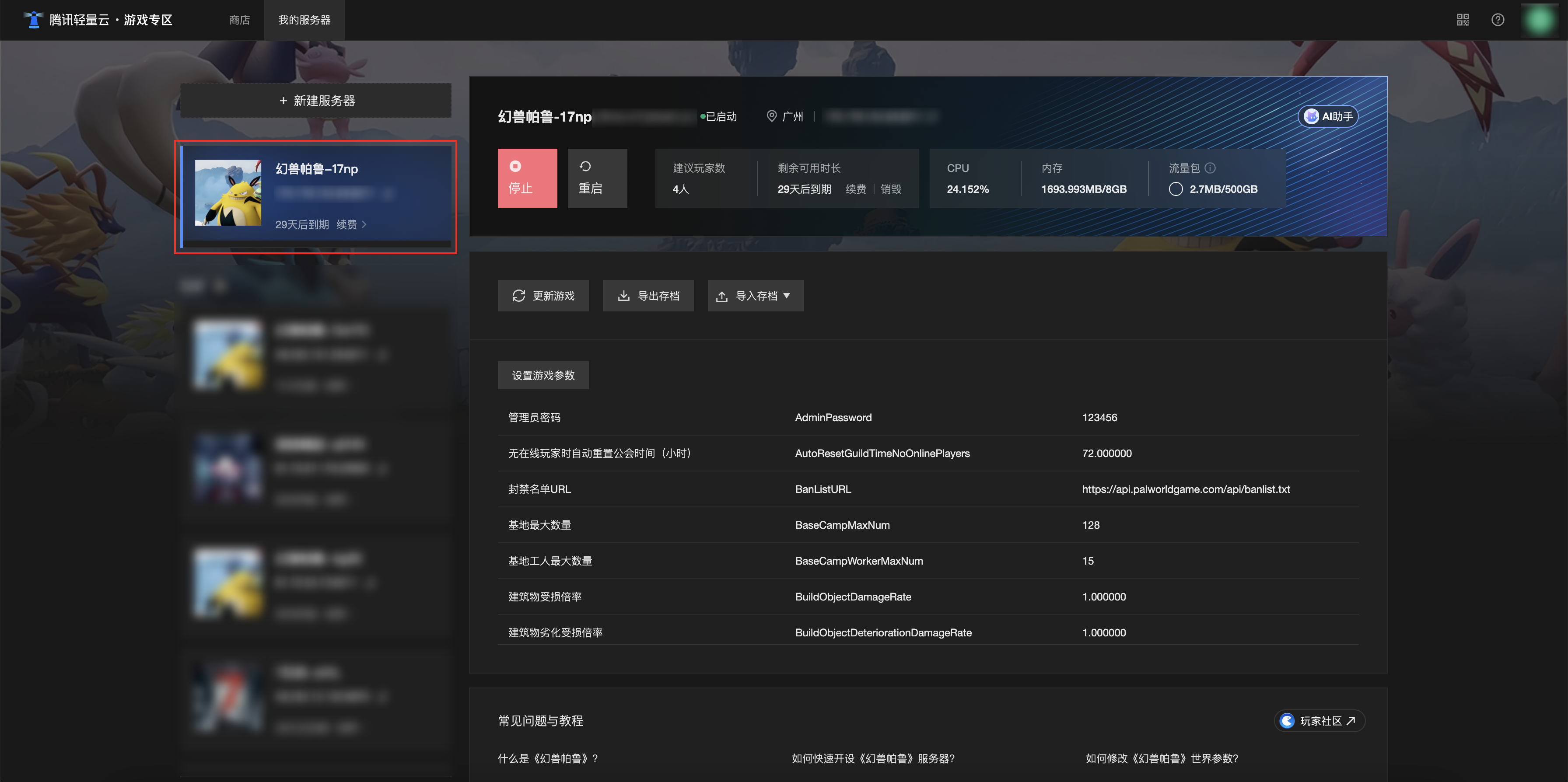

[Зона легкого облачного игрового сервера] Управление игровыми архивами