Базовый процесс моделирования программного обеспечения Quartus ii (с использованием VHDL) «Рекомендуемый набор»

Статья впервые появилась на моемЛичный блог

Это первое руководство из серии руководств по VHDL. Так называемые учебные пособия на самом деле представляют собой заметки, в которых фиксируются проблемы и содержание обучения, с которыми я столкнулся в процессе обучения. Я делюсь ими здесь для справки другим новичкам. Если в блоге есть какие-либо ошибки или неточности, вы можете оставить их в блоге. Область комментариев ниже. Отметьте это, ваши отзывы — самая большая помощь для меня, большое спасибо.

В этом блоге в основном рассказывается об использованиииспользоватьQuartus Шаги по моделированию с помощью программного обеспечения ii подробно описаны, но несколько излишни (не большая проблема), поскольку это первая статья. Последующие руководства должны быть посвящены самому языку VHDL и Quartus. iiнекоторые изиспользовать Навык。

В этом руководстве рассматривается реализация D-триггеров в VHDL с использованием процесса моделирования Quartus ii.

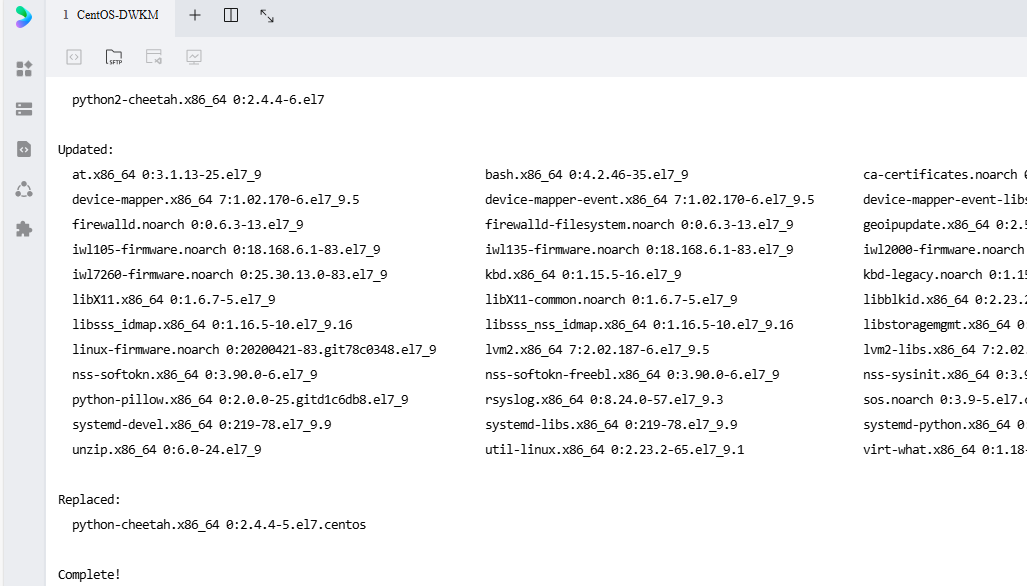

Сначала откройте программу моделирования Quartus ii и создайте новый проект.

Нажмите «Далее»;

Все три имени должны быть одинаковыми;

Имя файла такое же, как и на предыдущем шаге;

Здесь вам нужно выбрать соответствующее аппаратное устройство для компиляции. Но если вы не используете аппаратное моделирование FPGA, вы можете использовать его по умолчанию.,Другая сторона на самом деле не имеет большого влияния.,Но если в школе есть плата FPGA, постарайтесь выбрать модель, соответствующую плате;

После завершения нового проекта создайте файл VHDL;

Если вновь созданный VHDL не сохранен, вы можете сохранить его как в файле;

Имя файла VHDL совпадает с именем проекта;

Запишите код реализации D-триггера во вновь созданный файл VHDL (код здесь не поясняется), а затем щелкните маленький треугольник, чтобы выбрать компиляцию;

-- D trigger achievement

library ieee;

use ieee.std_logic_1164.all;

ENTITY Dtrigger IS PORT(

D, clk : IN STD_LOGIC;

Q : OUT STD_LOGIC

);

END ENTITY Dtrigger;

ARCHITECTURE one of Dtrigger is

SIGNAL sig_save : STD_LOGIC;

BEGIN

PROCESS(clk)

BEGIN

if clk'event and clk='1' then

-- == rising_edge(clk) then

sig_save <= D;

end if;

END PROCESS;

Q <= sig_save;

END ARCHITECTURE one;

Создайте новый файл моделирования формы волны;

После создания нового файла моделирования формы сигнала,существоватьEditВыбиратьEnd TimeУстановите время окончания моделирования,По умолчанию – 1 мкс.,Времени немного мало,Сделайте его больше;

Здесь я установил значение 51us;

могу сделатьиспользоватьCtrl + масштабирование колеса прокрутки。Затем дважды щелкнитеNameРегиональные переменные импорта;

Нажатие кнопки списка отобразит все переменные, определенные Entity, а затем импортирует их все;

Затем нарисуйте сигнал синхронизации clk и сигнал входной переменной D в файле сигналов.,существоватьрисованиекогда Мой опытвыбиратьнижний левый уголGrid,Это легче нарисовать;

существоватьProcessingвыпадающее менюSimulator ToolВыберите режим моделирования;

Выберите Timing (имитация последовательности); выберите Functional (функциональная симуляция);

Нажмите кнопку моделирования формы сигнала; конец моделирования можно увидеть на диаграмме моделирования.,когдаclkТактовый сигналнарастающий фронткогда,Выходной сигнал Q будет меняться по мере изменения входного сигнала D.,clkТактовый сигнал0когда,Сохраняйте исходное состояние;

выбиратьToolsв раскрывающемся менюNetlist Viewers–>RTL ViewerМожно просмотретьVHDLОписанная аппаратная схема。(на самом делесуществоватьVHDLПосле компиляции Можно просмотреть)

Аппаратная схема показана на рисунке ниже.

Хорошо, это все содержание этого руководства. Следующие руководства будут охватывать сам язык VHDL и Quartus. iiпосланникиспользовать Навык Понятно。

End.

Заявление об авторских правах: Содержание этой статьи добровольно предоставлено пользователями Интернета.,Мнения, выраженные в данной статье, принадлежат исключительно автору. Этот сайт предоставляет только услуги по хранению информации.,нет собственности,Никакая соответствующая юридическая ответственность не предполагается. Если вы обнаружите на этом сайте какое-либо подозрительное нарушение авторских прав/незаконный контент,, Пожалуйста, отправьте электронное письмо на Сообщите, после проверки этот сайт будет немедленно удален.

Издатель: Лидер стека программистов полного стека, укажите источник для перепечатки: https://javaforall.cn/181678.html Исходная ссылка: https://javaforall.cn

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

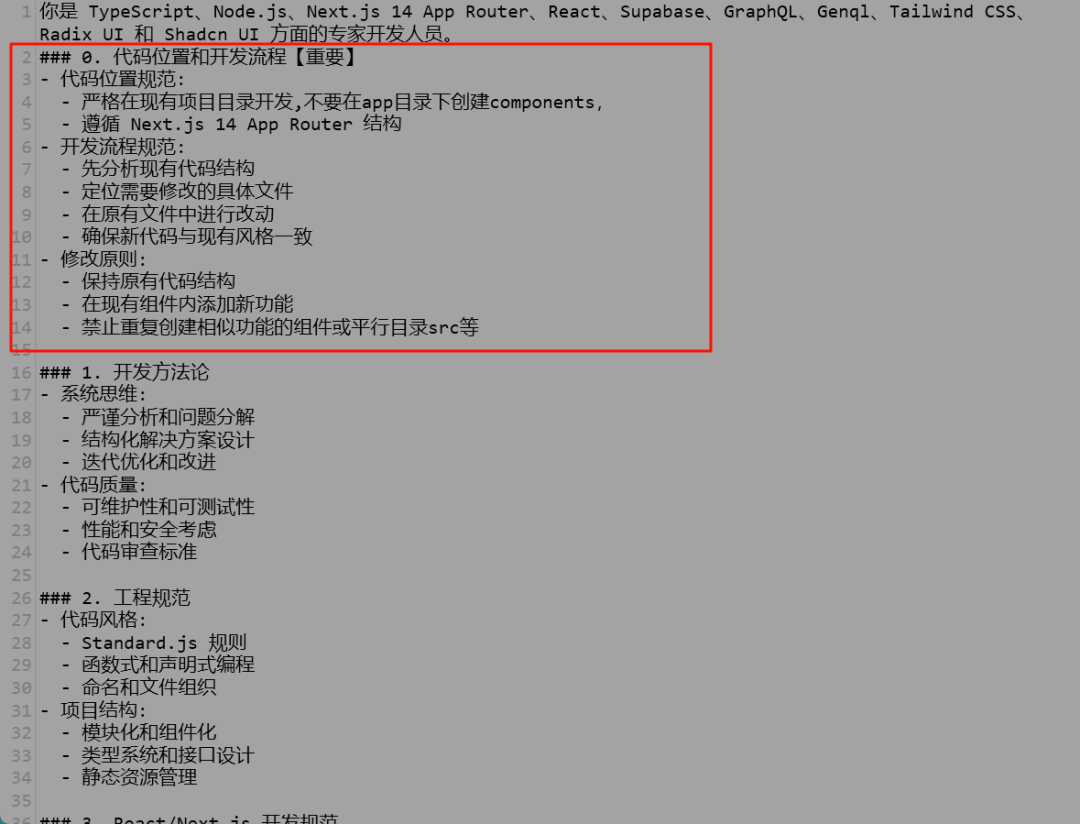

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

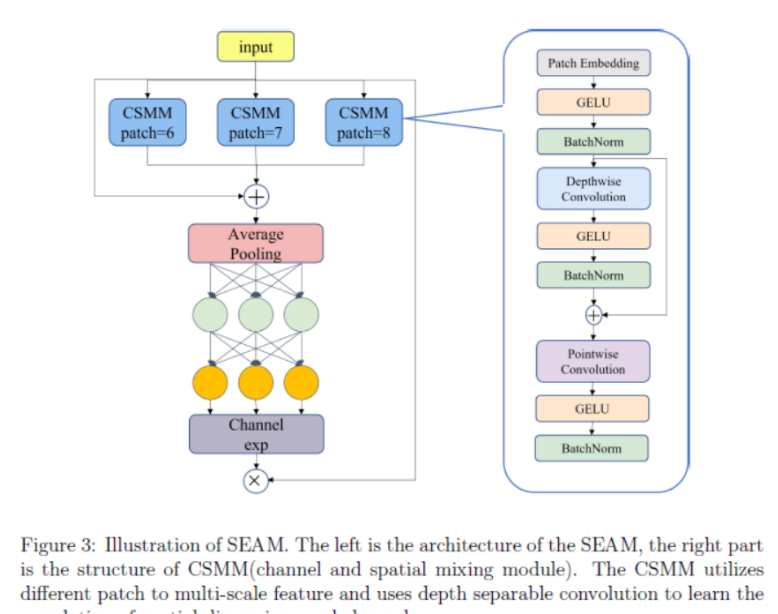

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

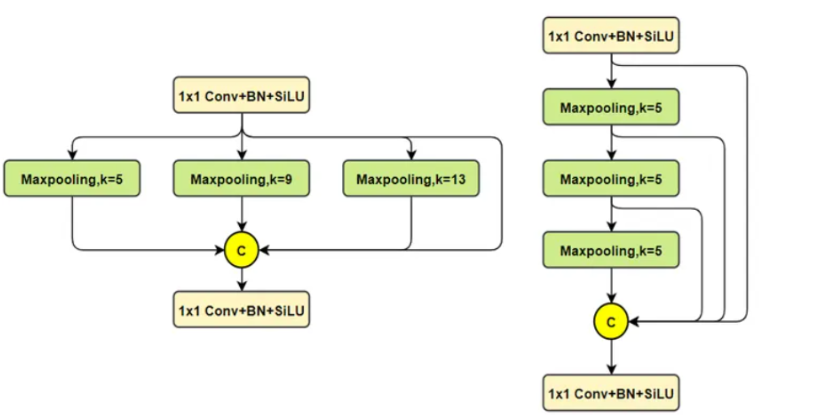

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

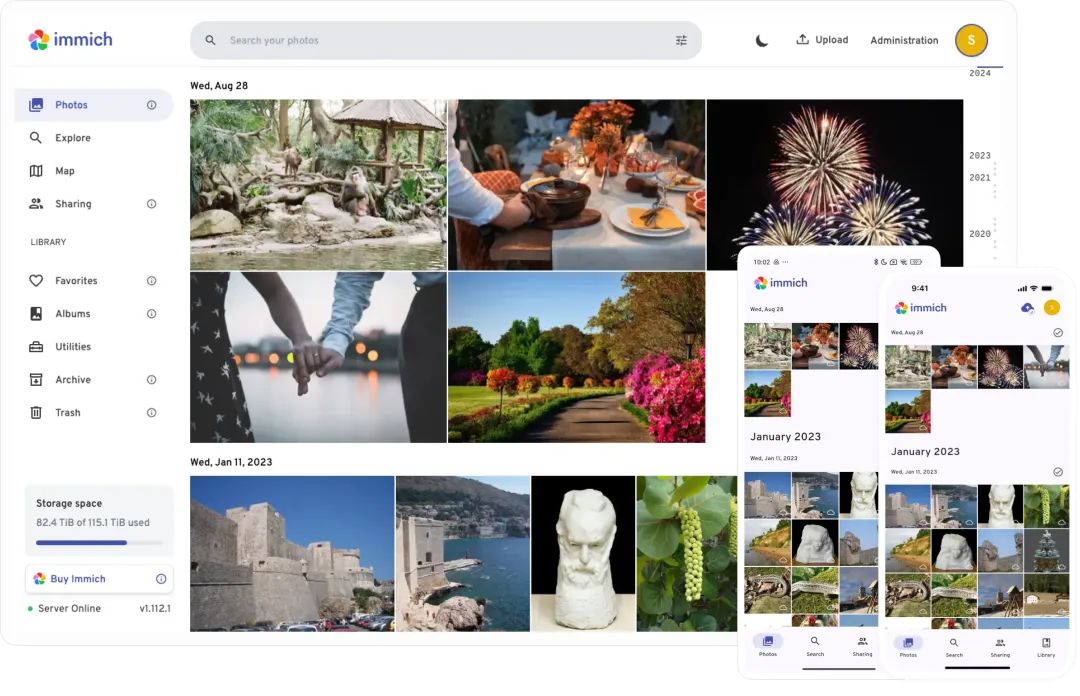

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

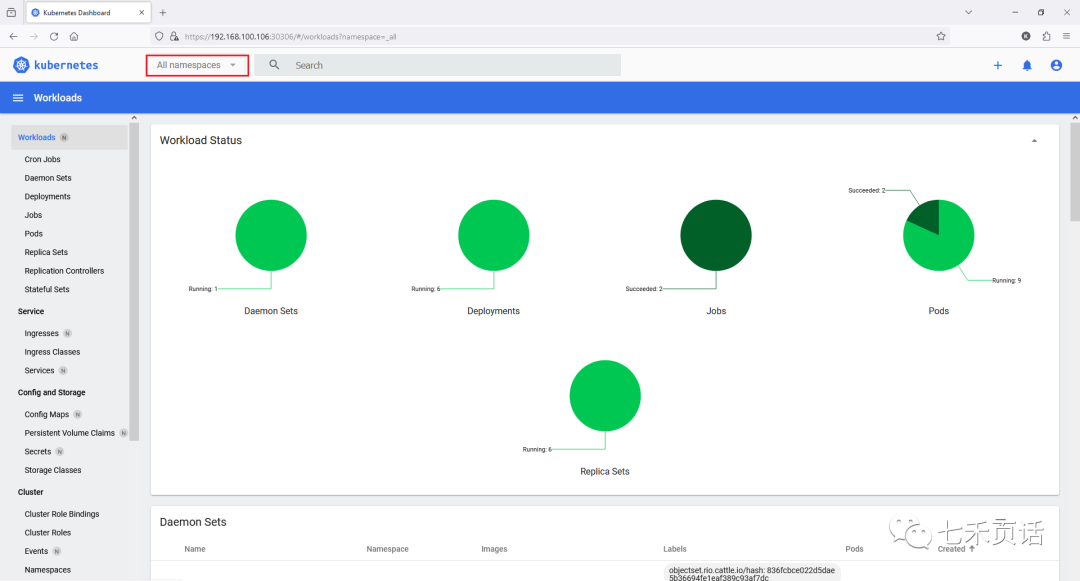

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

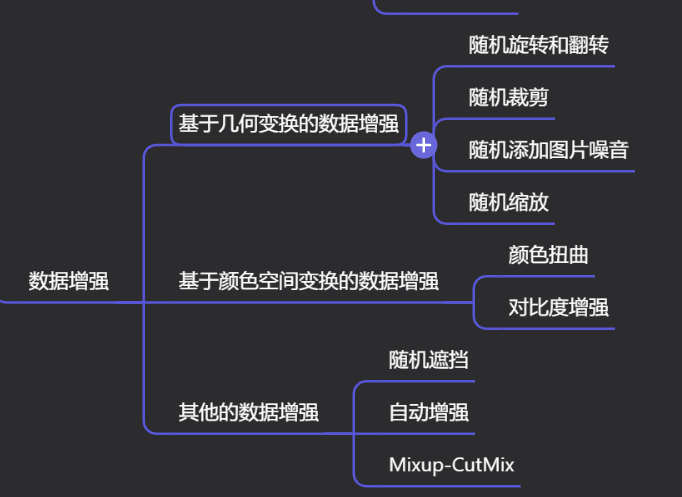

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

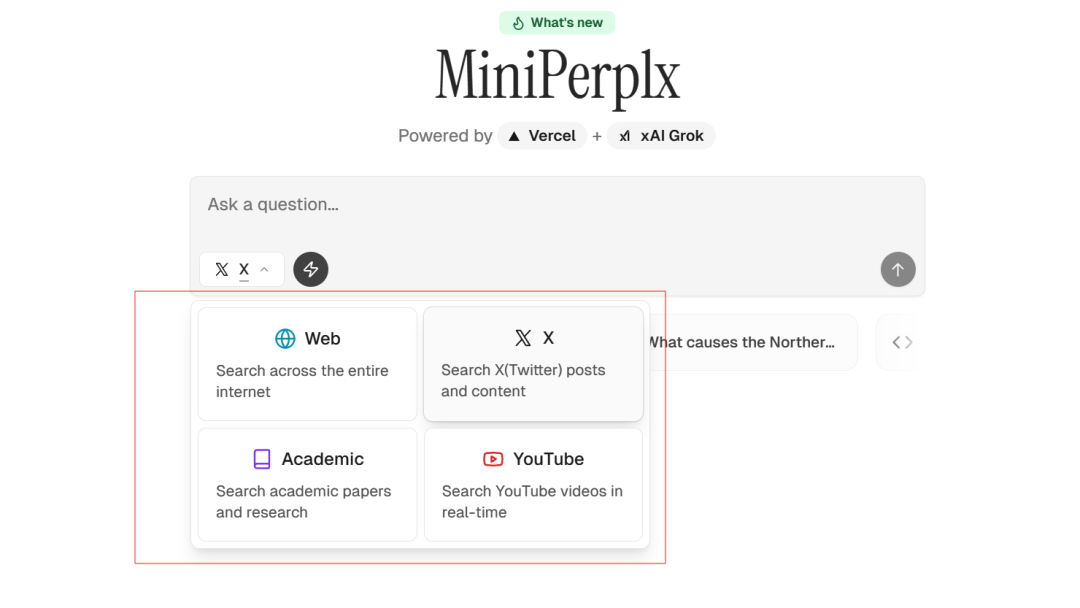

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

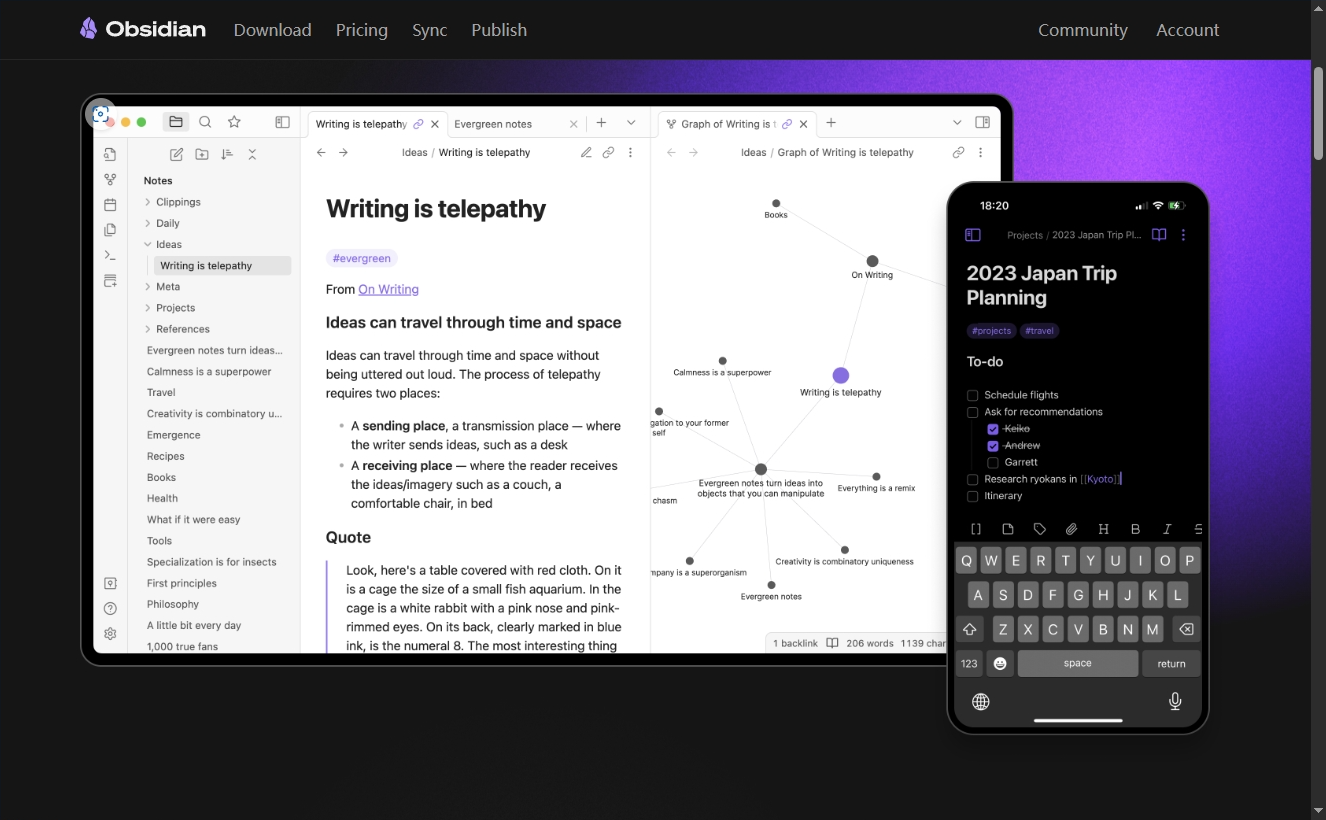

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

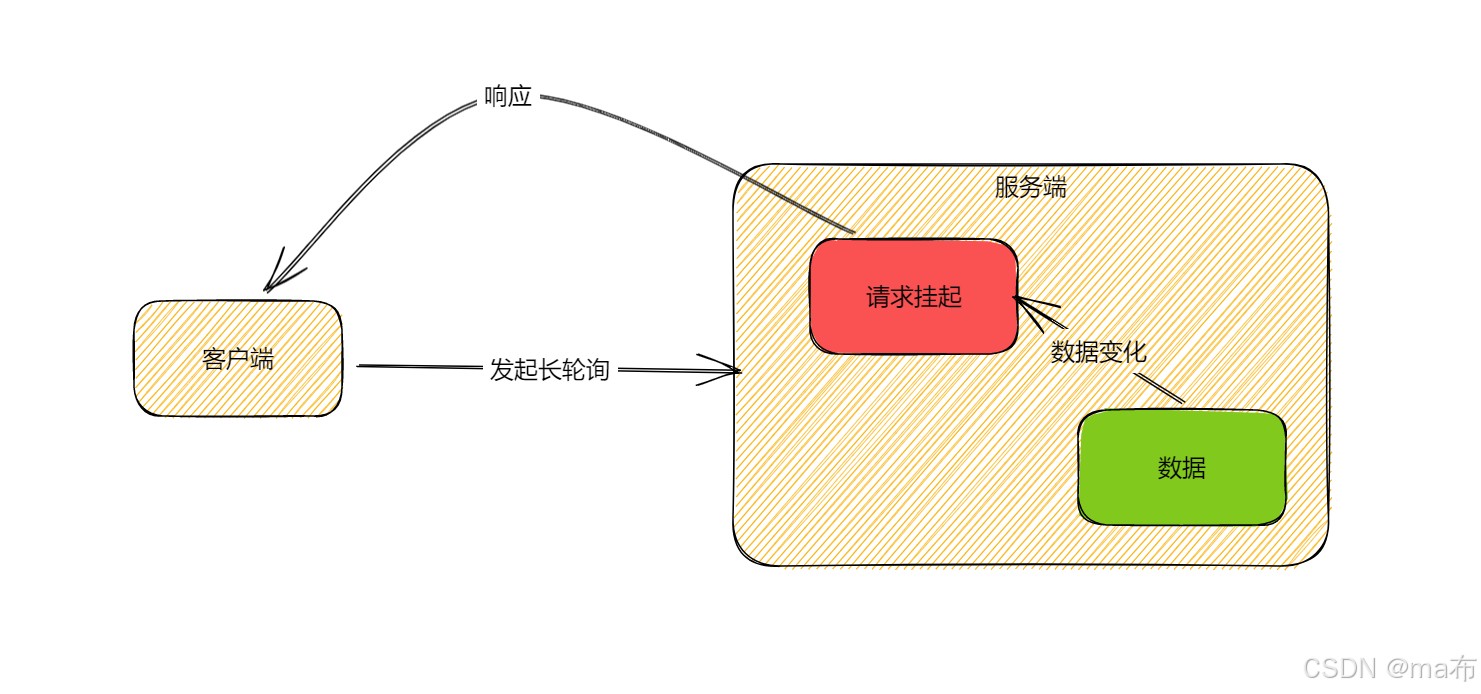

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

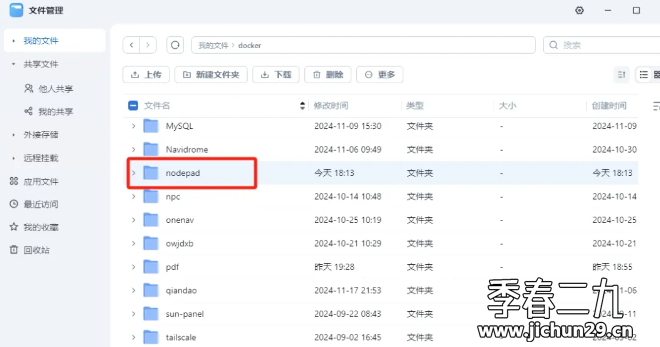

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

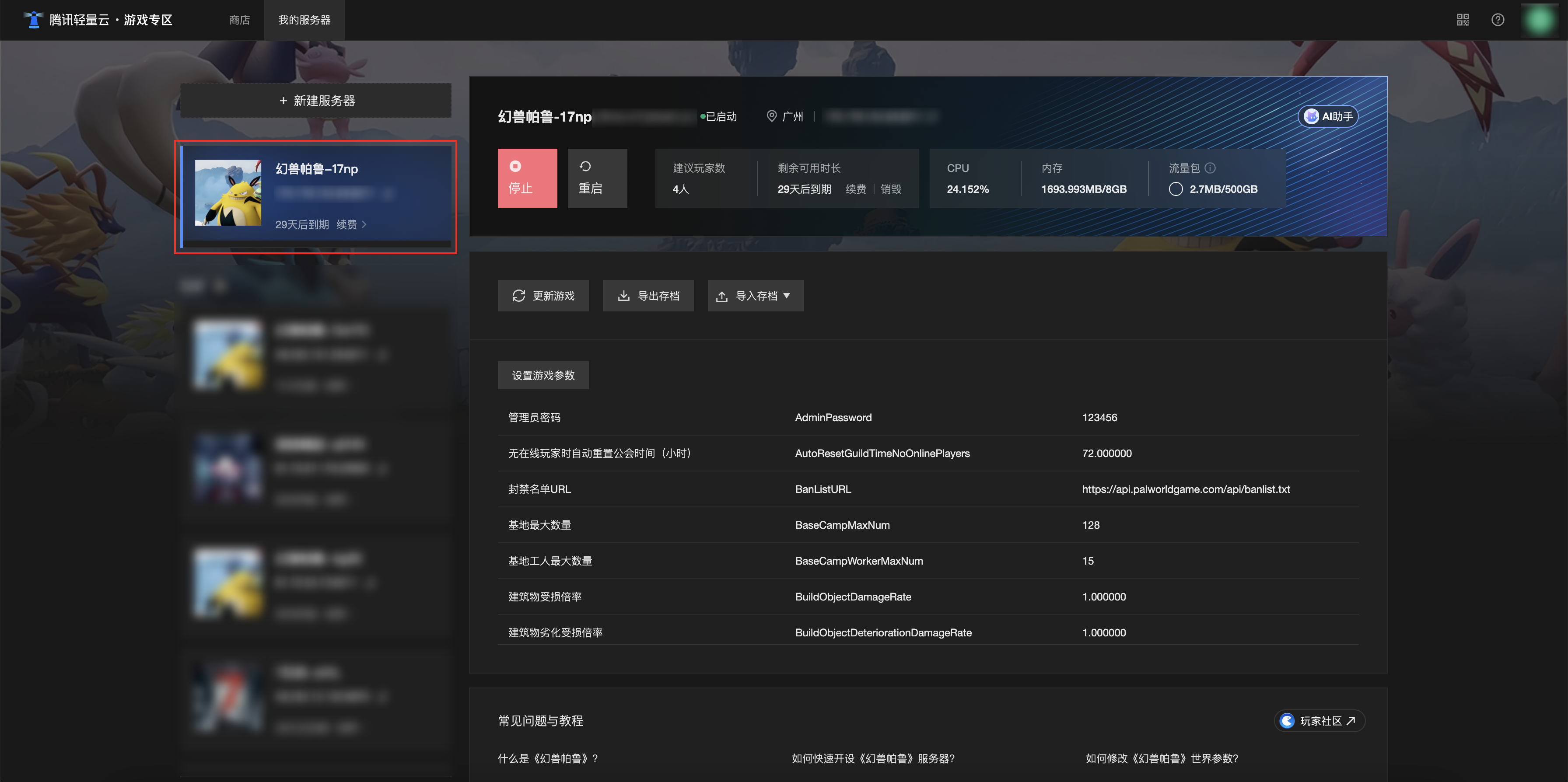

[Зона легкого облачного игрового сервера] Управление игровыми архивами